一.简介

RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接。

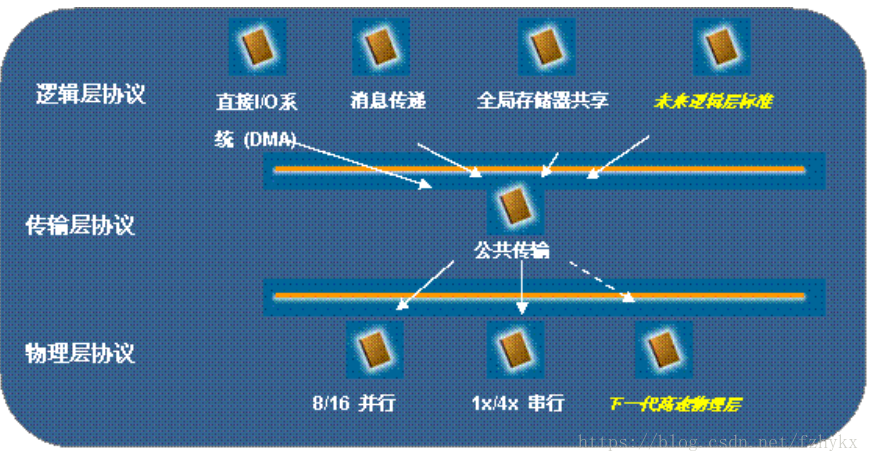

RapidIO协议由逻辑层、传输层和物理层构成。逻辑层定义了所有协议和包格式。这是对终端进行初始化和完成传送的很有必要的信息。传输层为数据包从一个终端到另一个终端通道的必要信息。物理层描述了设备之间接口协议,例如包传装置,流量控制,电特性及低级错误管理等。Rapid IO分为并行Rapid IO标准和串行Rapid IO标准,串行RapidIO是指物理层采用串行差分模拟信号传输的RapidIO标准。

RapidIO行业协会成立于2000年,其宗旨是为嵌入式系统开发可靠的、 高性能、 基于包交换的互连技术,2001 年正式发表其基本的规范。2003 年10 月,国际标准组织(ISO)和国际电工委员会(IEC)一致通过了RapidIO互连规范,即ISO/IEC DIS 18372,这使RapidIO(ISO)成为嵌入式互连技术方面得到授权的唯一标准。RapidIO 的规范发布历史如下:

2001年3月,发布RapidIO 1.1规范;

2002年6月,发布RapidIO 1.2规范;

2005年2月,发布RapidIO 1.3规范;

2007年6月,发布RapidIO 2.0规范;

2009年8月,发布RapidIO 2.1规范;

2011年5月,发布RapidIO 2.2规范。

RapidIO 1.x标准支持的信号速率为1.25GHz、2.5GHz和3.125GHz;RapidIO 2.x标准在兼容Rapid IO 1.x标准基础上,增加了支持5GHz和6.25GHz的传输速率 。

RapidIO 已有超过10 年的历史,仍然生机勃勃,它还在继续为开发人员提供高速、先进的通讯技术:可对许多集成电路、板卡、背板及计算机系统供应商提供支持,支持RapidIO 标准的厂商有:Mercury Computer Systems、Freescale Semiconductor、Lucent-Alcatel、PMC-Sierra、Texas Instruments、Tundra Semiconductor、WindRiver、AMCC、Curtiss-Wright Controls、GE Fanuc 等,也就是说世界上几乎所有的嵌入式主流厂商都已经支持RapidIO 技术,显然,RapidIO 势在必行。发展至今,开发人员有100 多种基于RapidIO 的产品可供选择,这些产品涵盖了各种开发工具、嵌入式系统、IP、软件、测试与测量设备及半导体(ASIC、DSP、FPGA)等。

二.其他协议相比较

随着高性能嵌入式系统的不断发展,芯片间及板间互连对带宽、成本、灵活性及可靠性的要求越来越高,传统的互连方式,如处理器总线、PCI总线和以太网,都难以满足新的需求 。

处理器总线主要用作外部存储器接口,如德州仪器(TI) C6000系列DSP的外部存储器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持异步SRAM、FLASH等。外部存储器接口也可用作与板内FPGA或ASIC芯片互连,这种情况下,FPGA或ASIC模拟一个DSP支持的存储器接口,DSP则把FPGA或ASIC当作存储器来访问。这类同步接口带宽可达10Gbps,如德州仪器TMS320C6455 DSP的DDR2接口最大带宽为17.066Gbps,SBSRAM接口最大带宽为8.533Gbps。然而,这种接口也存在一些局限性:

1.接口管脚多,硬件设计困难。常见的DDR2接口有70~80个管脚;

2.只能用于板内互连,无法用于板间互连;

3.不是点对点的对等互连,DSP始终是主设备,其它器件只能做从设备。

PCI是广泛用于计算机内器件互连的技术。传统PCI技术也采样类似于上述存储器接口的并行总线方式,如TMS320C6455 DSP的PCI接口,有32bits数据总线,最高时钟速度为66MHz,共有42个管脚。最新的串行PCI Express技术采用与串行RapidIO(SRIO, Serial RapidIO)类似的物理层传输技术,使得带宽达到10Gbps左右。但由于其主要的应用仍是计算机,而且为了兼容传统PCI技术,使得它在嵌入式设备方面的应用具有一定的局限性,如不支持点对点对等通信等。

众所周知,以太网是使用最广泛的局域网互连技术,它也被扩展应用到嵌入式设备互连,但它的局限性也是显而易见的:

1.不支持硬件纠错,软件协议栈开销较大;

2.打包效率低,有效传输带宽因此而减小;

3.只支持消息传输模式,不支持对对端设备的直接存储器访问(DMA, Direct Memory Access)。

针对嵌入式系统的需求以及传统互连方式的局限性,RapidIO标准按如下目标被制定:

1.针对嵌入式系统机框内高速互连应用而设计。

2.简化协议及流控机制,限制软件复杂度,使得纠错重传机制乃至整个协议栈易于用硬件实现。

3.提高打包效率,减小传输时延。

4.减少管脚,降低成本。

5.简化交换芯片的实现,避免交换芯片中的包类型解析。

6.分层协议结构,支持多种传输模式,支持多种物理层技术,灵活且易于扩展。

三.协议的三层结构

为了满足灵活性和可扩展性的要求,RapidIO协议分为三层:逻辑层、传输层和物理层。

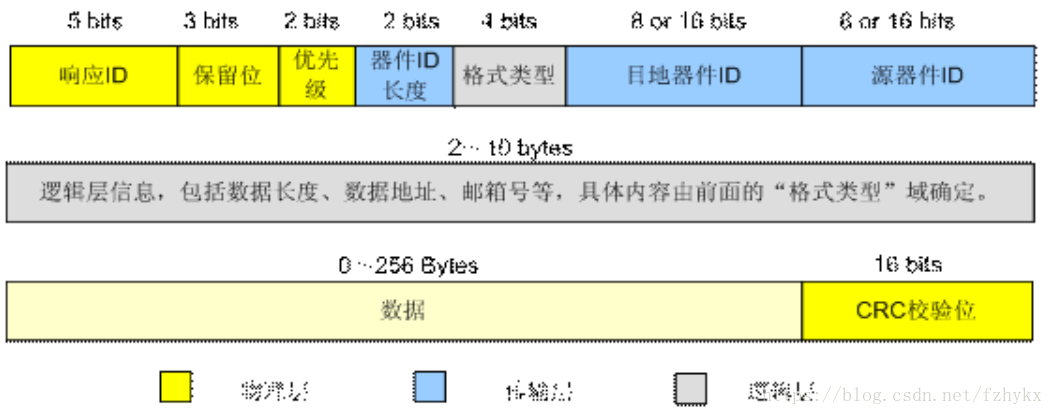

和以太网一样,RapidIO也是基于包交换的互连技术。如图3所示,RapidIO包由包头、可选的载荷数据和16bits CRC校验组成。包头的长度因为包类型不同可能是十几到二十几个字节。每包的载荷数据长度不超过256字节,这有利于减少传输时延,简化硬件实现。

上述包格式定义兼顾了包效率及组包/解包的简单性。RapidIO交换器件仅需解析前后16bits,以及源/目地器件ID,这简化了交换器件的实现。

逻辑层协议

逻辑层定义了操作协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息传递(Message Passing)。

直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。从功能上讲,这一特点和德州仪器DSP的传统的主机接口(HPI, Host Port Interface)类似。但和HPI口相比,SRIO(Serial RapidIO)带宽大,管脚少,传输方式更灵活。

对上层应用来说,发起直接IO/DMA传输主要需提供以下参数:目地器件ID、数据长度、数据在目地器件存储器中的地址。

直接IO/DMA模式又可进一步分为以下几种传输格式:

NWRITE: 写操作,不要求接收端响应。

NWRITE_R: 带响应的NWRITE(NWRITE with Response),要求接收端响应。

SWRITE:流写(Stream Write),数据长度必须是8字节的整数倍,不要求接收端响应。

NREAD: 读操作。

SWRITE是最高效的传输格式;带响应的写操作或读操作效率则较低,一般只能达到不带响应的传输的效率的一半。

消息传递(Message Passing)模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。

对上层应用来说,发起消息传递主要需提供以下参数:目地器件ID、数据长度、邮箱号。

传输层协议

RapidIO是基于包交换的互连技术,传输层定义了包交换的路由和寻址机制。

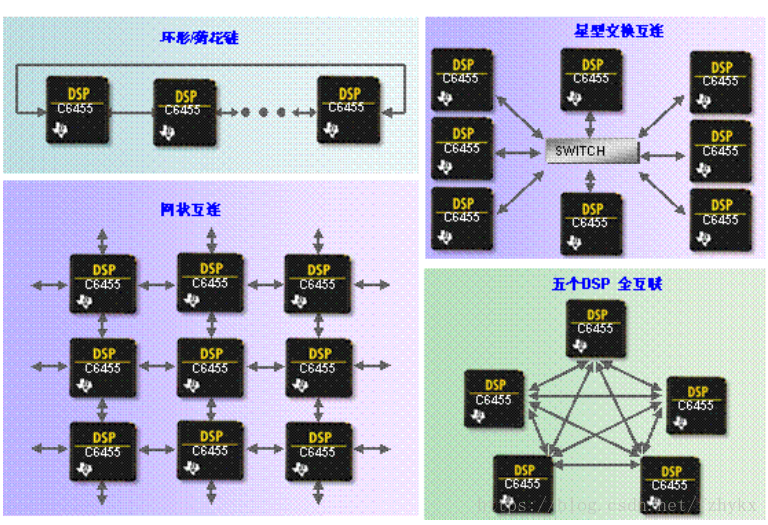

RapidIO网络主要由两种器件,终端器件(End Point)和交换器件(Switch)组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。RapidIO支持8 bits 或 16 bits器件ID,因此一个RapidIO网络最多可容纳256或65536个终端器件。与以太网类似,RapidIO也支持广播或组播,每个终端器件除了独有的器件ID外,还可配置广播或组播ID。交换器件根据包的目地器件ID进行包的转发,交换器件本身没有器件ID。

RapidIO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。以德州仪器(TI)的TMS320C6455 DSP为例,它有4个3.125G的SRIO口,它可支持的拓扑结构

物理层协议

RapidIO 1.x 协议定义了以下两种物理层接口标准:

8/16 并行LVDS协议

1x/4x 串行协议 (SRIO)

并行RapidIO由于信号线较多(40~76)难以得到广泛的应用,而1x/4x串行RapidIO仅4或16个信号线,逐渐成为主流,所以本文仅介绍串行RapidIO。

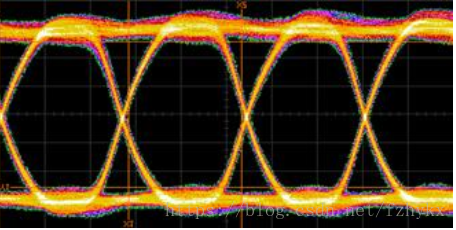

串行RapidIO基于现在已广泛用于背板互连的SerDes(Serialize Deserialize)技术,它采用差分交流耦合信号。差分交流耦合信号具有抗干扰强、速率高、传输距离较远等优点。差分交流耦合信号的质量不是由传统的时序参数来衡量,而是通过眼图来衡量,眼图中的“眼睛”张得越开则信号质量越好。下图是一个典型的串行RapidIO信号的眼图。

差分信号的强弱由一对信号线的电压差值表示,串行RapidIO协议规定信号峰-峰值的范围是200mV-2000mV。信号幅度越大,则传输距离越远,RapidIO协议按信号传输距离定义两种传输指标:

短距离传输(Short Run),<=50厘米,主要用于板内互连,推荐的发送端信号峰-峰值为500mV-1000mV

长距离传输(Long Run),>50厘米,主要用于板间或背板互连,推荐的发送端信号峰-峰值为800mV-1600mV

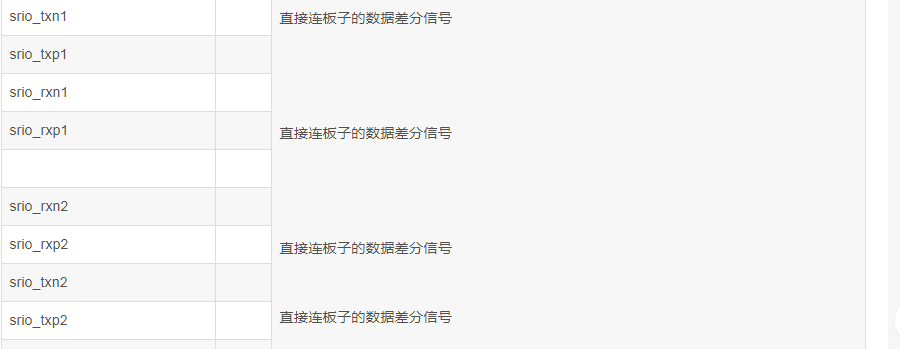

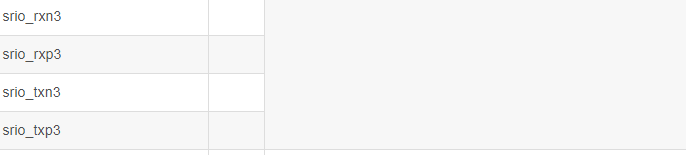

为了支持全双工传输,串行RapidIO收发信号是独立的,所以每一个串行RapidIO口由4根信号线组成。标准的1x/4x 串行RapidIO接口,支持四个口,共16根信号线。这四个口可被用作独立的接口传输不同的数据;也可合并在一起当作一个接口使用,以提高单一接口的吞吐量。

德州仪器TMS320C6455 DSP上集成了标准的1x/4x串行RapidIO接口,如图

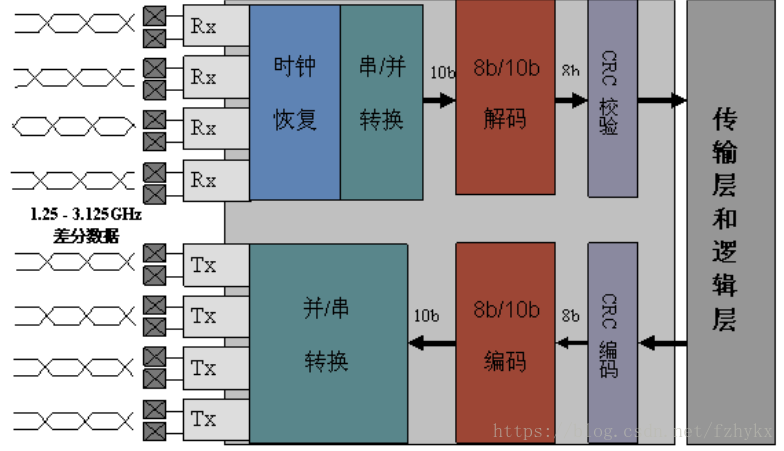

发送时,逻辑层和传输层将组好的包经过CRC编码后被送到物理层的FIFO中,“8b/10b编码”模块将每8bit数据编码成10bits数据,“并/串转换”模块将10bits并行数据转换成串行bits,发送模块把数字bit转换成差分交流耦合信号在信号线上发送出去。这里的8b/10编码的主要作用是:

保证信号有足够的跳变,以便于接收方恢复时钟。串行RapidIO没有专门的时钟信号线,接收端靠数据信号的跳变恢复时钟。所以需要把信号跳变少的8bits数据(如全0或全1)编码成有一定跳变的10bits数据。另外,也使得总体数据中0和1的个数均衡,以消除直流分量,保证交流耦合特性;

8b/10编码可扩大符号空间,以承载带内控制符号。10bits能表示1024个符号,其中256个表示有效的8bits数据,剩下的符号中的几十个被用作控制符号。控制符号可被用作包分隔符,响应标志,或用于链路初始化,链路控制等功能;

8b/10编码能实现一定的检错功能。1024个符号中,除了256个有效数据符号和几十个控制符号外,其它符号都是非法的,接收方收到非法符号则表示链路传输出错。

接收的过程则正好相反,首先接收方需要根据数据信号的跳变恢复出时钟,用这个时钟采样串行信号,将串行信号转换为10bits的并行信号,再按8b/10b编码规则解码得到8bits数据,最后做CRC校验并送上层处理。

数据被正确的接收时,接收端会发送一个ACK响应包给发送端;如果数据不正确(CRC错或非法的10bits符号),则会送NACK包,要求发送方重传。这种重传纠错的功能由物理层完成,而物理层功能往往由硬件实现,所以不需要软件干预。

串行RapidIO支持的信号速率有三种:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b编码,其有效数据速率分别为:1Gbps, 2Gbps, 2.5Gbps。4个1x端口或一个4x端口支持的最高速率为10Gbps。

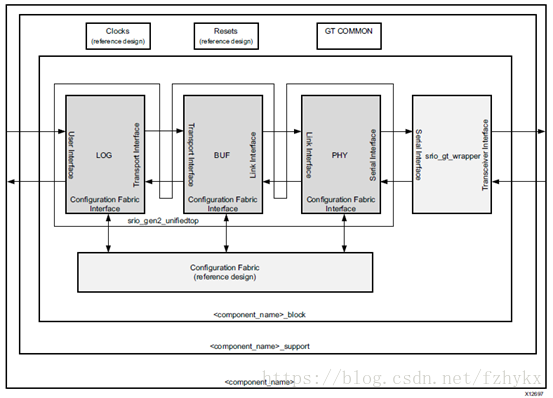

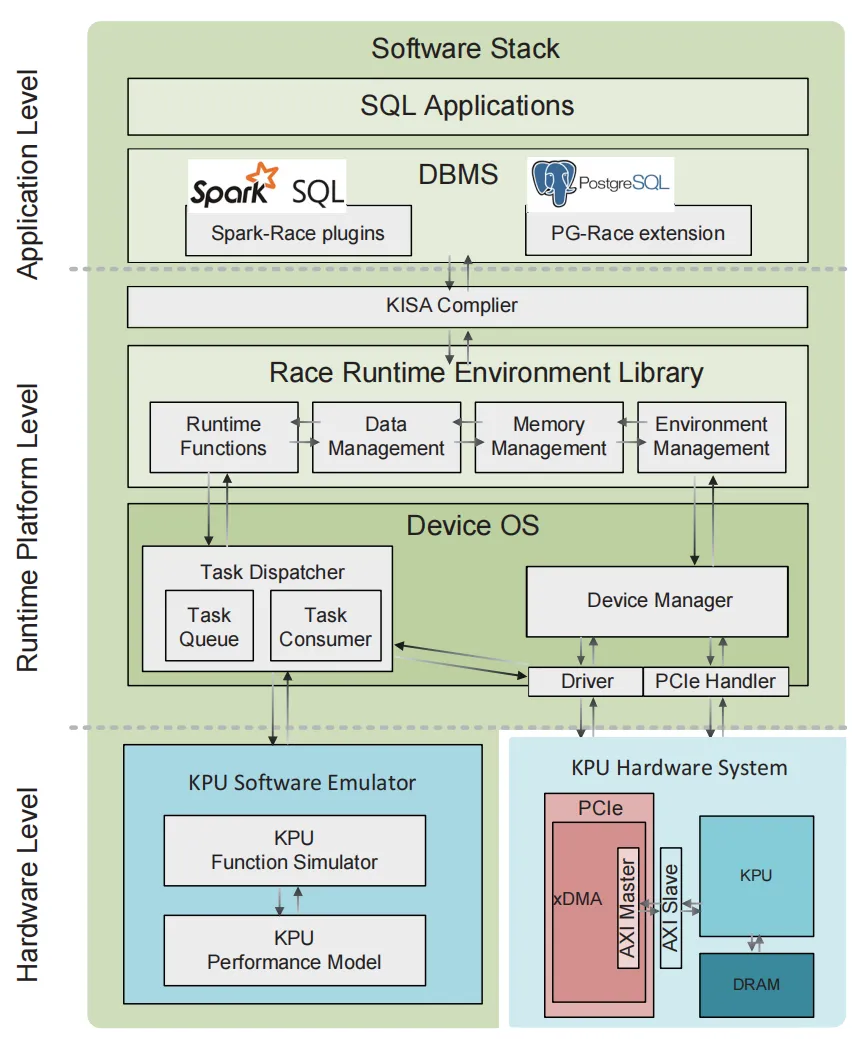

四.xlinx srio ip介绍

Endpoint IP由物理层、传输层及逻辑层组成,自带可配置buffer design、reference clock module、reset module及configuration fabric referencedesign。支持1x、2x、4x lane widths,支持per-lane speeds of 1.25、2.5、3.125、5.0及6.25Gbaud。SRIO Gen2使用AXI4-Stream接口用于高速数据传输。

逻辑层定义了操作协议和包格式。

传输层提供端点器件间传输包所需的路由信息。

物理层定义器件级接口的细节,如包传输机制、流量控制、电气特性和低级错误管理。

1.1SRIO系统预览

图一 Serial RapidIOSystem Overview

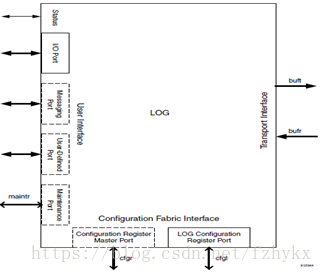

2.逻辑层接口介绍

由图一可以看到逻辑层有三种接口:ConfigurationFabric Interface,具体如下:

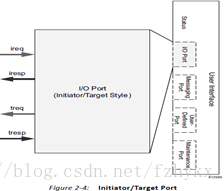

图二 逻辑层接口

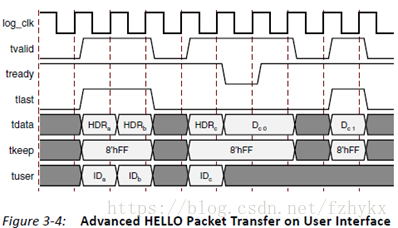

User Interface

主要包含一系列I/O ports和三类可选的ports,主要是用来发包和收包解析。对于使用哪些接口,在FPGA开发过程中,可以在IP core进行配置,实现时,每种事物根据事物的类型接入对应的port中。

其中,任何支持I/O事物传输的都将在I/O ports收发,如NWRITEs、NWRITE_Rs、SWRITEs、NREADs和RESPONSEs等事物;MESSAGE事物则可以在I/O ports传输,也可以在专用的messaging port传输;DOORBELL事物不管有没有message port,都将使用IO port进行传输;如果定义了maintenance接口,那么maintenance事物将通过maintenance接口进行传输;如果使用了User-defined接口的话,那么用户自定义的、系统不支持的或者未指明接口的事物将可以采用这种User-defined接口,如果未使能User-defined接口,那么上面提到这3种事物包将被丢弃。

必备的I/O Port

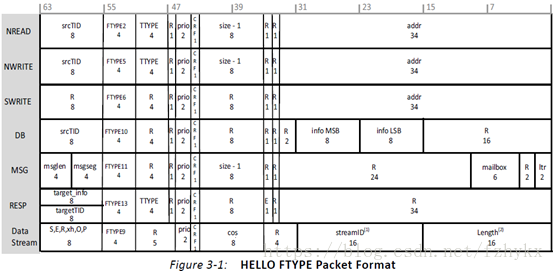

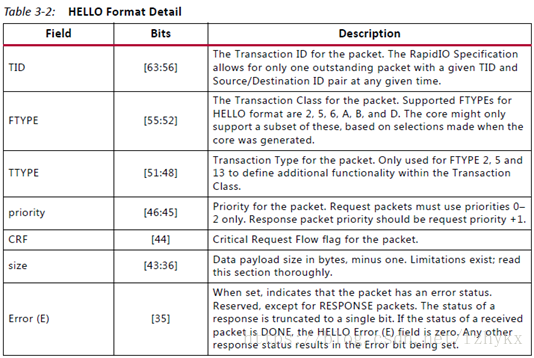

IO port支持2种格式:HELLO format 和SRIOstream。对于模式和包格式的选择都需要在创建IPcore的时候选定好,并且IO ports里面所有的channels都必须使用相同的包格式。

IO ports配置成condensedIO模式主要是为了减少channels数,此时只有一个AXI4-stream 用来收发数据。在这种模式下,SRIO的IO port很接近于PCIE的AXI总线。(注意端口命名的参考是LOG层).

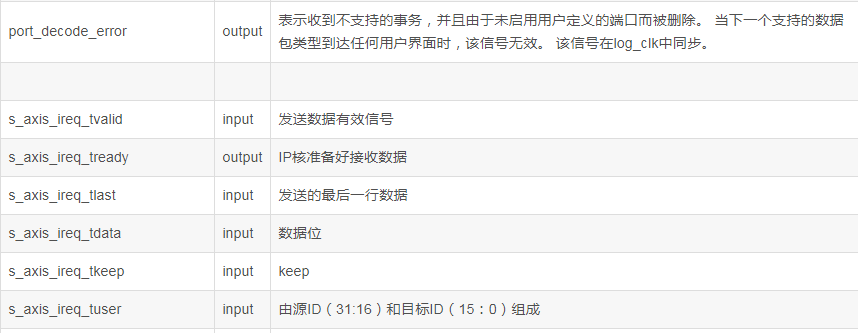

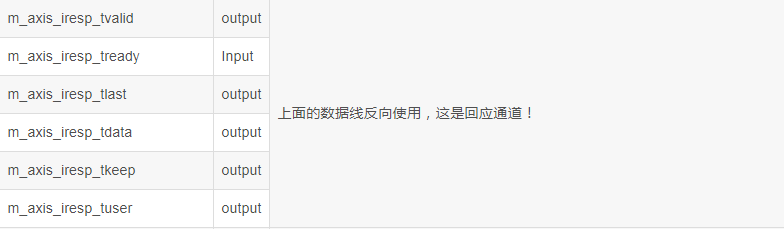

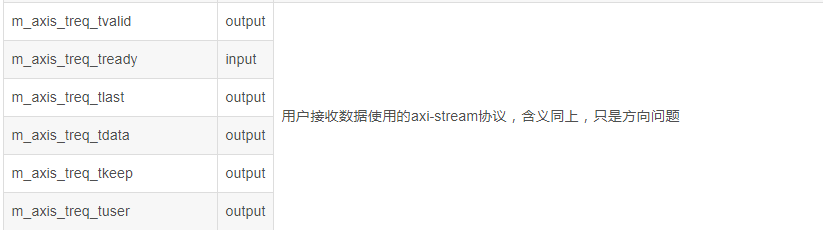

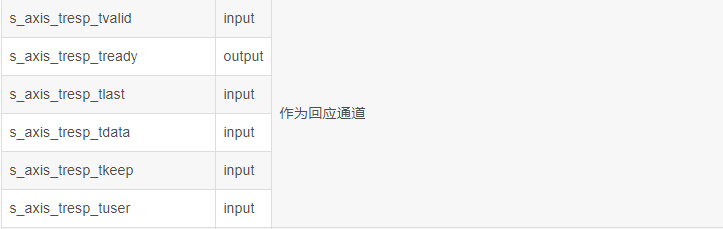

initiator/Target允许在远端的initiator发起事物并把本地的endpoint作为事物传送目标。从下面其接口图可以看出,其实感觉有点类似IIC,规定什么时候谁为master,向slave发起操作,故具备了2套独立的AXI4-stream用来收发数据。

s_axis_ireq* are associated with INITIATOR_IREQ.

m_axis_iresp* are associated with INITIATOR_IRESP.

m_axis_treq* are associated with TARGET_TREQ.

s_axis_tresp* are associated with TARGET_TRESP.

可选的Messaging Port

为什么是可选的呢,因为message也可以作为普通的wrtie事物通过I/O prot进行传输,IP core 产生时可以对这个进行选择。默认是和I/O port复用的,但是如果作为独立的port也是可以的,接口类型和initiator/Target一样。

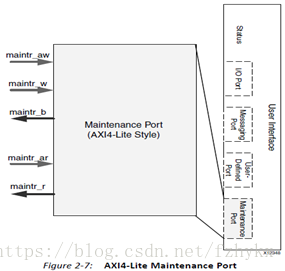

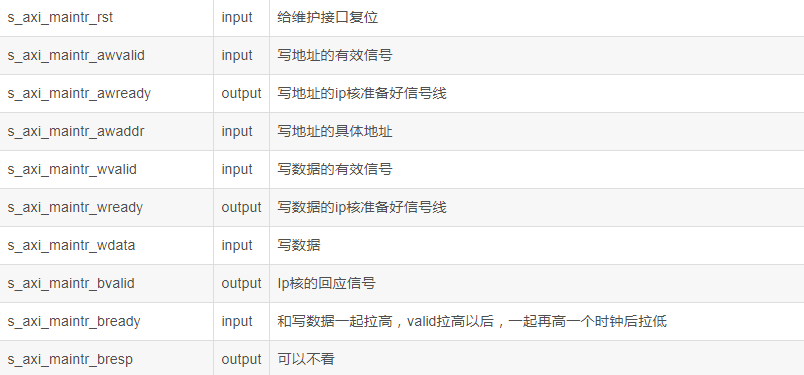

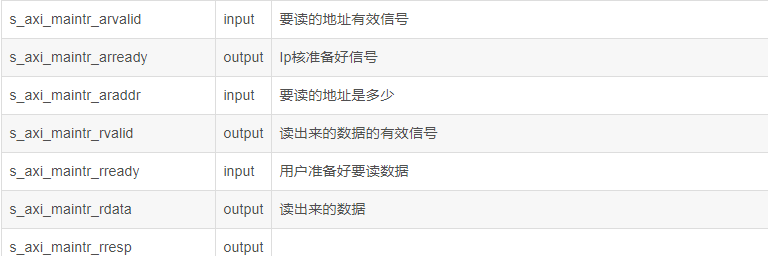

可选的Maintenance Port

虽然说这个是可选的,可是在xilinx的IP core配置上,这个好像是一定存在的,并且还被推荐配置成AXI4-Liteinterface,当然也可以配置成AXI4-Stream。这2种interface的区别主要在于AXI4-Lite interface不仅可以让用户app target本地的配置空间,还可以target远端的配置空间,而AXI4-Stream interface只能配置远端的配置空间。

可选的User-Defined Port

User-definedport采用的是SRIO stream format,并且拥有2个AXI4-Stream channels。

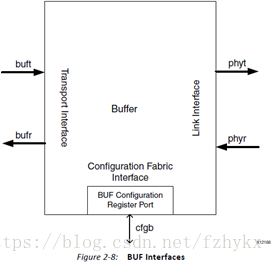

3.BUF接口

BUF层夹杂在LOG层和PHY层中间,为包的传送和流控制提供了保证。当然收发的buffer大小是可配的,值得注意的是,这里说的大小不是说fifo size或深度之类的,而是max sized packets的个数,即按最大size包的个数进行管理的。

上面的和LOG和PHY层的interface是AXI4-Stream,而cfgb则是AXI4-Liteinterface接口,实现进入BUF层的配置空间。

该层主要包含以下一些接口:

(1)clock andresetinterface

(2)transport interface

(3)link interface

(4)BUF configurationfabric interface

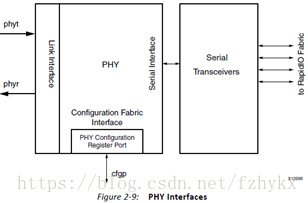

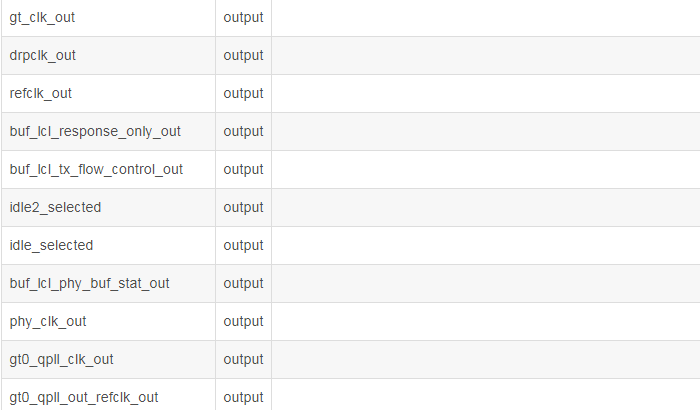

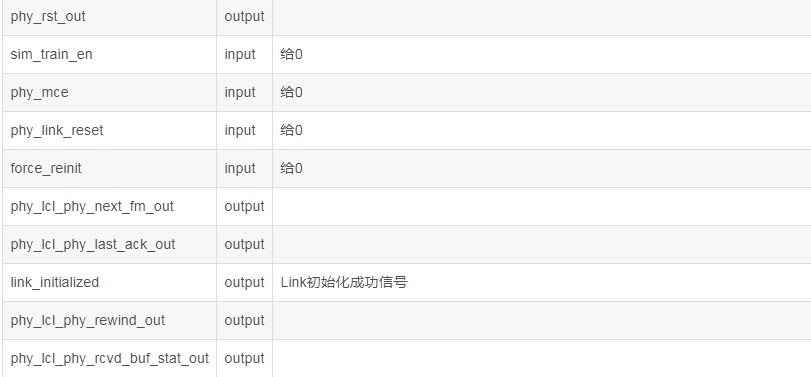

4.物理层接口

RapidIO串行物理层,通常称为串行RapidIO,针对板上或通过背板的器件间的电气连接。串行物理层定义器件间的全双工串行链路,在每个方向上使用单向差分信号。RapidIO串行物理层支持RapidIO器件间的包传送,包括包和控制符号的传送、流量控制、错误管理和其他器件到器件的功能。

由于串行RapidIO规范仅在物理层定义(RapidIO技术定于物理层为电气接口和器件到器件的链路协议),多数RapidIO控制器的逻辑是相同的。因此,串行RapidIO规范保留了许多已有的设计经验和经过证实的基础结构,简化了并行与串行链路间的系统级交换操作。

RapidIO串行物理层有如下特征:

(1)采用8B/10B编码方案将发送时钟嵌入到数据中;

(2)在每个方向上支持一个串行差分对,称为1通道;或支持四个并列的串行差分对,称为4通道;

(3)使用专用的8B/10B码来管理链路,管理内容包括流量控制、包定界和错误报告;

(4)允许在RapidIO1x/4xLP-Serial(串行RapidIO)端口和RapidIO物理层8/16 LP-LVDS(并行RapidIO)端口之间进行包传输而无需包处理;

(5)使用与并行RapidIO物理层相似的重传和错误恢复协议;

(6)支持每通道1.25G、2.5G和3.125G波特率(数据流为1.0Gbps、2.0Gbps和2.5Gbps)的传送速率。(现在支持的应该更多了,可以高达6.25G了)

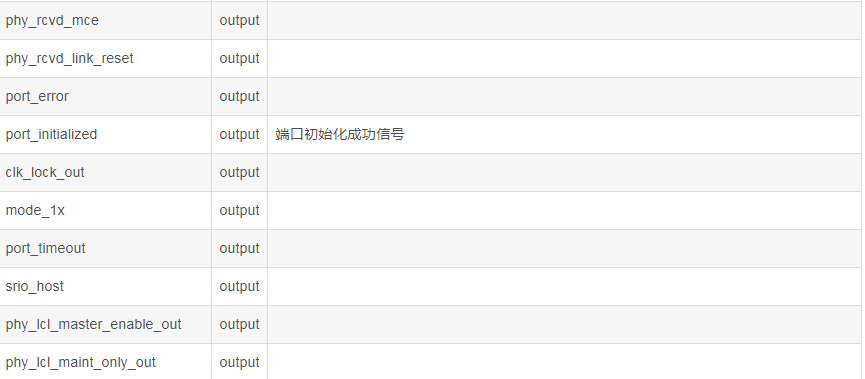

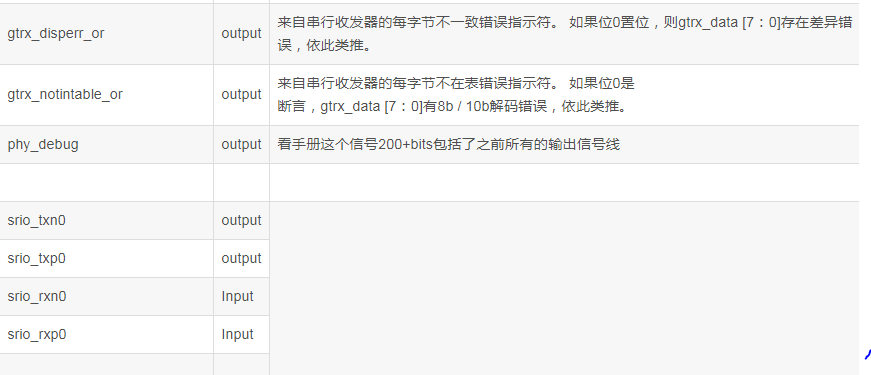

该层主要包含以下一些接口:

(1)clock and reset interface

(2)link interface

(3)serial interface

(4)control and statusinterface

(5)configuration fabricinterface

(6)serial transceiversinterface

(7)configuration fabricreference design interface

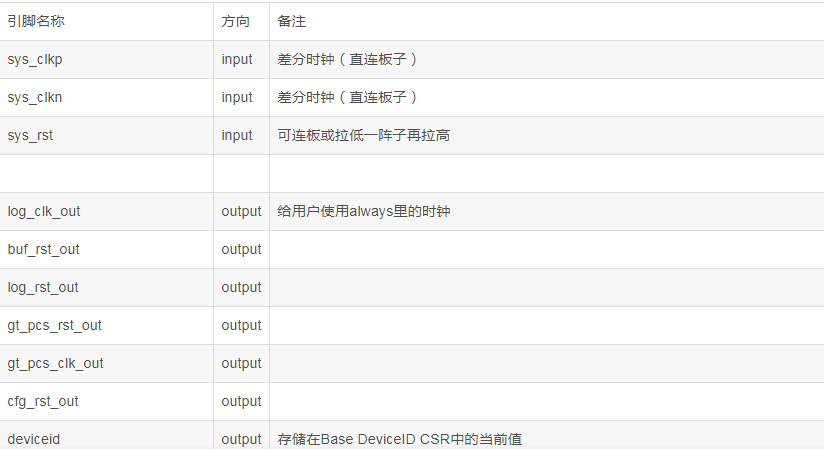

五.xlinx srio ip

在利用Xilinx的IP进行开发时,为了简化报文的解析和组包,SRIO Gen2 usesAXI4-Stream,Xilinx推出了一种简化的报文格式,这样一来,我们可以发现,这样又很接近PCIE的TLP报文格式了。

l HELLO format

引脚示意:

审核编辑 :李倩

-

嵌入式系统

+关注

关注

41文章

3716浏览量

133071 -

Xilinx

+关注

关注

73文章

2192浏览量

129885 -

RapidIO

+关注

关注

1文章

41浏览量

21460

原文标题:Xilinx Srio详解&IP核使用

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于INT与Flowlet的自适应路由:提升数据中心性能的关键

串口DMA接收数据包丢失怎么解决?

GD32F470+LWIP TCP偶尔丢包怎么解决?

如何用AI负载为SONiC交换机调整ECN水线

DPU核心技术论文再次登陆体系结构领域旗舰期刊《IEEE Transactions on Computers》

XSR芯片间互连技术的定义和优势

RapidIO:一种高性能、 低引脚数、 基于数据包交换的互连体系结构

RapidIO:一种高性能、 低引脚数、 基于数据包交换的互连体系结构

评论