将软件集中到一个硬件平台中被认为是航空电子设备的一种良好做法。事实标准 ARINC653 描述了它如何根据分区模型正确工作,排除和减轻硬件资源冲突。随着该模型的成功和多核处理器 (MCP) 的普及,认证机构已开始扩大其对使用多核处理器的接受程度。

CAST-32 方法为多核处理器打开了大门……

关于认证机构软件团队 (CAST),一个由认证和监管机构代表 (EASA, FAA) 组成的国际组织,发表了一篇名为 CAST-32 的论文,描述了允许使用多核 -机载系统中的处理器。从本质上讲,本文确定了可能对系统安全产生影响的主要主题,并且在大多数情况下,确定性是关键。CAST-32 的最终结论是可以使用多核处理器,但范围仅限于最多两个活动核心。

但随后的发展实际上允许有效地利用它们

随着 CAST-32 文件CAST-32A (2016) 的更新,这种情况发生了变化。现在可以在机载系统中并行使用处理器的所有内核。该文件明确允许使用多个核心,只要提交认证的组织(申请人)可以为所提到的问题提供最先进的解决方案。这些问题涉及硬件设计方面以及软件架构方面的问题。后者需要借助适当的操作系统打下坚实的基础。高级操作系统已经将多核支持紧密结合到其分区管理中。

规划的挑战

CAST-32A 定位文件的“规划”部分讨论了与处理器、架构、操作系统和工具的选择相关的所有主题。首先是申请人有责任识别 MCP。此外,CAST-32A 要求申请人注意软件架构(包括 IMA 考虑因素)、资源划分模型和要使用的开发工具。

最大的挑战:无冲突地管理共享处理器缓存

CAST-32A 中最具争议的话题被称为“干扰通道和资源使用”。它留给申请人来识别应用程序之间的干扰,定义资源使用,并评估对整个系统的确定性行为的影响。两个问题,共享处理器缓存和主内存带宽的影响正在挑战申请人构建系统。

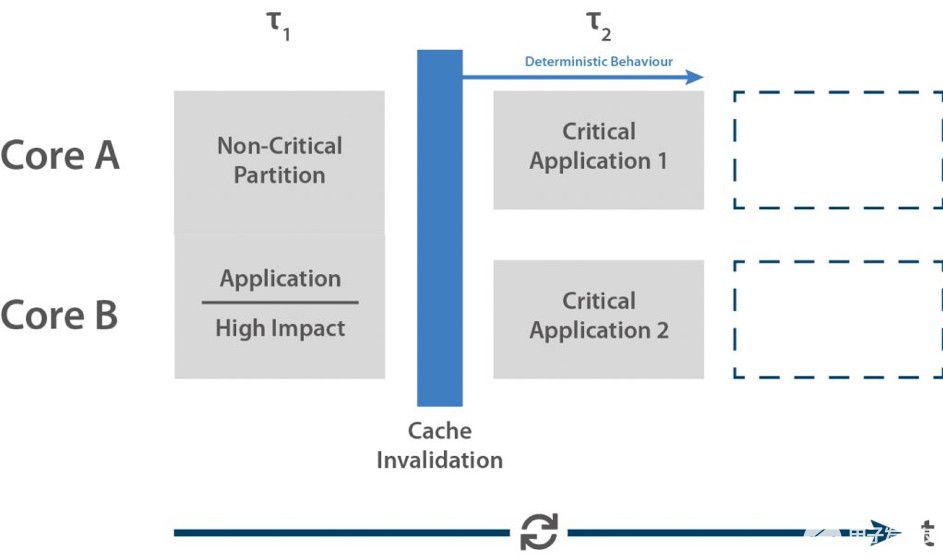

因为高级缓存在处理器内核之间共享,所以 CPU 的硬件必须处理同步问题。此外,共享缓存的状态可能会受到错误应用程序的影响,从而严重影响安全关键分区的性能。

内存冲突解决方案及时处理任务

为了为最坏的情况做好准备,符合 CAST-32A 的操作系统必须提供对缓存带宽的监控,以关闭错误的应用程序。除了这些在运行时适用的技术方法之外,申请人应该有可能(几乎)消除架构级别的缓存效应。最明显的方法是增加时间分区窗口的安全边际,这样即使共享缓存永久不稳定也能满足最坏情况执行时间(WCET)。这样做时,性能将受到显着影响。相反,申请人可以将应用程序排序为具有相同软件级别的组。通过确保安全关键进程并行运行,缓存可以在关键时间框架开始时失效。

另一个干扰源是主存储器总线。即使内存区域被分区并因此相互保护,对总线的访问也需要一定的时间。一个应用程序对内存总线的密集使用是以并行运行的应用程序为代价的。该主题与共享缓存讨论非常相似,缓解措施也几乎相同。

细粒度的锁定和清晰的前景

当在不同内核上执行的应用程序同时进入内核空间时,也可能发生争用,可能访问相同的数据结构。传统上,对整个内核内存的访问受到全局锁的保护,一次只允许一个内核执行操作系统服务。这在技术上可能是足够的,但在可扩展性方面并不令人满意。为了减少这种干扰通道的影响,一个兼容良好的操作系统必须使用细粒度的锁定,这大大降低了应用程序同时请求相同锁定的概率。

除了识别干扰信道之外,CAST-32A 论文还需要对每个核心的资源使用情况进行分析。例如,申请人仍然需要在合理的条件下确定安全任务的 WCET,并且必须最终确定安全裕度。这同样适用于内存区域大小的分析。一个好的操作系统必须通过提供有关内存预算和执行时间的信息来支持用户。

概括

认证机构团队 (CAST) 小组已经勾勒出在航空电子系统中使用多个处理器内核的方法。他们的定位文件 CAST-32A 涉及硬件设计方面以及软件架构方面的问题。借助操作系统PikeOS,SYSGO 公司交付了主要构建块之一,将强大的资源和时间分区扩展到具有多核的 CPU,完美地应用了 CAST-32A 论文的描述要求。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20327浏览量

254747 -

存储器

+关注

关注

39文章

7753浏览量

172165 -

操作系统

+关注

关注

37文章

7432浏览量

129599

发布评论请先 登录

CAST-32方法为多核处理器打开了大门

CAST-32方法为多核处理器打开了大门

评论