SAR ADC是一个非常常见的拓扑结构,这是一种在速度、分辨率和功率之间提供了很好平衡的折衷方案。SAR ADC的一个关键优势是几乎没有延迟。因此在很多应用领域都能看到使用SAR ADC。

本文将介绍SAR ADC的原理,以及SAR ADC驱动电路设计需要注意的一些要点。

SAR ADC原理

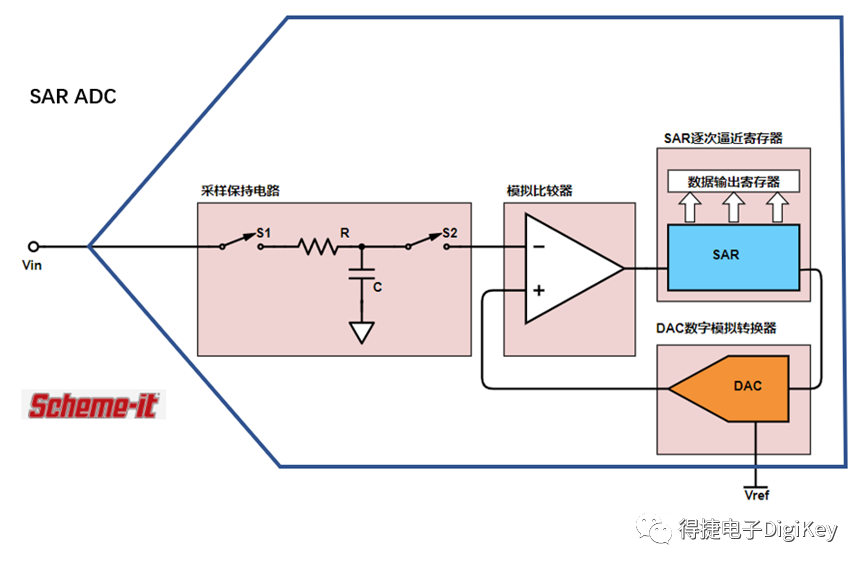

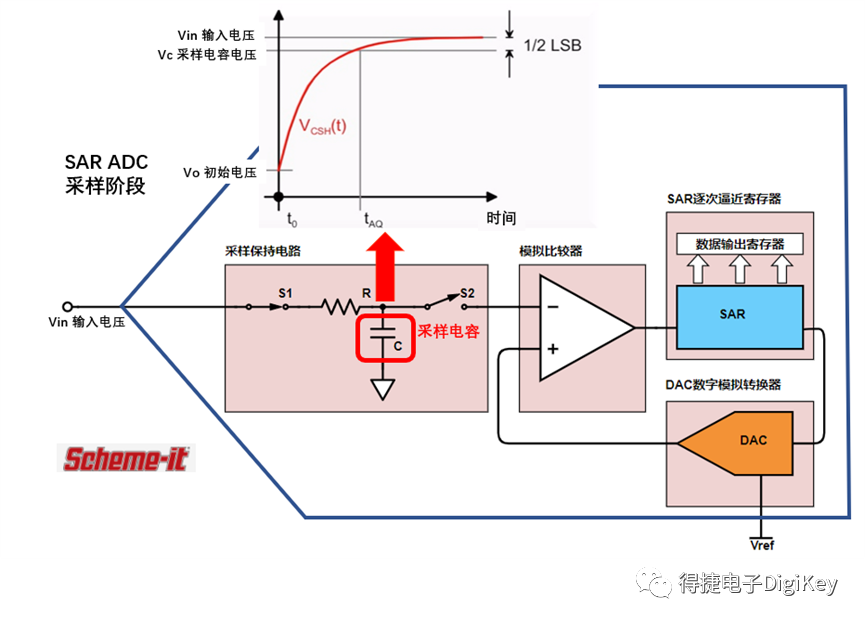

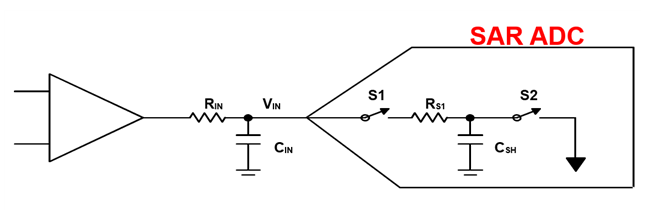

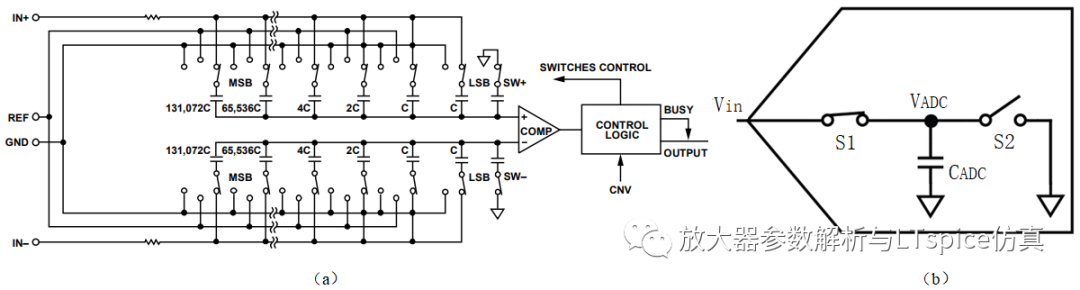

SAR ADC(Successive Approximation Register),即逐次逼近型ADC。 如下图,SAR ADC主要分成四个部分:采样保持电路、模拟比较器、SAR逐次逼近寄存器和DAC数字模拟转换器。

图1:SAR ADC的典型拓扑结构

SAR ADC的工作过程主要有两个阶段:采样阶段和转化阶段。

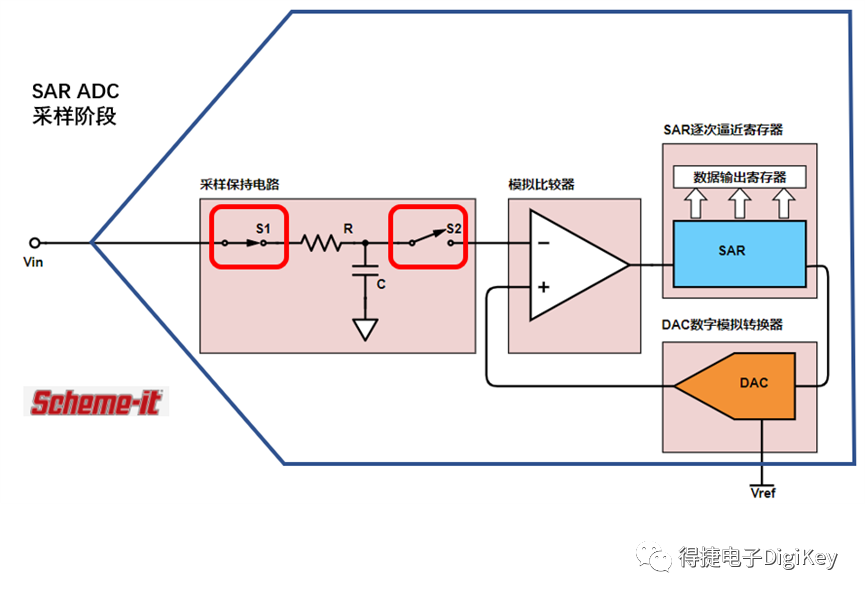

采样阶段:

在采样阶段,开关S2断开,开关S1闭合,这时对ADC采样电容C充电。

图2:SAR ADC的采样阶段

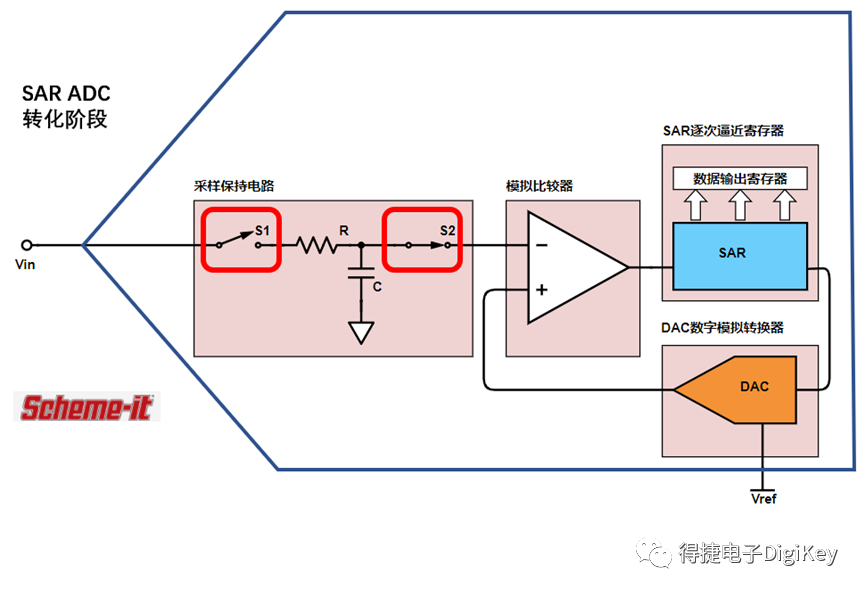

转化阶段:

在转化阶段,开关S1断开,S2闭合。

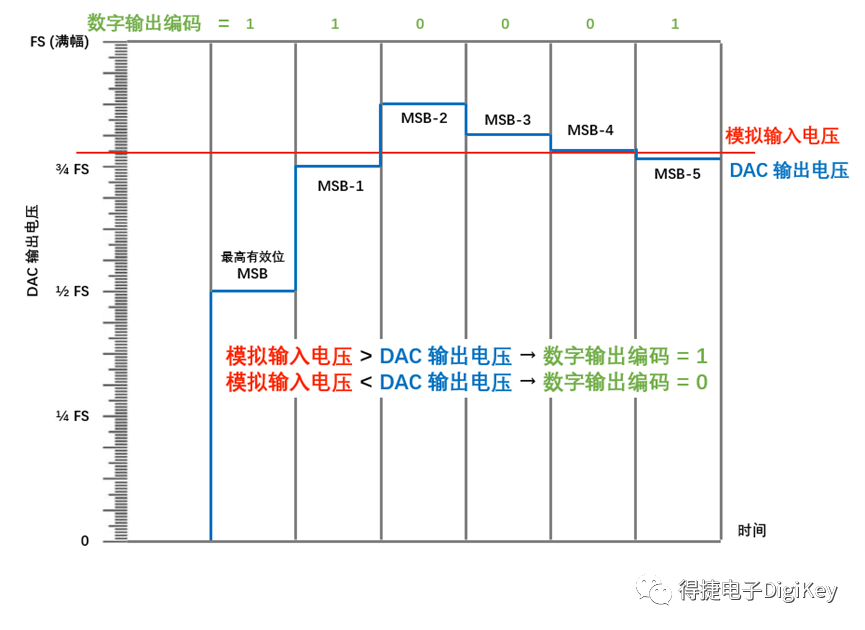

图3:转化阶段 下图是一个6-bit ADC转换过程:

采样电容上的电压与内部DAC通过比较器上的电压,从高位到低位,逐级比较。

逐次逼近寄存器在每个时钟周期向内部DAC提供额外的代码。

如果采样电容上的模拟电压高于内部DAC电压,记为1

如果采样电容上的模拟电压高于内部DAC电压,记为0

图4:6-bit ADC的转换过程 所以,转换时间是转换取决于时钟频率和ADC分辨率。上图示例中,转化需要6个时钟周期得到结果。结束转化之后,大多数ADC会返回采样阶段。

SAR ADC驱动电路设计

为什么需要驱动电路?

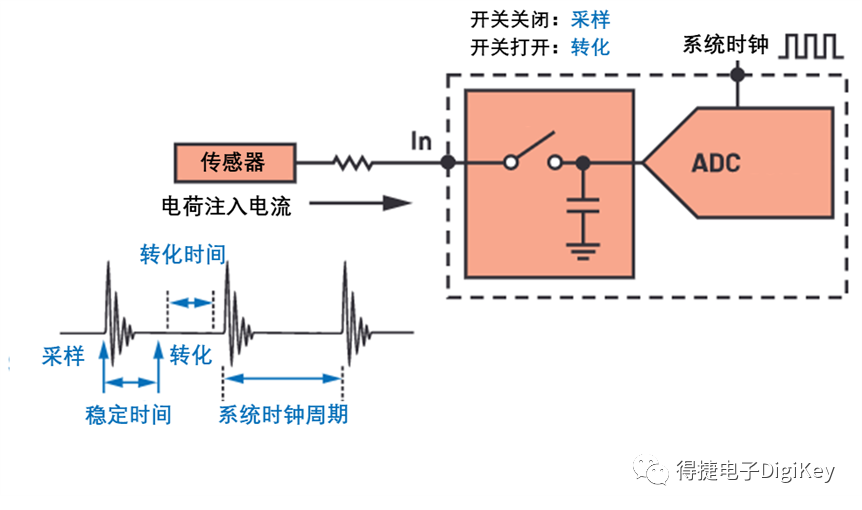

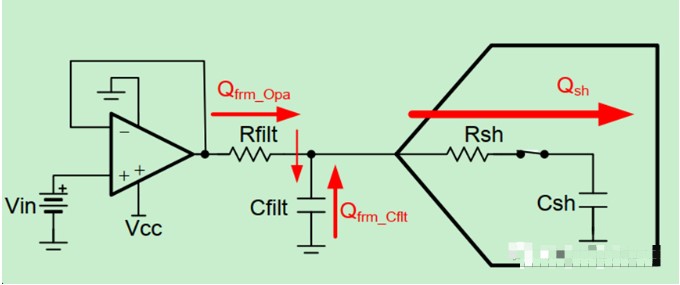

一般情况下,SAR ADC输入结构为开关电容采样电路。而电容的充放电需要足够的电流来支持。同时由于电容的存在,加上开关本身的一些片内寄生电容,会将一些电荷反向注入电源,称为电荷注入反冲,从而引起振荡。

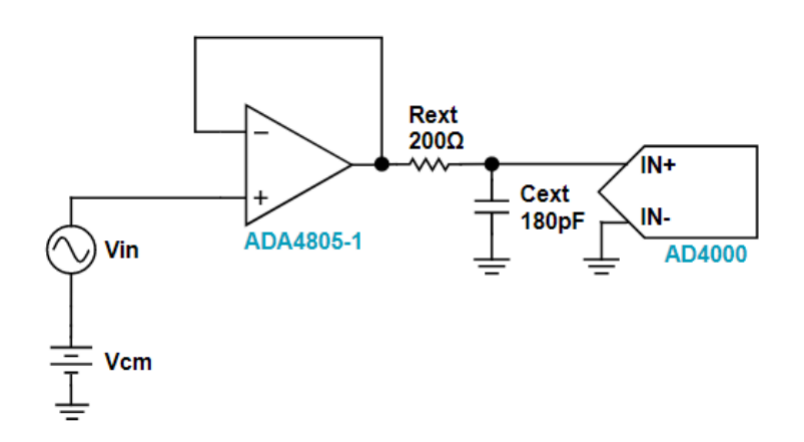

图5:开关电容采样电路, 电荷注入反冲(图片来源:ADI)

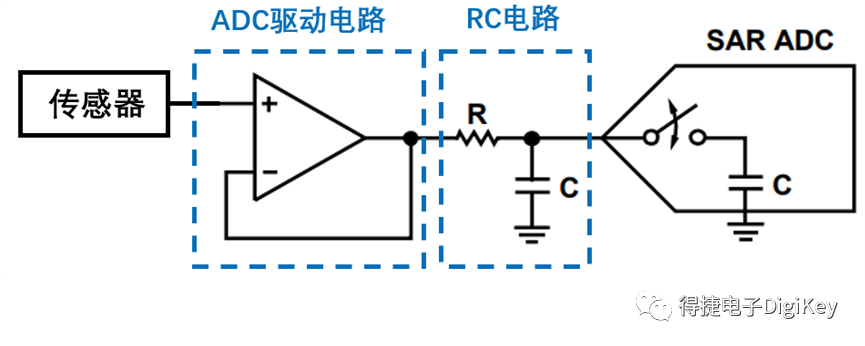

如上图:开关闭合的时候,采样;开关打开的时候,转化。每当开关闭合的时候,电容本身存在的电荷反向注入传感器,从而引起振荡。我们需要额外的稳定时间来排除这部分干扰。 为了给SAR ADC供电以及减少电荷反冲的影响。一般我们会在传感器和SAR ADC之间,添加ADC驱动电路(放大器)和开关采样电容充电RC电路。

图6:SAR ADC驱动电路设计(图片来源:ADI)

开关采样电容充电RC电路

RC起到的作用是减少电荷反冲的影响以及限制宽带噪声。这项要求又对放大器选择和性能构成了进一步的限制。 为了选择合适的RC阻值和容值,我们至少要确保以下两点: 第一,确保所选ADC驱动器和RC电路能切实驱动ADC。也就是说RC电路的电阻阻值不能过于大。是否能够足够驱动ADC,由ADC需要的输入电流大小决定,也就是ADC输入电阻大小决定。 第二,确保采样电容上的电压尽量接近输入电压。在转化阶段之前,确保采样电容上的电压尽量接近输入电压,且稳定到所需的分辨率。 如下图,在SAR ADC采样阶段,S1关闭,输入电压Vin通过电阻R对采样电容C充电。采样电容上的电压和输入电压之间的电压差应小于LSB(最低有效位)的一半。

图7:采样电容上的电压

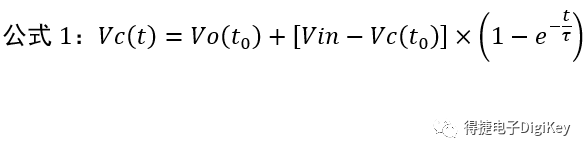

下面我们来看看时间常数τ的计算。 采样电容上的电压Vc与时间的函数关系:

如果只考虑ADC采样电路结构,时间常数t取决于内部采样电容器C和开关电阻R。时间常数t等于R乘以C。

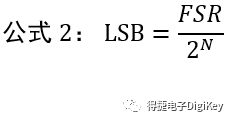

其中FSR为满量程范围,N为ADC的位数。 对于不同的分辨率,下表显示了至少需要多少个时间常数才能保证误差在1个LSB之内。

比如一个8位ADC,至少要6倍于时间常数的时间,才能保证误差在1个LSB之内。 推导计算过程,这里就不展开了,感兴趣可以看下面这篇ADI的文章:精密SAR模数转换器的前端放大器和RC滤波器设计 存在外部RC电路的情况下,需要一同考虑外部RC电路和内部ADC采样电路结构中的RC以及存在的其他的寄生阻抗参数,来计算时间常数τ。这里就不展开讨论。 为RC电路选择合适的电阻和电容,可访问Digi-Key相应的产品网页。

Digi-Key电阻

Digi-Key电容

ADC驱动电路(放大器)

驱动电路(放大器)的选择,我们需要注意以下两点:

放大器应支持充电电流并能够吸收电荷注入反冲。

该放大器的输出需要在采样边缘的末端完全稳定,使得对ADC输入采样时不会增加误差。

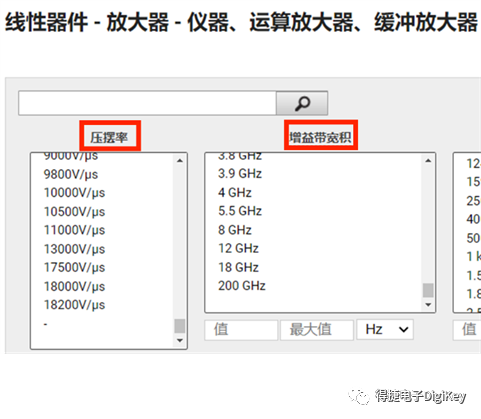

这意味着放大器应能提供瞬时电流阶跃,对应放大器应该具有高压摆率。对这些瞬态事件提供快速建立响应,对应放大器应该具有高带宽。 放大器选型时,可以通过压摆率和带宽等参数进行筛选。通过Digi-Key网站,可以方便地根据参数选择合适的放大器。

Digi-Key放大器

图8:Digi-Key网站中放大器参数选项

SAR ADC的选择

选择合适的SAR ADC,能大大减少对驱动电路的要求,简化驱动电路设计难度。大家可以通过Digi-Key网站进行快捷地选型。

Digi-Key SAR ADC

从SAR ADC驱动电路设计的角度考虑,我们需要注意以下两点:

长采样阶段

较长的采样阶段可以降低对驱动放大器的建立要求,并且允许较低的RC电路截止频率,这意味着可以使用噪声较高且/或功率/带宽较低的放大器。可以在RC电路中使用较大的R值和较小的对应C值,减少放大器稳定性问题,同时也不会大幅影响失真性能。较大的R值有助于在过压条件下保护ADC输入;同时还能降低放大器中的动态功耗。

高输入阻抗SAR ADC:

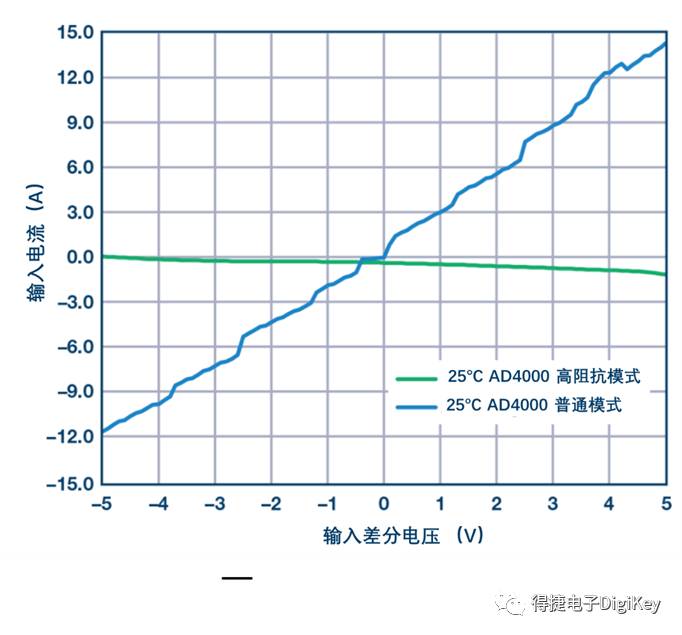

高输入阻抗的优势在于:在慢速 (<10 kHz) 或直流类信号条件下支持低输入电流,并且可在高达100kHz的输入频率范围内实现更好的失真 (THD) 性能。 我们以ADI AD4000举例,AD4000支持高阻抗输入模式,降低的输入电流需求,能以比传统SAR高得多的源阻抗来驱动。这意味着,RC电路中的电阻值可以比传统SAR设计大10倍。

图9:AD4000高阻抗模式和普通模式对输入电流的影响(图片来源:ADI)

在慢速应用中(信号带宽<10 kHz),高阻抗输入带来较低的输入电流,我们可以用较低截止频率的RC电路,低功率和带宽的精密放大器来驱动ADC,消除了使用专用高速ADC驱动器的必要性,从而降低功耗、尺寸和成本。

精密ADC驱动器设计工具

如果你觉得上面SAR ADC驱动设计很麻烦,也可以使用ADI精密ADC驱动器设计工具。你这样一来,你就可以根据不同的参数来模拟仿真,从而缩短精密ADC驱动器设计的时间。

图10:ADI 精密ADC驱动器设计工具 (图片来源:ADI)

本文小结

SAR ADC是一个非常常见的拓扑结构。驱动电路设计往往是SAR ADC设计的一个难点。理解SAR ADC原理。对于SAR ADC,RC电路、驱动电路(放大器),我们往往需要放在一起综合考虑。了解每部分的设计要点,使用适当的工具,往往能事半功倍。

审核编辑 :李倩

-

SAR

+关注

关注

3文章

448浏览量

48065 -

adc

+关注

关注

100文章

7950浏览量

556958 -

驱动电路

+关注

关注

160文章

1630浏览量

111940

原文标题:SAR ADC驱动电路设计有点难?掌握了这些要点,让你事半功倍!

文章出处:【微信号:电子工程世界,微信公众号:电子工程世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

LED驱动设计需要注意的问题

设计逐次逼近型模数转换器的驱动电路需要注意的三个方面

如何设计逐次逼近型模数转换器的驱动电路

ADC驱动器配置为差动放大器几点需要注意资料下载

SAR ADC驱动电路设计需要注意的要点

SAR ADC驱动电路设计需要注意的要点

评论