可以肯定地说,现在的计算世界如此丰富多彩,PCIe标准的贡献功不可没。

在处理器面世的头些年,整个计算领域的各个方面都在高速发展。但进入到上世纪80年代后,随着处理器的速度越来越快。以至于当时流行的总线带宽已经满足不了CPU的需求,并逐渐成为制约计算机处理能力进一步提高的瓶颈。于是在1991年,Intel、IBM、HP、Compaq、DEC等100多家计算机公司成立了PCISIG,联合推出PCI(Peripheral Component Interconnect),并于次年发布了PCI1.0标准。

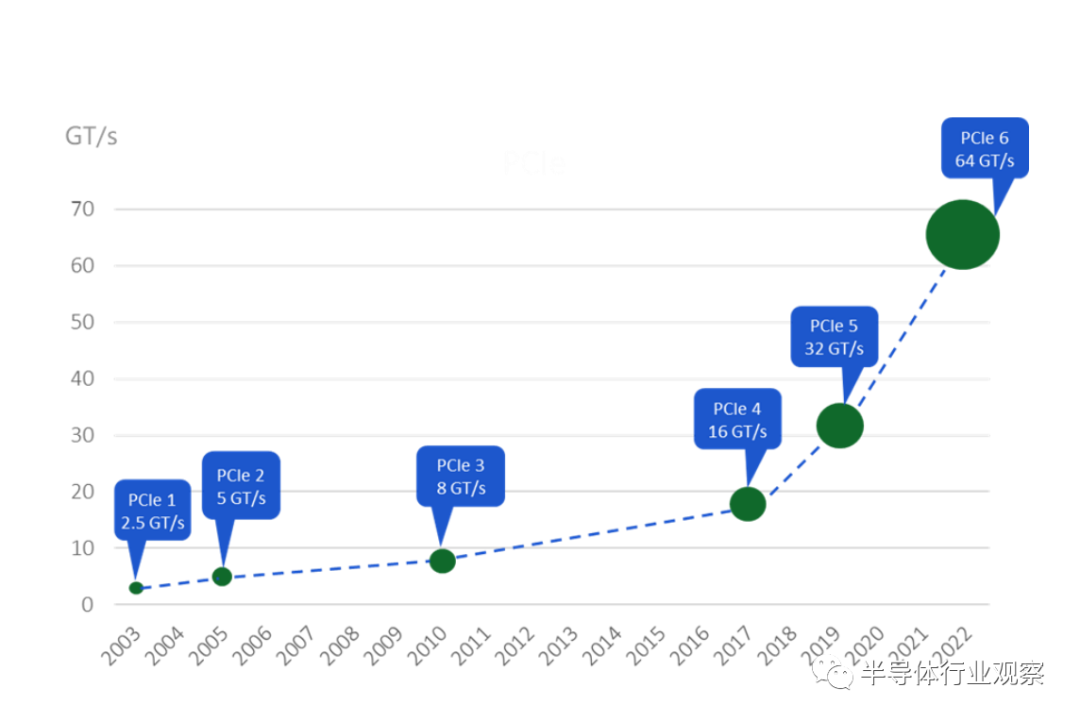

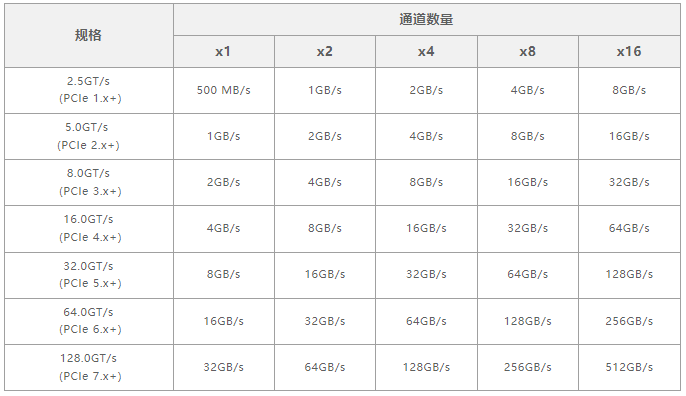

但在后续的发展中,行业参与者发现PCI还是不能满足总线的需求,于是他们又在接下来的日子里继续对其进行更新升级,并于2003年推出了广为人知的PCIe标准。和在PCI总线上同时挂接多个I/O设备不同,PCIe标准采用了点对点串行连接,物理上只能连接一个设备。通过在物理层、链路层和传输层的定义和升级,PCIe逐渐成为数据中心和计算应用中芯片间数据传输的行业标准。随着终端的需求,也在今年1月正式进入了PCIe 6.0时代。

如上图所示,每一代的PCIe标准较之上一代,都实现了较大的速度提升。为了达成这个目的,PCIe 6.0做了一些不同以往的新升级。

PCIe 6.0改变了什么?

对于全新标准,首先从速度上看,和以往的标准一样,PCIe 6.0同样实现了翻倍提升——获得了高达64GT/s的速率体验。同时,新标准还克服了整个通道传输长度以及距离的限制,具备前向纠错(FEC)以及固定大小数据包(Flit)等新特性。其中,在速度方面的提升,则主要是通过采用新的PAM4调制信号方式实现。

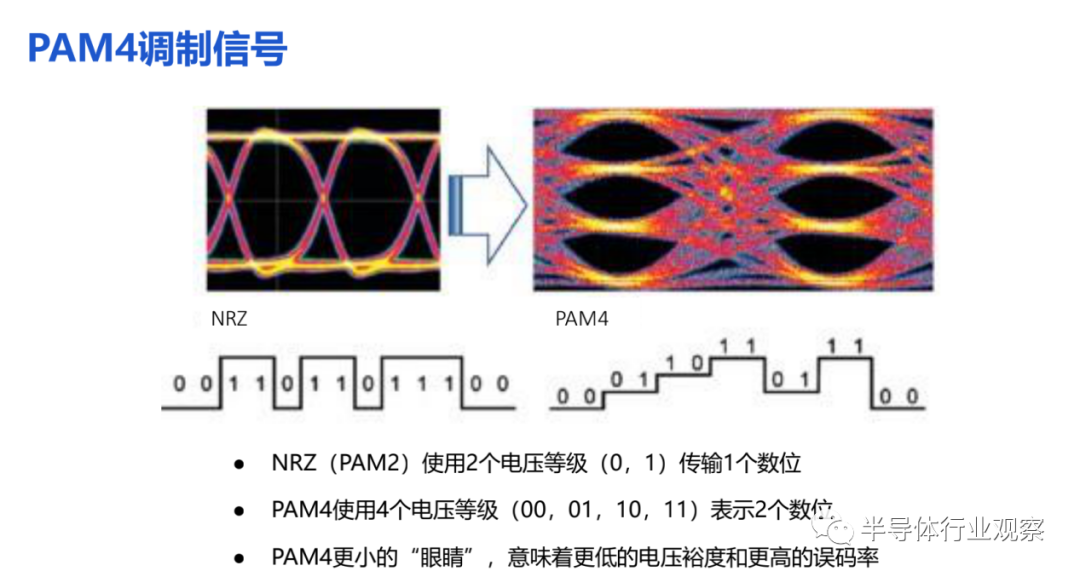

从Rambus 战略营销副总裁Matt Jones的介绍我们得知,在PCIe 6.0以前,PCIe一直采用的是NRZ调制信号方式,也就是“ Non-Return-to-Zero ”——不归零编码。在实际应用中,这种编码模式采用0或1两个电压等级,每一个时钟周期只能传输1bit的信号。也就是说它只采用了高低两种信号电平。因此,与采用四电平的PAM4相比,我们也将NRZ称作PAM2 。

在以前的标准,这种编码模式还是能够实现其规定的速度,但进入到PCIe 6.0,PAM 4的采用是刻不容缓了,这主要与奈奎斯特频率有关。根据维基百科,奈奎斯特频率(英语:Nyquist frequency)是离散信号系统采样频率的一半,因瑞典裔美国工程师哈里·奈奎斯特(Harry Nyquist)或奈奎斯特-香农采样定理得名。采样定理指出,只要离散系统的奈奎斯特频率高于被采样信号的最高频率或带宽,就可以避免混叠现象。

回到PCIe标准上,据介绍,在进入PCIe 5.0时代后,数据速率的增加,也让奈奎斯特频率从8GHz加倍到16GHz,这就使得PCIe 5.0的频率相关损耗比PCIe 4.0要严重得多。再加上电容耦合(噪声和串扰)的增加,使得PCIe 5.0通道成为最难处理的NRZ通道。换而言之,如果PCIe 6.0仍然保留NRZ信号,则奈奎斯特频率将增加到32GHz,通道损耗大于60dB,这对于实际系统而言太大了。这就是我们需要从NRZ更改为PAM-4的原因。这一变化意味着发射和接收的信号现在有四个不同的电压电平,而不是两个。

PAM4是PAM(Pulse Amplitude Modulation,脉冲幅度调制)调制技术的一种。作为NRZ(NonReturn-to-Zero)后的热门信号传输技术,PAM4是多阶调制技术的代表,当前也被广泛应用在高速信号互连领域。 Matt Jones也指出,通过PAM4,每个时钟周期的数据传输可以达到2bit,而并不仅仅是单bit的数据传输。又因为PAM4采用四个不同的电平等级,因此能在每个时钟周期表达2个数位,分别是00、01、10再到11。这就意味着在同样的电压波动范围之内和同样的时钟周期内,由于PAM4的电压等级比PAM2高了两个,即眼图中黑色的区域“眼睛“这个部分更多、更小了。

“这种变化带来了另外两个重要的影响,即更低的电压裕度和更高的误码率,使得在设备中保证信号完整性成为了一个非常关键的难题。”Matt Jones强调。

至于前文谈到的前向纠错技术(FEC),按照Matt Jones所说,这是为了在保持数据传输速率的前提下解决PAM4本身的问题。而这种算法技术则恰好可以在数据传输链路中确保所有信号的完整性。

“同时,FEC技术的采纳还改变了数据流控制单元的情况,要求我们也必须针对数据包本身的大小做出调整和改变。在PCIe 6.0之前的几代规范采用的都是可变大小的数据包。但由于FEC技术的采纳,PCIe 6.0必须采用固定大小数据包(FLIT),以更好地保证FEC技术的实现和操作。”Matt Jones接着说。

为了减少整体系统的能耗,PCIe 6.0还采用了颠覆式的L0p模式,其本质是通过动态的信道分配,允许将每个通道进行封闭或者打开来实现系统性的节能。

PCIe 6.0的关键

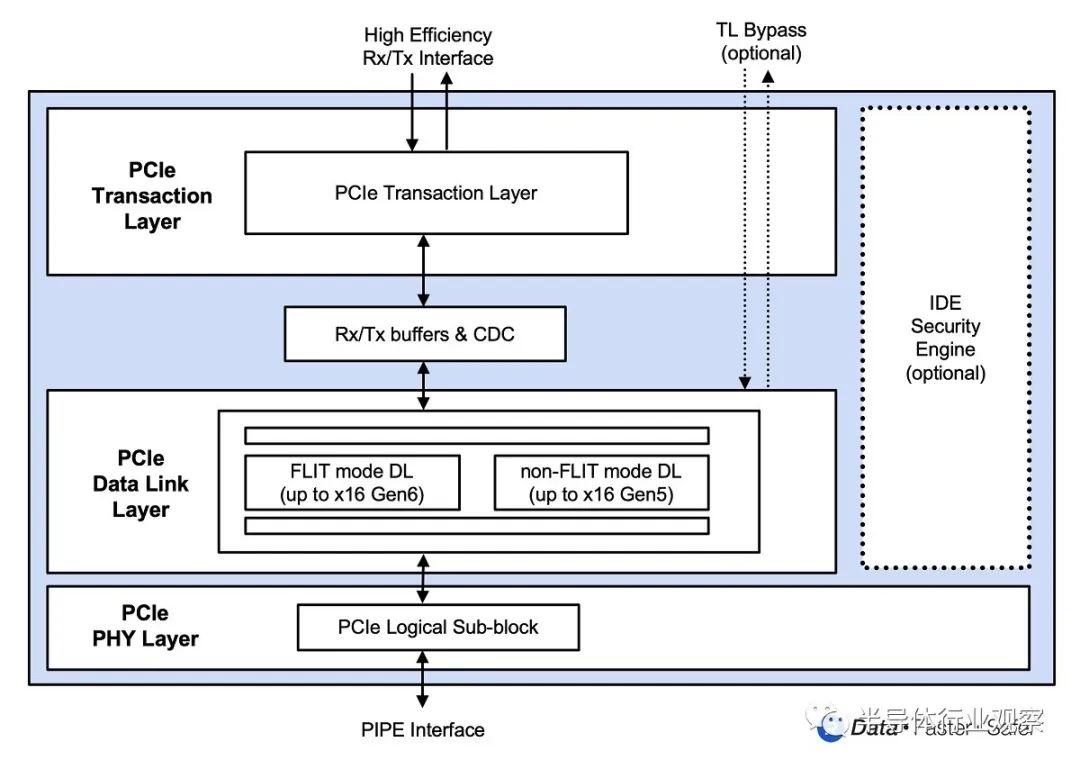

熟悉PCIe的读者应该知道,所有的PCIe外设要想连接到系统上,关键就在于其控制器。因为多个标准的出现,市场对PCIe 控制器又提出了更多的需求。以PCIe 6.0 控制器为例,不但要要支持 PHY Interface for PCI Express (PIPE) 规范的 6.x 版,还要向后兼容 PCIe 5.0、4.0 和 3.1/3.0 规范。并且能够满足众多客户和行业用例,例如可配置为支持端点、根端口、交换机端口和双模拓扑,以帮助实现多种使用模型。

因为终端对速度的需求量猛增,市场对PCIe 6.0也翘首以待,作为这个市场的重要玩家之一,Rambus也推出他们全新的PCIe 6.0 控制器。

Matt Jones告诉记者,Rambus的PCIe 6.0控制器不但数据传输速率能达到新标准设定64GT/s。更重要的一点是,该控制器还集成了完整性和数据加密(IDE)引擎,使其可以实现数据在不同PCIe设备的PCIe通路之间的安全传输。同时,该控制器在功耗、面积以及延迟上都特别进行了相应的优化,特别在降低能耗方面,以帮助确保PCIe 6.0成为数据中心解决方案的一块关键基石,进而推动环保型数据中心的建设,并减少对散热管理的需求,降低拥有成本。

此外,Rambus的PCIe 6.0控制器还非常灵活,可以适用于PCIe端点、根端口、双模式和交换机端口配置。

Rambus总结道,公司PCIe 6.0控制器的主要特性包括但不限于:支持PCIe 6.0规范,包括64 GT/s数据传输速率和PAM4信令;支持实现高带宽效率的固定大小的FLIT;实现低延迟前向纠错 (FEC) 以提高链路稳健性;内部数据路径大小可根据最大值自动放大或缩小(256、512、1024 位)链接速度和宽度,以减少门数和优化吞吐量;向后兼容PCIe 5.0、4.0和3.0/3.1;支持端点、根端口,以及双模式和交换机端口配置以及针对性能进行了优化的集成IDE。

Matt Jones指出,PCIe 6.0早期的使用场景是高性能计算的应用(如AI加速器),这些计算密集型应用通常选择的节点是高级节点,尤其集中在5纳米和3纳米。但是,随着PCIe 6.0在未来的成熟,进入到其他的应用领域,可能更多使用者会考虑成本因素,并转向不那么先进的节点。

Matt Jones同时强调,Rambus的PCIe 6.0的控制器将成为ASIC供应商的重要基石,帮助他们为AI/ML加速器建立起一个更加完善的PCI生态系统,并支持不断发展的数据中心中PCIe 6.0级数据传输的基础设施。

除了PCIe以外,Rambus还在备受关注的CXL(Compute Express Link)标准上扮演先锋者的角色。这是一种开放式互连新标准,面向 CPU 和专用加速器的密集型工作负载,这些负载都需要在主机和设备之间实现高效稳定的存储器访问。

Rambus 大中华区总经理苏雷透露,在去年,Rambus发布CXL内存互连计划,推出了一系列面向数据中心的新的解决方案,目标是让数据中心架构进入下一个更高效节能的新阶段。他进一步指出,现在已经有厂商在CXL的合作上与Rambus进行了沟通。展望未来,CXL也会推出池化的概念,这将帮助下一代的数据中心变得更加高效化、节能化,以一种新的架构来迎合数据中心的未来需求。

之所以Rambus能够在总线技术上拥有那么如此实力,如苏雷所说,这从公司的名称上可以体现的淋漓尽致。他表示,Rambus可以拆分为RAM和BUS,其中RAM代表内存,BUS是总线,这也代表了公司的两个发力方向。在历经多年的发展,Rambus也已经积累了3000多项专利和应用,公司的主要业务也涵盖了基础专利授权、芯片IP(接口IP和安全IP)授权以及内存接口芯片。

正因为拥有如此丰富的技术根基,这让他们能够为全球客户提供全方位服务。具体到中国方面,苏雷表示,Rambus会紧密联系中国产业链上下游伙伴,除了提供优异性能的产品外,还提供紧密高效的技术支持。“我们将自身的技术经验分享给客户,以在设计阶段就给客户一些建议和指导,帮助客户的产品以高质量更快上市。这也深得客户的支持和欢迎,并且让他们的产品更有竞争力。”苏雷最后说。

审核编辑 :李倩

-

cpu

+关注

关注

68文章

11216浏览量

222897 -

PCIe

+关注

关注

16文章

1420浏览量

87537

原文标题:关于PCIe 6.0,你需要知道的!

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCIe 5.0市场加速渗透,PCIe 6.0研发到来

什么是ARM架构?你需要知道的一切

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

曙光存储超级隧道技术助力应对PCIe 6.0时代

已收藏!你需要知道的57个常用树莓派命令!

关于 树莓派5 超频:你需要知道的一切!

Diodes公司PCIe 6.0时钟缓冲器介绍

BLDC霍尔安装角度你知道多少?(可下载)

PCIe 7.0最终版草案发布,传输速率128 GT/s,PCIe 6.0加速商业化

是德科技PCIe 6.0发射机合规性测试解决方案

详解PCIe 6.0中的FLIT模式

PCIe 6.0时代的测试挑战和解决方案

慧荣正在开发4nm PCIe 6.0 SSD主控芯片

PCIe 6.0 互操作性PHY验证测试方案

Modbus和RS-485的组合使用,你需要知道这些!

关于PCIe 6.0,你需要知道的!

关于PCIe 6.0,你需要知道的!

评论