缓冲器分为输入缓冲器和输出缓冲器两种;输入缓冲器的作用是将外设送来的数据暂时存放,以便处理器将它取走,输出缓冲器的作用是用来暂时存放处理器送往外设的数据。

缓冲器的工作原理:

当液压缓冲器受到碰撞压力时,动能经塞头和加速弹簧转给活塞,使其向右运动,活塞的运动挤压工作腔内的油液,弹簧复位压缩,同时使油液从活塞与顶杆之间的环形间隙挤压出来,进入贮油腔。

在活塞开始运动时,由于与顶杆之间的环形间隙较大,油液容易被挤出;在活塞继续运动时中,环形间隙会变得越来越小,活塞阻力会不断增大,到顶杆的圆柱形阶段后,环形间隙为零,阻力也稳定于最大值,这一过程消耗了大量动能,起到缓冲作用,当工作完毕,活塞被复位弹簧推至原始位置,完成一个工作循环。

缓冲器的作用:

- 减少电磁干扰

- 限制dI/dt或dV/dt

- 减少因开关导致的损耗

- 减少或消除电压电流过冲

- 转移功率损耗到电阻或有用负载

- 规整负载使其保持在安全范围内

文章整合自:dzsc、eepw、chetan

编辑:ymf

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电流

+关注

关注

40文章

7227浏览量

141600 -

缓冲器

+关注

关注

6文章

2236浏览量

49049 -

电磁

+关注

关注

15文章

1209浏览量

54180

发布评论请先 登录

相关推荐

热点推荐

深入解析SN74SSTVF16857 14位寄存器缓冲器

Instruments)的SN74SSTVF16857 14位寄存器缓冲器。 文件下载: SN74SSTVF16857VR.pdf 一、产品概述 SN74SSTVF16857属于德州仪器Widebus™系列产品。它

74LVC2G17Q:汽车级双缓冲器的卓越之选

工作。该器件具有两个独立的缓冲器,由于施密特触发器的作用,其正向((V {T+}))和负向((V {T-}))信

74AHC244:八进制缓冲器/线路驱动器的技术剖析

深入了解一下SG Micro Corp推出的74AHC244八进制缓冲器/线路驱动器。 文件下载: 74AHC244.pdf 一、产品概述 74AHC244是一款具有三态输出的八进制缓冲器/线路驱动

74AHC541 八进制缓冲器/线路驱动器:设计与应用全解析

SGMICRO 推出的高性能八进制缓冲器/线路驱动器——74AHC541。 文件下载: 74AHC541.pdf 一、产品概述 74AHC541 是一款具有三态输出的八进制缓冲器/线路驱动器

探索LMV112:高速双时钟缓冲器的卓越性能与应用

高速双时钟缓冲器,了解它的特性、性能以及在各种应用中的表现。 文件下载: lmv112.pdf 一、LMV112概述 LMV112是一款专为便携式通信和精确多时钟系统设计的高速双时钟缓冲器。它

SN74SSTUB32866:25位可配置寄存器缓冲器的设计与应用

(Texas Instruments)的SN74SSTUB32866这款25位可配置寄存器缓冲器,了解它的特性、工作原理以及应用场景。 文件下载: sn74sstub32866.pdf

CDCLVP1102:高性能时钟缓冲器的卓越之选

CDCLVP1102:高性能时钟缓冲器的卓越之选 在电子设计领域,时钟缓冲器的性能对整个系统的稳定性和可靠性起着至关重要的作用。今天,我们就来深入了解一下德州仪器(TI)的CDCLVP1102,一款

探索 CDCLVD1212:低抖动 LVDS 缓冲器的卓越性能与应用指南

——CDCLVD1212,它在众多领域都展现出了非凡的实力。 文件下载: cdclvd1212.pdf 产品概述 CDCLVD1212 是一款 2:12 的低附加抖动 LVDS(低电压差分信号)缓冲器,由德州仪器(TI)制造。它具有诸多令人瞩目的特性,能够在多种应用场景中

时钟缓冲器技术选型与设计要点

在现代高速数字系统中,时钟信号的完整性直接影响着系统的性能和稳定性。时钟缓冲器作为时钟树设计的核心组件,承担着信号分配、噪声隔离和时序优化的关键任务。随着5G通信、AI芯片和数据中心等领域的快速发展

NL17SZ07非反相开漏缓冲器技术解析与应用指南

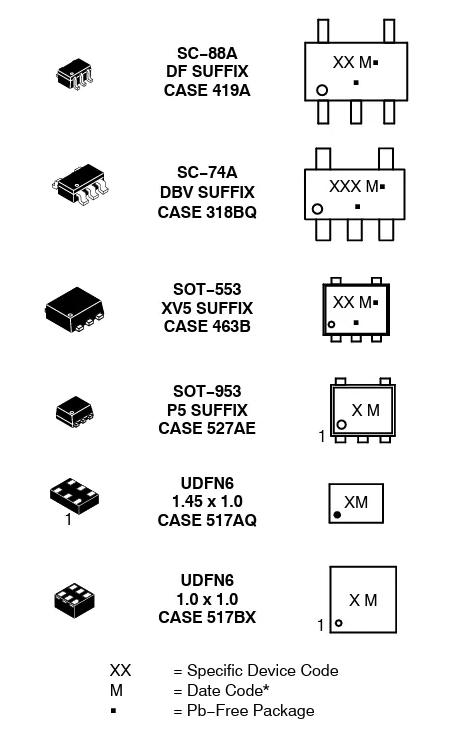

安森美 (onsemi) NL17SZ07缓冲器是高性能的单通道非反相缓冲器,具有开漏输出,工作电压范围为1.65V至5.5V。这些缓冲器的输入/输出过电压容差高达5.5V。NL17S

时钟缓冲器的应用场景及如何选择合适的时钟缓冲器?

时钟缓冲器广泛应用于各种电子系统中,以下是一些典型的应用场景:1.通信设备:在高速通信设备中,时钟信号的质量直接影响数据传输的准确性。时钟缓冲器通过优化信号完整性,确保通信系统的稳定性和可靠性。2.

时钟缓冲器在现代化建设中的作用

时钟缓冲器作为现代电子技术中的一项关键元件,其在信息化建设和智能化发展中所扮演的角色日益凸显。随着社会的不断发展,人们对信息传输的速度和准确性要求越来越高,时钟缓冲器以其独有的功能,确保了数据传输

缓冲器的工作原理及它的作用

缓冲器的工作原理及它的作用

评论