1. 前言

在数字电路课程中,老师在讲组合逻辑的时候,一般都会讲竞争与冒险。sky当时也听的云里雾里,没有想清楚如下问题:

1) 竞争与冒险究竟是什么东西?有啥物理现象?

2) 在数字电路设计中,什么时候需要关心(分析)竞争与冒险?

3) 如何避免竞争与冒险导致的问题呢?

经过多年实际工作的实践与理解,在此文略作分析。

2. 竞争与冒险的产生

在数字电路中,调用一个AND gate,用verilog可以如下描述:

assign out = in0 & in1;

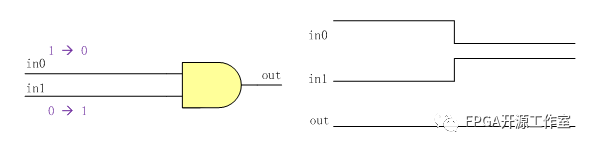

其综合后对应的电路与波形如下:

如果in0/in1分别有1--》0/0--》1的变化,如果同时满足如下两个条件:

1) in0/in1同时变化;

2) 从in0/in1的driver到AND gate的delay绝对匹配;

则,AND gate的输出端不会有毛刺,一直稳定的输出logic 0。

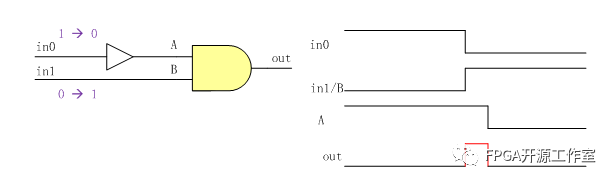

但是在实际电路中,经过place & route后,如上两个条件基本不能满足。抽象简化后,实际电路和波形如下:

可以看到,由于in0/in1到AND gate输入pin上delay的不匹配,导致AND的输出out出现一个logic 1的小脉冲,一般也叫毛刺(glitch)。

对于一个简单的AND gate,就会产生毛刺;那么对于一个更复杂的电路,比如:加法器,乘法器,glitch更是起起伏伏,直到一定的时间后,才会输出稳定的值。

这就是信号的竞争与冒险:逻辑上(真值表)输入的变化本来不会导致组合逻辑输出的变化;但是因为在输入逻辑gate的PIN上,输入信号变化时间上的差异,导致组合逻辑的输出端产生一些不必要的0--》1/1--》0变化,出现glitch。

3. 竞争与冒险分析

A. 对于同步电路(比如DFF的clk是同一个信号),我们需要分析(关心)竞争与冒险吗?

答案是不需要。

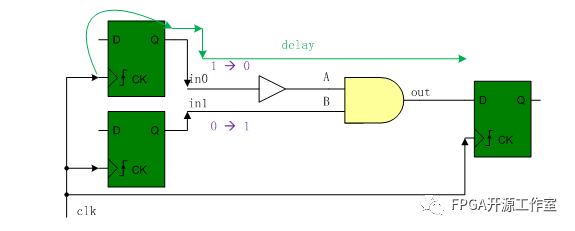

在实际同步数字电路中,组合逻辑通常伴随时序逻辑(DFF等),其结构如下图:

因为在同步电路中,我们会做STA时序分析,计算每条path的delay(如上图绿色线)。AND gate在各条path的最大delay后,out PIN上的信号是稳定不变的。再分析后级DFF是否满足setup/hold timing需求,则后级DFF一定采样到out PIN上稳定的输出值,而非中间的glitch。

也就是说:在同步电路中,我们利用STA分析,已经把out PIN产生glitch的期间给滤除(mask)掉了;只要后级DFF的setup/hold timing分析pass,则后级DFF肯定采样到正确的逻辑计算值,不会采样到毛刺。

B. 对于异步电路(比如DFF的clk不是同一个信号),我们需要分析(关心)竞争与冒险吗?

答案是需要。

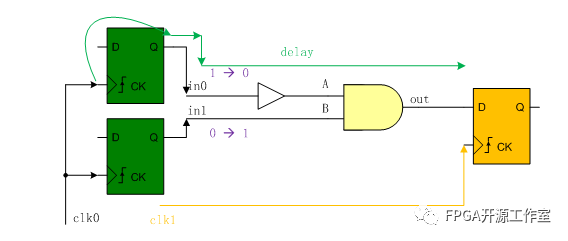

在实际异步数字电路中,组合逻辑也通常伴随时序逻辑(DFF等),其结构如下图:

在异步电路中,我们在做STA时序分析,会有困难。虽然我们仍然能准确计算每条path的delay(如上图绿色线),但是我们无法预知clk0/clk1的相位(phase)关系,导致无法分析后级DFF的setup/hold time,即:我准确计算out PIN在glitch产生期间是否会有clk1的上升沿。在工程实践中,一般是设置:set_flase_path -from clk0 -to clk1。这样,后级DFF(图中橙色DFF)可能会采样到毛刺。

这时,我们就得关心glitch了,即竞争与冒险。

不是说了不能计算了吗?那怎么“关心”呢?

既然不能计算,就从电路结构上解决问题:

通过增加一个clk0 domain的DFF,让clk0--》clk1的数据交互是DFF输出,是不是就肯定不会有glitch啦 ^_^。“out_reg”PIN是DFF输出,不会有glitch的。

啊,讲到这儿,是否突然明白,老师讲:跨时钟域时,信号一定要DFF的Q端直接输出。

C. 还有哪儿需要分析(关心)竞争与冒险吗?

当然是有的。

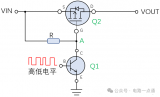

比如:chip IO上的异步信号。比如IIC接口的SCL/SDA。这2信号在chip输出时,是不是应该(必须)用DFF输出呢?不能搞组合逻辑输出,否则接收方chip可能看到SCL上的glitch,导致功能错误。

4. 总结

综上:

1) 在同步电路中,我们并不关心竞争与冒险,因为有STA做保障;

2) 在异步电路中,我们关心竞争与冒险(从电路结构解决问题),因为没有STA做保障;

编辑:jq

-

同步电路

+关注

关注

1文章

61浏览量

13781 -

STA

+关注

关注

0文章

52浏览量

19622 -

SCL

+关注

关注

1文章

244浏览量

18068

原文标题:数字IC/FPGA设计基础_竞争与冒险

文章出处:【微信号:bianpinquan,微信公众号:变频圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

JH7110 什么时候支持 Vulkan API?

门控时钟(Clock-gating)介绍

掌握数字设计基础:迈向芯片设计的第一步

高速数字电路设计与安装技巧

最全的硬件工程师笔试试题集

如何学好电路设计?(文末分享电路设计资料合集)

数字电路设计中什么时候需要分析竞争与冒险

数字电路设计中什么时候需要分析竞争与冒险

评论