实时图像处理系统的显著特点是数据量大,有效地处理和传输图像数据是实现实时图像处理系统的关键,TI公司推出了高性能多媒体双核处理器OMAP5910,是将高性能、低功耗的TMS320C55x DSP与控制性能很强的ARM925微处理器集成到同一芯片器件中如何有效地发挥双核的优势,合理利用OMAP5910的各种内存配置DMA控制器实时、高效传输大规模的图像数据是本文研究的重点。

1 OMAP5910的内存管理

由于OMAP5910支持多种内存,因此在设计DMA传输方案时,必须对OMAP5910的内存管理有一个详细的了解。

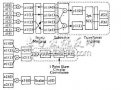

OMAP5910的MPU存储器片内集成了192KB的SRAM,DSP存储器片内集成了64KB的双向DARAM,96KB的单向SARAM,32KB的程序存储器PDROM,MPU和DSP子系统的存储器映射情况如图1所示。通过EMIFF和EMIFS接口,OMAP5910可以访问片外存储器,但访问片外存储器的速度与访问片内存储器的速度差别很大。

OMAP5910的片内存储器主要由存储器管理单元TC管理。TC管理MPU、DSP、DMA以及局部总线对OMAP5910系统存储资源(SRAM、SDRAM、Flash、ROM等)的访问,它的主要功能是确保处理器能够高效访外部存储区,避免产生瓶颈现象而降低片上处理速度,TC通过3种不同的接口-EMIFS、EMIFF或IMIF,支持处理器或DMA单元对存储器的访问。其中EMIFS接口提供对Flash、SRAM或ROM的访问,EMIFF接口提供对SDRAM的访问,IMIF接口提供对OMAP5910片内192KB SRAM的访问,3种接口是完全独立的,从任何一个处理器或DMA单元都可以同时访问。

ARM核访问DSP核的数据或内存空间,需要ARM和DSP之间进行通信,主要有3种方式支持内部双核间的通信,第1种方式通过双核共享邮箱寄存器MailBox来实现,ARM和DSP均可以通过MailBox触发对方中断,并同时传递两个16位的参数,以通知对方自己的状态或传递某种请求,第2种方式是MPUI方式,ARM通过主机接口获得对DSP存储空间和I/O空间的访问权,由ARM完成数据在双核间的搬移,第3种方式是设置DSP的MMU,将DSP的外部存储空间映射到OMAP5910系统存储资源中,共享DSP的地址空间,由DSP完成双核间的数据搬移。

2 OMAP5910的DMA控制器

OMAP5910的DMA控制器对实时图像处理系统非常重要,它可以在没有CPU参与的情况下完成映射存储空间中数据搬移,灵活的使用DMA控制器可以大大提高数据传输效率。

OMAP5910的DMA控制器进行通用功能传输时的特点如下:

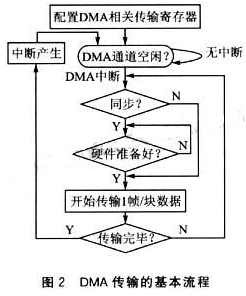

1)单通道分割操作,具有通用和专用信道,不同的硬件资源端口。所有的数据交换都通过请求(Request)、准备就绪(ready)、中止(abort)信号进行握手。DMA信道是时分复用的,其传输的基本流程如图2所示。

2)多帧传输。传输的每个数块可以有多个数据帧。传输的数据大小为8位、16位和32位。可按字节打包、拆包、并对传输的字节计数。可访问所有的存储器地址空间(物理地址映射和I/O空间)。

3)DMA的读、写和帧操作都有中断触发,每个DMA物理通道都可以产生一个中断,使处理器对本次传输的状态作出反应,所有的DMA中断都是电平中断。

4)后台传输、高吞吐率,DMA可独立于CPU工作和以PCU时钟速度进行数据吞吐。

实时图像处理系统的图像数据很大,同时图像处理过程中也也会产生大量的中间数据,而OMAP5910的片内资源有限,不能容纳帧的图像数据和中间数据,所以大量的图像数据必须存储在片外存储器中,为了保证系统的实时性,由DMA负责完成数据在不同存储空间的搬移,不必占用CPU的时钟周期,避免CPU大部分时间堵塞在对外存的访问上,同时DMA对数据重排功能可以优化图像数据在内存中的存储,这不仅可以提高内部存储空间的利用效率,而且可以提高数据的传输速率。

3 OMAP5910内、外存储器数据交换分析

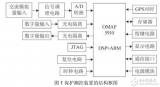

一个完整的实时图像处理不仅能对图像进行实时采集,还能对图像进行实时处理,该实时图像处理系统主要由图像传感器、A/D转换器,复杂可编程逻辑器件FPGA、OMAP5910双核处理器,图像显示设备等构成。该系统的主要功能是FPGA实时接收红外焦平面阵列传感器输出的14位视频信号,降频后由OMAP5910的DSP处理器执行图像处理算法,同时,OMAP5910的ARM处理器执行复杂控制指令,再由FPGA缓存,经D/A变换合成10位视频信号输出,另外,OMAP5910的ARM处理器通过接口接收计算机的控制指令。

按照人眼的视觉要求,成像系统每秒钟至少要采集和处理25帧图像数据,才能避免图像实时显示时的视觉闪烁感,。对于320×240的点阵图像,A/D为14位,每帧采集数据为320×240×14位=1 MB,按实时性的要求,进行处理和显示数据的速度为320×240×14

位×25帧/s=3.125MB/s,即需要在64μs内完成读1行(320像素)和写1行(346象素)的操作,只有这样图像才不失连续性。

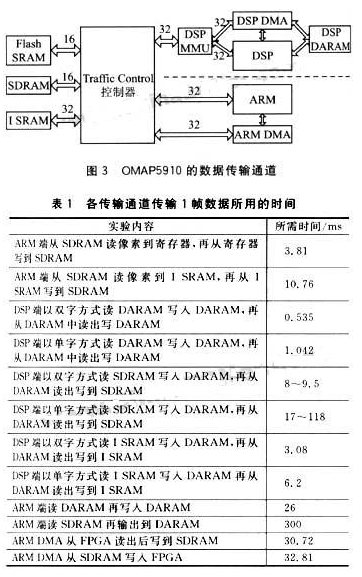

为了保证图像处理和显示的实时性,应充分利用OMAP5910的各数据传输通道,OMAP5910的片内、外存储器的数据传输,如图3所示,图中给出了OMAP5910处理实时图像时的所有数据传输通道,他们的传输速率与存储器的类型有关。为了充分认识OMAP5910的数据传输通道的性能,笔者做了一系列的实验,设置系统时钟为150MHz,工作模式设为全同步模式,使能Ca che的前提下,详细测试了各传输通道传输1帧数据所用的时间,如表1所列。以此为依据来优化数据的传输。

4 DMA方式数据传输优化方案

在详细分析各数据传导的数据传输速率性能的基础,本文提出了一种DMA方式的数据传输优化方案,把整帧划分成多个块,OMAP5910待处理的图像数据完全放在OMAP5910的片内数据存储器中进行处理,既减少了与外存的大量交互,又充分利用了片内的高速存储资源,在内外存之间的数据传输使用DMA在后台进行操作,大大提高OMAP5910的工作效率。

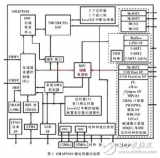

4.1 数据流程

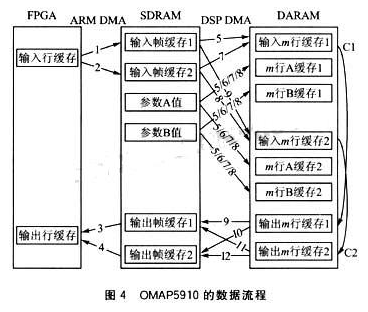

A/D采样的数据首先存放在外部缓冲中,当采集到一定的数据量后,由复杂可编程逻辑器件触发ARM DMA读取数据,依次输入两帧图像保存在SDRAM中,从外挂Flash中取得进行图像处理所需的参数A、B值保存在SDRAM中,与输出帧存以8行为块单位,触发DSP DMA将块数据从OMAP5910的外部缓存区SDRAM搬运到DSP核的双向内部缓存区DARAM,以供DSP核进行计算。有关DMA方式传输的特点,DSP核进行计算的同时,DSP DMA搬运上一块的图像数据(8行)到SDRAM,ARM核接收到输出行数据后,触发ARM DMA把数据搬移到FPGA控制外部存储区,数据流程如图4所示。

由于OMAP5910内部和外部都采用双缓冲机制,因此ARM核和DSP核处理的DMA传输上一帧数据的同时,不影响DMA进行当前帧数据的传输。这样整个系统中A/D数据的采集,DMA数据的传输及CPU数据的计算达到了高度的并行性。

4.2 操作时序

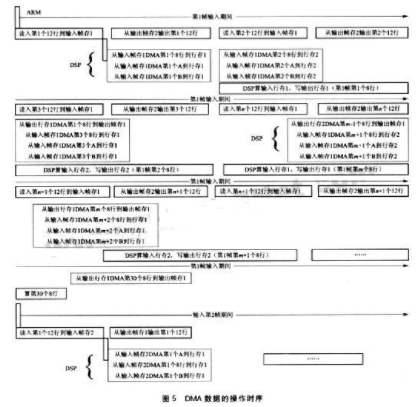

从数据传输的操作时序上,可以看出该优化方案另一个优势,将原来的几个输入过程(每个输入过程指的是输入1行像素)合并为1个输入过程(1次输入几行像素),并且将原来集中完成的输出过程分散到输入过程中间完成,进一步提高的性能。

具体配置操作为:OMAP5910中ARM DMA读过程1次输入12行数据,用20次将1帧图像输入到SDRAM中。ARM DMA的写过程在读过程中间启动。即1帧中的第1次DMA读过程结束的中断中启动行号和帧号的添加以及 DMA的写过程,这一次只写2行,在1帧中的第2次到第20次DMA读过程结束的中断中启动写过程,每次写15行,其操作时序图5所示。

具体的时间计算是:读12行数据为17.07μs×12=204.84μs,写15行数据为27.68μs×15=415.2μs,1次读写及中断的处理所需时间为204.84μS+415.2μs≈700μs,1次读写及中断的处理允许时间为68μS×12=816μs。经计算700μ<816μs,能够保证实时图像处理系统的实时性。

5 优化方案中的代码设计与实现

5.1 ARM端的主程序

ARM核主要实现OMAP5910系统的配置,与FPGA接口的数据输入/输出,与SDRAM的数据保存、帧模式的控制与转换等优化方案的功能。

5.2 DSP端的主程序

DSP核主要实现DSP DMA在I SRAM和DARAM之间

数据的输入/输出,红外图像的两点校正算法和疵点剔除等算法,以及红外图像的亮度和对比度参数的计算等功能。

5.3 调试与配置DMA通道的经验总结

1)测试DMA通道的数据传输是否正确,可编写SDRAM到SDRAM的内部DMA数据搬移测试程序来初步测试DMA通道的初始设置和数据传输是否正确。

2)测试DMA与FPGA接口数据的传输速率,示波器读取读信号或写信号的效率时,应注意查看读信号和写信号的个数是否是传输数据的个数。

3)测试DMA的外部中断,外部中断的引脚是复用引脚,应提前设置此引脚。

4)测试DMA操作的读操作和写操作的相互配合,查看输出的传输是否正确。

5)使用指定内存不同的数据测试视频图像的输出是否正确。

6)DMA中断的触发事件是上升沿有效。

7)为保证DMA传输数据的完整性,要对DMA的优先级进行设置。

结语

实时图像处理系统实现了此数据传输的优化方案,实时显示图像的速度为25帧/s,图像的视觉效果比较理想,通过灵活地控制DMA,不仅能够提高图像数据的传输效率,而且能够充分发挥OMAP5910的高速性能。

责任编辑:gt

-

处理器

+关注

关注

68文章

20339浏览量

255323 -

dsp

+关注

关注

561文章

8277浏览量

368421 -

存储器

+关注

关注

39文章

7758浏览量

172268

发布评论请先 登录

蓝牙模块和OMAP5910的接口技术

基于OMAP5910的低压保护测控装置设计

什么是双内核嵌入式处理器OMAP5910?在3G的多媒体中有哪些应用?

开放式多媒体应用平台OMAP5910双核程序装载方法

基于双核OMAP5910的嵌入式系统及其应用

多媒体应用平台OMAP5910双核通讯技术

基于Omap5910平台的并行JPEG压缩算法

多核处理器OMAP5910的介绍及其低压保护测控装置的设计

ARM与DSP双核组成的OMAP5910嵌入式系统分析

基于OMAP5910双核处理器实现实时图像处理系统的应用设计

基于OMAP5910双核处理器实现实时图像处理系统的应用设计

评论