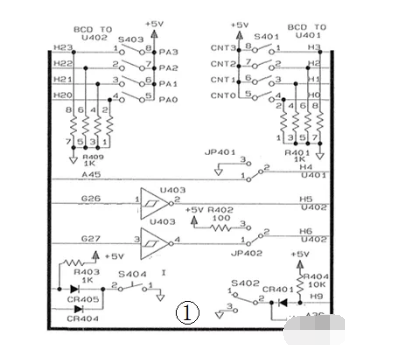

HARRIS固态化10KW电视发射机的主控器中,设计了两块电可擦除程序逻辑电路U401和U402,发射机运行所需要的各种逻辑程序就固化在内部电路中。为了适应电路的需要,在U401和U402的外围安装了各种跳接片和编码开关,它们的具体设置方法如下:

编码开关S401,用来设置前面板上显示被测量参数的数量。这个拨码开关设置的二进制数字,要比前面板发光二极管数目少一个。例如,前面板上共有7个需要测量的参数,设置二进制数字就是7-1=6,也就是0110,如图1所示。

校正开关S402的作用,是转换测量模式。用S402可以把入射功率取样信号校正成反射功率。把S402拨到校正CALIBRATE位置时,驻波比过载功能失去作用,驻波比故障指示灯闪烁,出现禁止操作发射机的告警信号。同时,经过二极管CR401,把这种状态送到了微处理器U401的10脚,发出驻波比校正命令VSWR-CAL。S402没有返回到正常状态之前,微处理器一直保持本地操作LOCAL这种模式。把S402拨到校正位置,就是2、3脚连接成低电平。通过地址线A39,控制继电器K401吸合。它的4个触点7、10、9和8接地,地址线A21、A28、A29和A30把低电平信号送到了驻波比测量电路。电压比较放大器U507和U510,非常灵敏地把测量因数减低了10倍。已经校正好的入射功率取样电压,可以在这个时候加到反射功率取样输入端。调整反射功率取样校正电位器,让反射功率取样电压低于入射功率取样电压的10倍,就等同于驻波比1.92:1。

S403设置允许出现故障的模块数量:在发射机中,如果一个模块出现了故障,就会丢失部分功率。但是,发射机自身设计了自动增益控制系统AGC,依靠这个AGC环路,能够补偿模块丢失的功率。如果多个模块出现了故障,AGC系统就要提高驱动电平,而且要增加到超出正常电平很高的状态。这个时候,出现故障的模块一旦复位,AGC系统却不能立刻反应过来,把驱动电平降到原来的水平,就会出现过驱动故障,损坏其它模块。为此,控制器中安装了驱动封锁电路,让驱动电路在这种情况下,跟随故障模块恢复的比率,提高驱动电平,保护模块。在主控制电路1A3B中,用S403设置输出电路封锁之后允许存在故障的图像功放模块数量,也就是可以在封锁解除后重新复位恢复正常的模块数量。如果出现故障的模块数量超出了设置的数字,系统复位后,控制器仍然封锁激励器的输出。出现故障的图像驱动模块、伴音驱动模块和伴音功放模块,它们复位后,也会引起驱动封锁现象,但它们不受S403的影响。

S404是一个轻触按钮开关,用来测试前面板发光二极管是否正常。按下S404,发射机控制柜前面板的测量指示灯都应该点亮,而且测量选择发光二极管也必须循环闪亮。

跳接片JP401拨到1、2位置时,1ATB1-3的互锁信号就通过光电耦合器U205、去抖动电路U206的14、2脚和地址线A45,送到微处理器U401的59脚和U402的66脚。互锁回路形成,允许操作发射机;解除互锁,发射机关闭,开机命令不起作用。当JP401的2、3脚连接时,外部互锁电路形成的互锁信号不能到达微处理器U401,但是送到了微处理器U402的66脚,制约着模块的运行。当跳接片JP402在1、2位置时,表示发射机使用了PS1和PS2两块电源。JP402在2、3位置时,说明发射机只安装了一块电源。

跳接片JP403位于图纸的最右下端,1、2脚相连时,表示一个5KW功放柜,用二极管选通电路连接着主、备两块+50V电源。低波段二频道10KW电视发射机,配置了两个+50V电源,左、右功放柜各自使用对应的电源。只有驱动模块,利用二极管选通电路,同时由两个+50V电源供电。其它配置模式下,把JP403的2、3脚连接即可。

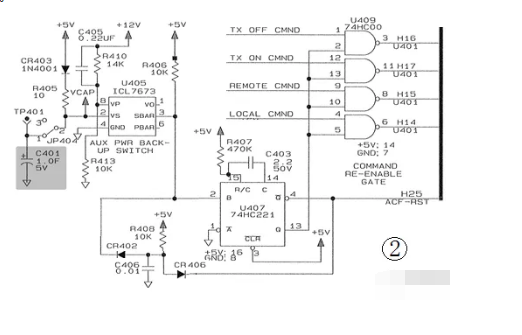

记忆电路:电可擦除程序逻辑控制器U401和U402的逻辑程序,已经固化在集成电路内部。U401的逻辑图是843-5285-275;U402的逻辑图是843-5285-352。在控制器逻辑电路图2中,有一个容量为1.0F的电容C401。它的作用是,交流电源停止供电时,输出一个+5V的直流电源,给记忆电路供电。正常运行时,U410构成了双稳态多谐振荡器,这里面储存着发射机开机命令、关机命令、遥控操作和本地操作命令。发射机没有交流电源供电期间,电容C401上储存的电能,由于给记忆电路供电导致了电压下降。

C401上的电压下降了300mV时,电源监测器U405就能够监测到,3脚转换成低电平。经过二极管CR402把这个逻辑电平送到了U408的2、5、10和13脚,防止逻辑转换并保持目前这种逻辑。C401上的电能大约能维持4天,在此期间,发射机储存在U408和U410种的信息一直保留着,直到交流电源恢复或者再次给C401充足电能为止。一旦发射机加上交流电源,C401通过CR403和R405自动加上+5V电压,U405的3脚变成高电平。U407产生一个1s的脉冲,打开U409的逻辑门电路,把储存在U410中的逻辑加到发射机中。交流电源停电恢复后,或者+50V电源故障恢复时,发射机仍然执行故障发生前的命令。正确地设置编码开关和跳接线,就能保证发射机运行在最佳工作状态。

责任编辑人:CC

-

逻辑电路

+关注

关注

13文章

503浏览量

44265 -

发射机

+关注

关注

7文章

531浏览量

49337

发布评论请先 登录

异步时序逻辑电路

固态发射机的控制和保护系统的设计

时序逻辑电路分析有几个步骤(同步时序逻辑电路的分析方法)

一文详解芯片的逻辑电路

时序逻辑电路的分析方法

一文知道发射机程序逻辑电路的设置方法

一文知道发射机程序逻辑电路的设置方法

评论