FPGA的MultiBoot功能可以支持远程动态更新bitstream images,实现bitstream images的实时切换。在MultiBoot配置过程中检测到错误时,FPGA可以触发fallback 功能,以确保可以将已知良好的设计加载到器件中。

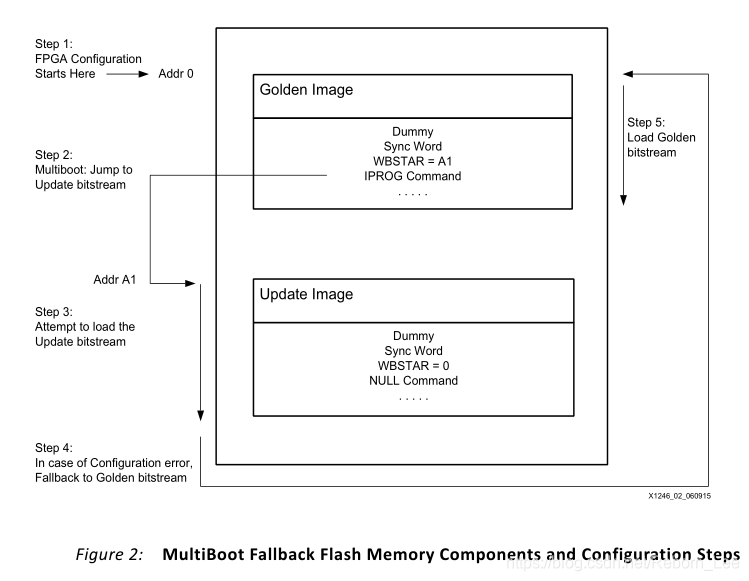

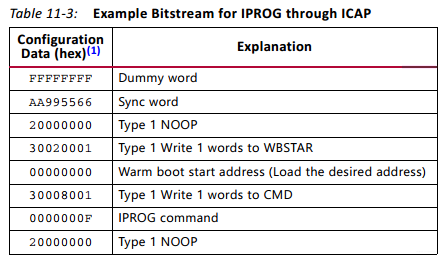

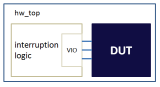

MultiBoot的大致过程如下图:

MultiBoot的配置文件由两个比特流文件生成,第一个为备份文件,永远都不会变,称为Golden_image,从Flash的0地址存储。

第二个为更新文件,后面远程更新,更新的就是这个文件,称为Update_image,存放在某个地址处,这个地址有热启动地址寄存器(WBSTAR)指定。

配置过程大致如下:FPGA从FLASH的0地址处读取配置,遇到IPROG Command命令时,跳转到WBSTAR寄存器指定的地址,该地址存放Update_image的地址,此时FPGA尝试加载该地址处的比特流文件,配置成功的话,就执行该配置的功能。如果遇到配置错误,则触发FallBack,FPGA重新加载Golden_image。

1、ICAPE3 接口

FPGA实现IPROG通常有两种方式,一种是通过ICAP配置,一种是把相关指令嵌入bit文件中。与通过bit文件实现IPROG相比,通过ICAP更灵活。

在Xilinx FPGA 中ICAP(Internal Configuration Access Port) 指的是内部配置访问端口,其主要作用是通过内部配置访问端口(ICAP),用户可以在FPGA逻辑代码中直接读写FPGA内部配置寄存器(类似SelectMAP),从而实现特定的配置功能,例如Multiboot。

ICAP目前为止有三个版本,包括ICAP,ICAPE2以及ICAPE3。UltraScale系列对应ICAPE3,7系列对应ICAPE2,7系列之前的对应ICAP。

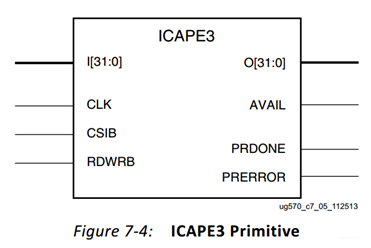

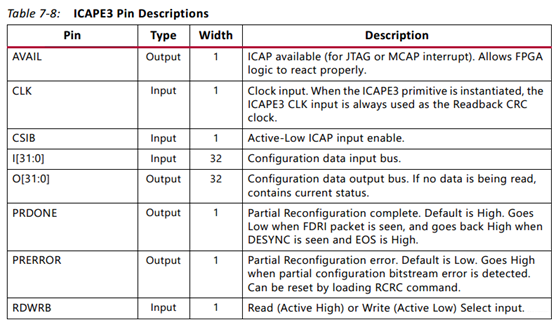

以下以ICAPE3 为例,ICAPE3 的接口如下:

2、IPROG指令

每个UltraScale系列的FPAG包括2个ICAPE3,但实际使用时只能例化并使用一个,默认顶部ICAPE3, 初级玩家采用默认的即可。

IPROG指令的作用跟外部Program_B管脚的作用类似,都是对FPGA芯片进行复位操作,该复位操作对FPGA内部的应用程序进行复位,复位过程中除专用配置管脚和JTAG管脚,其他输入/输出管脚均为高阻态,同时IPROG指令不能复位专用重配置逻辑,如WBSTAR寄存器、TIMER寄存器、BSPI寄存器和BOOTSTS寄存器。IPROG指令能够触发FPGA开启初始化流程,同时拉低INIT和Done信号。完成复位操作后,将默认的加载地址用热启动地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址替换。

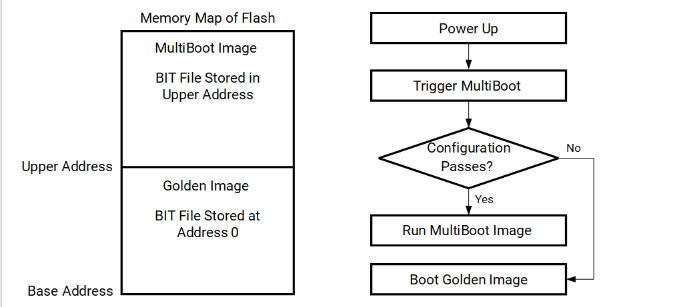

通过ICAP发送IPROG指令实现Multiboot的步骤如下:

首先写入同步头 32’hAA995566, 然后将需要跳转到的bit文件的起始地址写入WBSTAR寄存器,最后写入IPROG(internal PROGRAM_B)指令。

WBSTAR寄存器的格式,根据自己的要为Update_image分配在FLASH的地址,按照下面的格式生成一个32位数据。例如,我为Update_image分配的flash地址为2000000。

(1)对于BPI模式来说,可以通过RS[1:0]来控制具体位流的读取,也可以通过STAT_ADDR[28:0]地址来控制具体位流的读取。

(2)对于SPI模式来说,只有STAT_ADDR[23:0]地址来表征FLASH器件的地址,当使用32位地址的SPI(容量大于等于256Mb)时,需要将实际存储的高24地址赋值给STAT_ADDR[23:0]。因此在位流存储的起始地址早于255时,这就要求位流中的dummy数目要大于256个,否则就会出现易失部分有效位流读取,导致加载失败。为了安全起见,在使用大于等于256Mb的FLASH时,可以适当在位流头前加入Dummy。

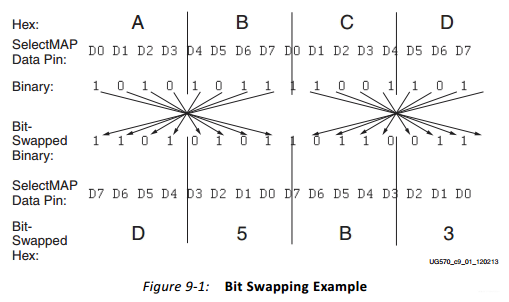

这里需要注意一点,ICAP以及SelectMAP都存在位反转(Bit Swapping),也就是说,上表中所有的数据需要进行位反转之后才能接到ICAP的输入接口,同理,ICAP输出的值需要进行位反转后才能与实际的值对应起来,位反转的示例如下图。

3、ICAPE3 例化示例

ICAPE3 进行例化,示例如下:

// ICAPE3: Internal Configuration Access Port

// UltraScale

// Xilinx HDL Language Template, version 2019.1

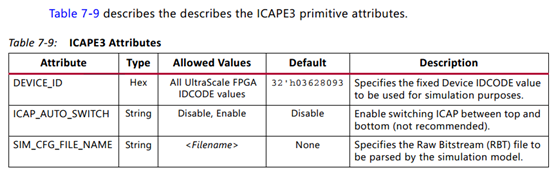

ICAPE3 #(

.DEVICE_ID(32‘h03628093),//pre-programmed Device ID value,used for simulation

// purposes.

.ICAP_AUTO_SWITCH(“DISABLE”),//Enable switch ICAP using sync word

.SIM_CFG_FILE_NAME(“NONE”)//Raw Bitstream (RBT) file,parsed by the simulation

// model

)

ICAPE3_inst (

.AVAIL(AVAIL), // 1-bit output: Availability status of ICAP

.O(O), // 32-bit output: Configuration data output bus

.PRDONE(PRDONE),//1-bit output: Indicates completion of Partial Reconfiguration

.PRERROR(PRERROR),//1-bit output: Indicates Error during Partial Reconfiguration

.CLK(CLK), // 1-bit input: Clock input

.CSIB(CSIB), // 1-bit input: Active-Low ICAP enable

.I(I), // 32-bit input: Configuration data input bus

.RDWRB(RDWRB) // 1-bit input: Read/Write Select input

);

// End of ICAPE3_inst instantiation

其中设备号DEVICE_ID需要查找USER GUIDE手册,而ICAP原语接口时序跟Select Map接口时序非常相似。SelectMap模式下,FPGA的配置和回读是通过CSI_B,RDWR_B和CCLK来控制的。

4、程序步骤

在发送IPROG指令之前,将默认的加载地址用热启动地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址。

然后对ICAP核进行预配置。重载控制模块在收到触发信号后,第一个时钟周期将ICAP核的RDWRB信号和CSIBCSIB信号置高,第二个周期将RDWRB信号置底,CE信号置高,第三个周期将RDWRB信号置底,CSIB信号也置底。

接着在下面的8个时钟周期里,将指令队列中的控制命令逐个发出。

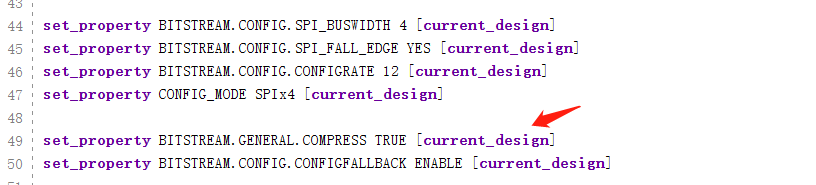

运行工程,生成位流Bit,在约束XDC文件中添加压缩等命令即可。

固化Mcs生成。Xilinx系列的FPGA需要将后缀名为mcs的内存镜像文件固化到外部配置存储器中,FPGA上电后才能自动加载配置文件。一般的mcs文件只包含一个bit流文件,多重启动的mcs固化文件包含多个bit流文件。在将多个bit流整合到mcs文件的过程中,需要指定每个bit流的起始地址,这样FPGA专用配置逻辑才能根据地址找到对应的bit流。在程序设计WBSTAR地址时,确定了Golden位流存储的起始地址为0X00000000,Update位流存储的起始地址为0X00800000,因此在将Bit整合到Mcs过程中需要指定对应的存储起始地址,否则就无法加载成功了。

在SPI的flash里烧写有A和B两个程序,FPGA上电后,自动加载A程序,根据外部给FPGA指示信号,FPGA自动切换加载B的程序,同时在B程序运行期间,根据外部给FPGA指示信号,FPGA自动切换加载A的程序。

原文标题:FPGA中利用ICAP原语实现Multiboot功能

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1664文章

22504浏览量

639291

原文标题:FPGA中利用ICAP原语实现Multiboot功能

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera Agilex FPGA与SoC实现更智能的AI

Xilinx FPGA输入延迟原语介绍

【ALINX 教程】FPGA Multiboot 功能实现——基于 ALINX Artix US+ AXAU25 开发板

为什么在FPGA设计中使用MicroBlaze V处理器

如何使用FPGA实现SRIO通信协议

在FPGA设计中集成事件断点的实现过程

以太网通讯在FPGA上的实现

基于FPGA平台的蜂鸟E203 JTAG debug出错问题的解决思路

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

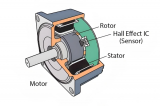

使用Verilog在FPGA上实现FOC电机控制系统

FPGA在机器学习中的具体应用

如何使用FPGA通过CYUSB3014连接U盘?

PLL技术在FPGA中的动态调频与展频功能应用

在FPGA中如何通过ICAP原语实现Multiboot?

在FPGA中如何通过ICAP原语实现Multiboot?

评论