“IIC 协议与编程序列” 一文,我们为内部集成电路 (IIC) 协议的初学者们提供了有关该协议基础知识和编程序列的详细解释。

在本篇博文中,我们将探讨有关 AXI IIC 和 PS IIC 的自调试技巧。

PS IIC 编程序列调试:

控制器设置为 “主发射器 (Mastertransmitter)”。

在 Zynq-7000/Zynq UltraScale+ 器件中启用 PS IIC。确保 SCL 频率配置为 100 kHz 或 400 kHz。

设置主发射器控制器的控制寄存器。

检查中断是否已清除,并且已配置实际 SCL 的时钟分频器。

要测试与从设备的通信,请将从地址写入 PS I2C 地址寄存器 (I2C_Address),然后将数据写入 I2C_data_reg

HOLD 位应根据数据大小来处理。当数据大小小于 FIFO 深度时,请清除 HOLD 位以终止事务传输,并生成 STOP 位。

在中断使能寄存器 (IER) 中使能 NACK 中断后,即可通过 ISR 来监控从设备应答 (ACK)。

验证 ISR 中的 COMP 标记位已置位。这样即可确认数据传输成功。

如果主传输不成功,用户可使用以下步骤进行调试:

确保控制寄存器中的配置正确无误

检查 ISR 中的 NACK 位,以确认从设备的响应

按上述方式谨慎处理 HOLD 位。否则,将导致 SCL 下拉直至超时为止

监控状态寄存器中的 TXDV 位,检查是否有任何暂挂数据正在等待传输

状态寄存器中的“总线繁忙 (Bus busy)”位或 BA 位将有助于您了解数据传输期间的总线状态。

控制器设置为 “主接收器 (Masterreceiver)”

与对应主发射器的步骤 1 相同,在 Zynq-7000/Zynq UltraScale+ 器件中启用 PS IIC。确保 SCL 频率配置为 100 kHz 或 400 kHz。

使用软件应用来设置主接收器控制器的控制寄存器。

与对应主发射器的步骤 3 相同,检查中断是否已清除,并且已配置实际 SCL 的时钟分频器。

将读取数据计数填入 PS IIC 的传输大小寄存器。如果传输大小大于 FIFO 深度,则启用 HOLD 位。

将地址写入从地址寄存器

等待数据接收完成,可通过检查状态寄存器的 RXDV 位来确认。

如果 RXDV = 0 且 ISR 中有任意中断位处于置位状态,则停止传输并报告错误。

同样,如果 RXDV = 1 且 ISR 中有任意中断位处于置位状态,则停止传输并报告错误。

如果 RXDV=1 且未报告任何错误,则从 FIFO 读取数据,直至状态变为 RXDV=1 为止。如果尚未完成接收的剩余数据(来自从设备)小于 FIFO 深度,则清除 HOLD 位。

等待 ISR 中的 COMP 位变为置位状态以完成传输。

以上对应编程序列的调试步骤适用于默认轮询方法。

如果对主接收器使用中断方法,则存在如下差异:

您需要在数据传输前启用中断

无需监控 RXDV 位,而需检查 ISR 中的 DATA 位。

常见问题解答

在 IIS 中,何谓“超时”?

如果在任何时间点上,主设备或接入的从设备将 SCL 时钟信号置于低位,且时间超过超时寄存器中指定的时间段,则会生成 [TO] 中断位以避免出现停滞状况。

如何将 PS IIC 复位?

寄存器 RST_LPD_IOU2 位 9 和 10 用于复位控制器

支持哪些模式?

主设备模式、从设备模式以及多重主设备模式。

注:在多重主设备模式下,所有主设备中的 SCL 频率需保持相同。

支持哪些频率?

仅支持 100 kHz 和 400 kHz。

用户如何检查总线错误?

在 ISR 寄存器中,监控总线上是否存在 ARB_LOST、NACK、RX_OVF 和 RX_UNF 错误。

如何区分 DATA 标记与 COMP 标记?

在 ISR 寄存器中,对应每读取 14 字节数据,DATA 位就有一个触发器,而 COMP 位则用于指示传输完成。

PS IIC 遵循何种规范?

NXP 规范UM10204

支持的最大数据发射率是多少?

255 个字节

AXI IIC 编程序列调试:

用户可以使用以下读写操作来调试 AXI IIC IP,以了解协议是否正常工作。

快速获取结果的首选选项是使用“动态”编程进行调试。

动态读取操作:

此操作的最终目的是从从设备中读取单一寄存器,以证明主从设备的功能是否正常。

使用写入操作将 START + 从设备地址一起写入 TX FIFO

将从设备的子寄存器地址写入 TX FIFO

使用读取操作将 RE-START + 从设备地址一起写入 TX FIFO

将 STOP + 要从从设备读取的字节数一起写入 TX FIFO

使用控制寄存器来启用控制器

轮询 RX_FIFO_EMPTY 的状态寄存器,以查看数据接收状态(如果 RX_FIFO = 0,则数据已进入接收 FIFO 内)

如果 RX FIFO 中无数据,且 RX_FIFO_EMPTY 为 1,则可遵循以下步骤来了解问题:

如果由于从设备不响应而导致无法接收数据,那么原因可能是指定地址不存在任何从设备。请复查从设备地址是否正确。

如果您确认从设备地址正确无误,请探测 SCL/SDA 以了解是否正在从从设备生成 ACK。

如果有来自从设备的 ACK,请以相同方式检查子寄存器,以对通信进行调试。

检查 TX_FIFO_Empty 标记,确认是否所有数据都已完成发射。

如果步骤 6 中未发现任何问题,则表示您可从从设备接收数据,请检查是否已建立通信。

动态写入操作:

使用写入操作将 START + 从设备地址一起写入 TX FIFO

将从设备的子寄存器地址写入 TX FIFO

将除最后一个字节外的所有数据字节都写入 TX FIFO

将 STOP + 最后一个数据字节写入 TX FIFO

使用控制寄存器来启用控制器

轮询 TX_FIFO_EMPTY 的状态寄存器,以判定数据发射状态(TX_FIFO_Empty = 1 表示数据发射已完成)。

如果用户想要检查写入操作是否正确,可通过以下步骤来进行调试:

请检查发射占用寄存器,确认是否已发射所有数据。

用户还可以执行上述读取操作以便通过读取和验证数据来交叉验证写入操作。

如果有来自从设备的 ACK,还请以相同方式检查子寄存器,以对通信进行调试。

检查 TX_FIFO_Empty 标记,确认是否所有数据都已完成发射。

如果步骤 6 中未发现任何问题,则表示您可将数据写入从设备,请检查是否已建立通信。

如何开始进行基本设计测试?

逻辑测试用例:

从 PS-IIC 访问 EEPROM - 用户可参阅代码示例以测试如何通过 PS IIC 控制器访问从设备。

针对从设备的低级 AXI IIC 寄存器访问 - 用户可使用随附的代码示例来测试 AXI IIC 控制器的基本功能。

从 AXI-IIC 访问 EEPROM - 用户可参阅代码示例以测试如何通过 AXI IIC 控制器访问从设备。

Linux 测试用例:

从PS-IIC 访问 EEPROM

请参阅 Wiki 页面

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842160/Cadence+I2C+Driver

以获取 PS IIC 内核配置、设备树节点和可用的用户应用示例。

从 AXI-IIC 访问 EEPROM

请参阅 Wiki 页面

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841974/Linux+I2C+Driver

以获取 AXI IIC 内核配置、设备树节点和可用的 sysfs 示例。

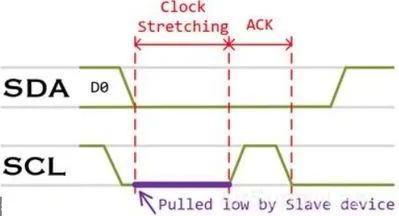

时钟拉伸

IIC 设备可以通过拉伸 SCL 来延缓通信。在 SCL 低位状态下,总线上的任何 IIC 主设备或从设备均可额外下拉 SCL 以防止其重新拉高,使其能够降低 SCL 时钟速率或者将 IIC 通信停止一段时间。

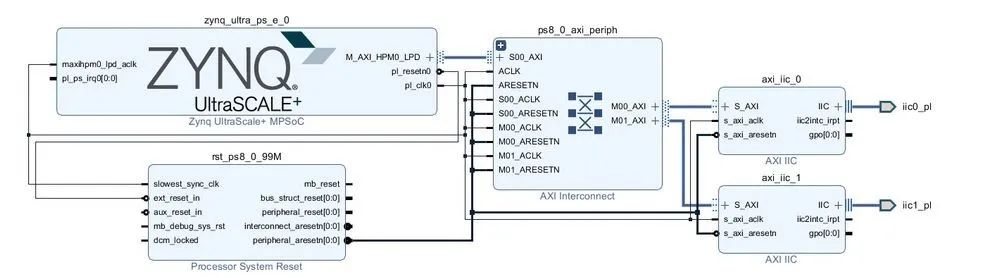

如何使用 AXI-IIC 来测试时钟拉伸

测试用例的目的是生成时钟拉伸机制。

简单硬件设计示例如下:

创建含 2 个 AXI-IIC IP 实例的 Vivado 硬件设计

在此测试用例中,2 个 IP 的输出频率相同。

每个 AXI IIC IP 的 SCL 和 SDA 都应在外部环回,即 SCL0 到 SCL1 且 SDA0 到 SDA1。

设计就绪后,您就可以导出到 SDK 并包含以下附件中的源代码。

注:随附的模块框图和源代码示例已在 ZCU102 板上经过测试。用户可以在自己的定制板上利用此测试用例,也可将其移植到 Vitis。

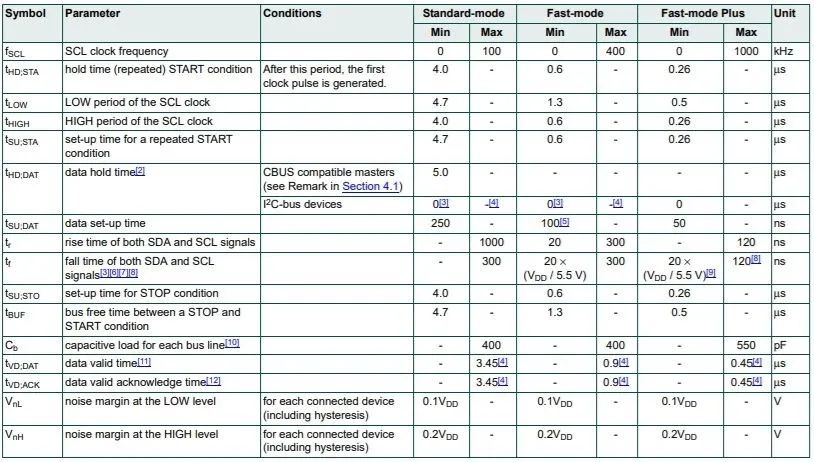

如何为赛灵思 IIC 控制器选择从设备?

AXI IIC 和 PS IIC 控制器都符合 NXP IIC 总线规范。用户必须确保其选择使用的从设备的时序参数与UM10204 的第 48 页上的“表 10”中的参数相同。

SDA 和 SCL 总线行的时序参数

注: PS IIC 不支持 Fast-mode Plus。

编辑:lyn

-

IIC

+关注

关注

11文章

311浏览量

40757 -

AXI

+关注

关注

1文章

145浏览量

18011

原文标题:开发者分享 | PS IIC 和 AXI IIC 调试技巧

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

BSP 调试:前言

变频器带载调试步骤

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

深入解析Renesas E1/E20 Emulator:硬件设计与调试的全方位指南

Renesas E1/E20 仿真器:设计与调试的全方位指南

探索DSC Multilink:调试利器的技术剖析

SEGGER Ozone调试器支持第三方调试工具

图解环路设计及控制技术探讨

调试工具:Eclipse调试工具栏与窗口的深入分析

微电机轴球面成型加工方法的探讨

硬件调试:JLink 驱动配置与调试技巧

泰克MSO46B示波器触摸屏如何提升高速信号调试效率

探讨有关AXIIIC和PSIIC的自调试技巧

探讨有关AXIIIC和PSIIC的自调试技巧

评论