简介

过滤高频电源噪声并干净地分享相似电源供电轨(即混合信号 IC 的模拟和数字供电轨),同时在共享的供电轨之间保持高频 隔离的一种有效方法是使用铁氧体磁珠。铁氧体磁珠是无源器 件,可在宽频率范围内过滤高频噪声。它在目标频率范围内具 有电阻特性,并以热量的形式耗散噪声能量。铁氧体磁珠与供 电轨串联,而磁珠的两侧常与电容一起接地。这样便形成了一 个低通滤波器网络,进一步降低高频电源噪声。

然而,若系统设计中对铁氧体磁珠使用不当,则会产生不利影 响。有一些例子可以说明:由于磁珠和去耦电容搭配用于低通 滤波而导致产生干扰谐振;直流偏置电流的依赖性导致磁珠的 EMI 抑制能力下降。正确理解并充分考虑铁氧体磁珠的特性后, 这些问题是可以避免的。

本文讨论系统设计人员在电源系统中使用铁氧体磁珠时的注意 事项,比如直流偏置电流变化时的阻抗与频率特性,以及干扰 LC 谐振效应。最后,为了解决干扰谐振问题,介绍了阻尼技术, 并比较了各项阻尼方法的有效性。

为演示铁氧体磁珠作为输出滤波器影响而采用的器件是一款 2 A/1.2 A DC-DC 开关调节器,具有独立的正输出和负输出 (ADP5071)。文中所用的铁氧体磁珠主要采用芯片类型表贴 封装。

铁氧体磁珠简化模型与仿真

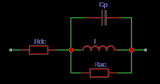

铁氧体磁珠能够建模为一个由电阻、电感和电容组成的简化电 路,如图1a 所示。RDC 对应磁珠的直流电阻。CPAR、LBEAD 和RAC 分别表示寄生电容、磁珠电感和与磁珠有关的交流电阻(交流 磁芯损耗)。

图1. (a) 简化电路模型 (b) 采用Tyco Electronics BMB2A1000LN2 测量的ZRX曲线。

铁氧体磁珠可依据三个响应区域分类:感性、阻性和容性。查 看ZRX 曲线便可确定这些区域(如图1b 所示),其中Z 表示 阻抗、R 表示电阻、X 表示磁珠的电抗。为了降低高频噪声,磁 珠必须处于阻性区域内;电磁干扰 (EMI) 滤波应用尤其需注意 这一点。该元件用作电阻,可阻止高频噪声并以热量的形式耗 散。阻性区域出现在磁珠交越频率 (X = R) 之后,直至磁珠变为 容性的那一点为止。此容性点位置为容性电抗 (–X) 绝对值等于 R 的频率处。

某些情况下,简化电路模型可用来近似计算铁氧体磁珠高达 sub-GHz 范围的阻抗特性。

本文以Tyco Electronics BMB2A1000LN2 多层铁氧体磁珠为例。 图1b 显示了在零直流偏置电流条件下使用阻抗分析仪测得的 BMB2A1000LN2 ZRX 响应。

在测得的ZRX 曲线上,磁珠表现出最大感性特性(Z ≈ XL;LBEAD) 的区域中,该磁珠的电感可根据下列公式计算:

其中:

f 是区域内磁珠表现为感性的任意频率点。本例中,f = 30.7 MHz。 XL 是30.7 MHz 时的电抗,数值为233 Ω。

由公式1 得出的电感值 (LBEAD) 等于1.208 μH。

在磁珠表现出最大容性特性(Z ≈ | XC|;CPAR)的区域中,寄生 电容可根据下列公式计算:

其中:

f 是区域内磁珠表现为容性的任意频率点。本例中,f = 803 MHz |XC|是803 MHz 时的电抗,数值为118.1 Ω。

由公式2 得出的寄生电容值 (CPAR) 等于1.678 pF。

根据制造商的数据手册,直流电阻 (RDC) 等于300 mΩ。交流电 阻 (RAC) 是磁珠表现为纯阻性时的峰值阻抗。从Z 中减去RDC 即可得出RAC。由于相比峰值阻抗,RDC 极小,因而可以忽略。 因此,本例中RAC 等于1.082 kΩ。使用ADIsimPE 电路仿真工具 (由SIMetrix/SIMPLIS 供电)生成阻抗与频率响应的关系。图 2a 显示了电路仿真模型,并提供计算值;图2b 显示了实际测量 结果以及仿真结果。本例中,从电路仿真模型得出的阻抗曲线 与测量曲线严格匹配。

图2. (a) 电路仿真模型 (b) 实际测量结果与仿真测量结果。

在噪声滤波电路设计和分析中,采用铁氧体磁珠模型很有帮助。 例如,当与去耦电容一同组成低通滤波器网络时,对电感进行 近似计算对于决定谐振频率截止很有帮助。然而,本文中的电 路模型是零直流偏置电流情况下的近似。此模型可能随直流偏 置电流的变化而改变,而在其他情况下可能需要采用更复杂的 模型。

直流偏置电流考虑因素

为电源应用选择正确的铁氧体磁珠不仅需要考虑滤波器带宽, 还需考虑磁珠相对于直流偏置电流的阻抗特性。大部分情况下, 制造商仅指定磁珠在100 MHz 的阻抗并公布零直流偏置电流时 的频率响应曲线数据手册。然而,将铁氧体磁珠用作电源滤波 时,通过磁珠的负载电流始终不为零,并且随着直流偏置电流 从零开始增长,这些参数也会随之迅速改变。

随着直流偏置电流的增加,磁芯材料开始饱和,导致铁氧体磁 珠电感大幅下降。电感饱和度根据组件磁芯所用的材料而有所 不同。图3a 显示了两个铁氧体磁珠的典型直流偏置依赖情况。 额定电流为50%时,电感最多下降90%。

图3. (a) 直流偏置对磁珠电感的影响以及相对于直流偏置电流 的曲线 (b) 采用TDK MPZ1608S101A 磁珠

(c) 采用Würth Elektronik 742 792 510 磁珠。

如需高效过滤电源噪声,则就设计原则来说,应在额定直流电 流约20%处使用铁氧体磁珠。如这两个示例所示,在额定电流 20%处,电感下降至约30%(6 A 磁珠)以及约15%(3 A 磁珠)。 铁氧体磁珠的电流额定值是器件在指定升温情况下可承受的最 大电流值,并非供滤波使用的真实工作点。

此外,直流偏置电流的效果可通过频率范围内阻抗值的减少而 观察到,进而降低铁氧体磁珠的有效性和消除EMI 的能力。图 3b 和图3c 显示了铁氧体磁珠阻抗如何随直流偏置电流的变化而 改变。只需施加额定电流的50%,100 MHz 时的有效阻抗就会 从100 Ω 大幅下降至10 Ω(TDK MPZ1608S101A,100 Ω,3 A, 0603),以及从70 Ω 下降至15 Ω(Würth Elektronik 742 792 510, 70 Ω,6 A,1812)。

系统设计人员必须完全了解直流偏置电流对磁珠电感和有效阻 抗的影响,因为这对于要求高电源电流的应用可能十分重要。

LC 谐振效应

当铁氧体磁珠与去耦电容一同应用时,可能产生谐振尖峰。这 个经常被忽视的效应可能会损害性能,因为它可能会放大给定 系统的纹波和噪声,而非衰减它们。很多情况下,此尖峰发生 在DC-DC 转换器的常用开关频率附近。

当低通滤波器网络(由铁氧体磁珠电感和高Q 去耦电容组成) 的谐振频率低于磁珠的交越频率时,发生尖峰。滤波结果为欠 阻尼。图4a 显示的是TDK MPZ1608S101A 测量阻抗与频率的 关系曲线。阻性元件(与干扰能量的耗散有关)在达到大约20 MHz 到30 MHz 范围之前影响不大。低于此频率则铁氧体磁珠 依然具有极高的Q 值,且用作理想电感。典型铁氧体磁珠滤波 器的LC 谐振频率一般位于0.1 MHz 到10 MHz 范围内。对于300 kHz 到5 MHz 范围内的典型开关频率,需要更多阻尼来降低滤 波器Q 值。

图4. (a) A TDK MPZ1608S101A ZRX曲线 (b) 铁氧体磁珠和电容 低通滤波器的S21 响应。

图4b 显示了此效应的一个示例;图中,磁珠的S21 频率响应和 电容低通滤波器显示了峰值效应。此例中使用的铁氧体磁珠是 TDK MPZ1608S101A(100 Ω,3 A,0603),使用的去耦电容 是Murata GRM188R71H103KA01 低ESR 陶瓷电容(10 nF,X7R, 0603)。负载电流为微安级别。

无阻尼铁氧体磁珠滤波器可能表现出从约10 dB 到约15 dB的尖 峰,具体取决于滤波器电路Q 值。图4b 中,尖峰出现在2.5 MHz 左右,增益高达10 dB。

此外,信号增益在1 MHz 到3.5 MHz 范围内可见。如果该尖峰 出现在开关稳压器的工作频段内,那么可能会有问题。它会放 大干扰开关伪像,严重影响敏感负载的性能,比如锁相环 (PLL)、 压控振荡器 (VCO) 和高分辨率模数转换器 (ADC)。图4b 中显示 的结果为采用极轻负载(微安级别),但对于只需要数微安到1 mA 负载电流的电路部分或者在某些工作模式下关闭以节省功 耗的部分而言,这是一个实用的应用。这个潜在的尖峰在系统 中产生了额外的噪声,可能会导致不良串扰。

例如,图5 显示了一个ADP5071 应用电路,该电路采用了磁珠滤 波器;图6 显示了正输出端的频谱曲线。开关频率设为2.4 MHz, 输入电压设为9 V,输出电压设为16 V,负载电流设为5 mA。

图5. ADP5071 应用电路(带磁珠和电容低通滤波器,部署在正 输出端)

图6. ADP5071 频谱输出(5 mA 负载)。

由于磁珠的电感和10 nF 陶瓷电容,谐振尖峰出现在约2.5 MHz 处。出现了10 dB 增益,而非衰减2.4 MHz 处的基频纹波频率。

影响谐振尖峰的其他因素是铁氧体磁珠滤波器的串联阻抗和负 载阻抗。在较电源内阻下,尖峰大幅下降,并被阻尼所减弱。 然而,采用这种方法会导致负载调节下降,从而失去实用性。 由于串联电阻下降,输出电压随负载电流而下降。负载阻抗还 会影响峰值响应。轻载条件下的尖峰更严重。

阻尼方法

本节介绍三种阻尼方法,系统工程师可用来大幅降低谐振尖峰 电平(见图7)。

图7. 不同阻尼方法的实际频率响应。

方法A 是在去耦电容路径上添加一个串联电阻,可抑制系统谐 振,但会降低高频旁路有效性。方法B 是在铁氧体磁珠两端添 加一个小数值并联电阻,这样也会抑制系统谐振。但是,在高 频时滤波器的衰减特性会下降。图8 显示了MPZ1608S101A 使 用和不使用10 Ω 并联电阻的情况下阻抗与频率的关系曲线。浅 绿色虚线表示磁珠采用10 Ω 并联电阻的总阻抗。磁珠阻抗和电 阻组合大幅下降,并主要由10 Ω 电阻决定。但是,采用10 Ω 并联电阻时的3.8 MHz 交越频率远低于磁珠自身在40.3 MHz 时 的交越频率。在低得多的频率范围内磁珠表现出阻性,可降低Q 值,改善阻尼性能。

图8. (a) MPZ1608S101A ZRX曲线 (b) MPZ1608S101A ZRX曲线,缩放视图。

方法C 是添加大电容 (CDAMP) 与串联阻尼电阻 (RDAMP) 的组合,通常这种方法最佳。

添加电容和电阻可抑制系统谐振,同时不会降低高频时的旁路 有效性。采用此种方法可以避免大隔直电容导致电阻功耗过大。 该电容必须远大于所有去耦电容之和,这降低了所需的阻尼电 阻值。在谐振频率处,电容阻抗必须远小于阻尼电阻,以便减 少尖峰。

图9 显示了ADP5071 正输出频谱曲线,其应用电路采用阻尼方 法C,如图5 所示。CDAMP 和RDAMP 分别是1 μF 陶瓷电容和2 Ω SMD 电阻。2.4 MHz 时的基频纹波降低5 dB 增益,而非图9 中 显示的10 dB 增益。

图9. 采用阻尼方法C时的ADP5071频谱输出以及磁珠和电容低 通滤波器。

一般而言,方法C 最为优雅,通过添加一个电阻和陶瓷电容的 串联组合实现,无需购买昂贵的专用阻尼电容。比较可靠的设 计始终包含电阻,可在原型制作时方便调试,如果不需要还可 移除。唯一缺点是额外的元件成本和更多的电路板占位空间。

结论

本文讨论了使用铁氧体磁珠时必须考虑的关键因素。本文还详 细介绍了一个简单的电路模型,表示磁珠。仿真结果在零直流 偏置电流处表现出良好的实际测量阻抗与频率响应的相关性。

本文还讨论了直流偏置电流对铁氧体磁珠特性的影响。结果表 明超过额定电流20%的直流偏置电流可能会导致磁珠电感的大 幅下降。这样的电流还会降低磁珠的有效阻抗,削弱EMI 滤波 能力。在供电轨上以直流偏置电流方式使用铁氧体磁珠时,应 确保电流不会导致铁氧体材料饱和以及产生电感的大幅变化。

由于铁氧体磁珠是感性的,将其与高Q 值去耦电容一同使用时 应当非常谨慎。如果不谨慎,会在电路中产生干扰谐振,弊大 于利。本文中提出的阻尼方法在负载上采用大去耦电容与阻尼 电阻的串联组合,从而避免了干扰谐振。正确使用铁氧体磁珠 可以高效而廉价地降低高频噪声和开关瞬变。

编辑:jq

-

电容

+关注

关注

100文章

6545浏览量

160378 -

磁珠

+关注

关注

6文章

281浏览量

45469 -

串联电路

+关注

关注

6文章

162浏览量

27671 -

陶瓷电容器

+关注

关注

1文章

234浏览量

26597

原文标题:铁氧体磁珠揭秘

文章出处:【微信号:TLTECH,微信公众号:韬略科技EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

风华贴片磁珠规格参数的详细选型指南

磁珠——电路里的高频噪声“吸尘器”

风华高科ABM系列车规级超大电流叠层片式铁氧体磁珠解析

风华叠层片式铁氧体高频磁珠CBF系列在高频段具有优异的EMI抑制效果

使用铁氧体磁珠解决EMC噪声和功率器件栅极振荡

探秘MH1005系列高电流贴片铁氧体磁珠

探秘MH1608系列高电流片式铁氧体磁珠:性能、规格与应用考量

探索MH2029-T系列高电流贴片铁氧体磁珠的特性与应用

村田BLM系列磁珠电感如何有效抑制高频噪声?

TE Connectivity BMC系列多层铁氧体磁珠技术解析与应用指南

村田磁珠电感:高频噪声抑制解决方案

贴片电感磁珠的选型方法有哪些?

带你们揭开铁氧体磁珠神秘的面纱

带你们揭开铁氧体磁珠神秘的面纱

评论