作者:焦慧芳,温平平,贾新章,王群勇,罗雯

针对不同工艺、不同设计的功能全兼容集成电路等效老化的需要,提取出了集成电路等效老化的特征参数—“归一化老化电流”指标α,并讨论了等效老化信号的确定方法。结合集成电路等效老化信号确定方法,以CPU486为研究对象,给出通用CPU 等效老化试验方案,为评估和比较不同CPU 的质量和可靠性提供了统一的试验平台。

老化是一种能够将产品早期故障剔除的无损筛选试验技术。集成电路的老化过程实质上就是通过对其施加应力,加速其内部潜在缺陷暴露的过程。经过老化,可以使有缺陷的集成电路在上机使用前失效,从而保证了集成电路最终的使用可靠性。老化的作用主要有两方面,一是剔除有缺陷的、可能发生早期失效的产品,保证产品的使用可靠性;二是评估和比较不同产品的质量和可靠性水平。

近年来,国家通过各种途径大力扶持微处理器(CPU)产品的研发,已相继研制出了具有独立知识产权的CPU 产品。相对于先进的设计和制造技术,国产CPU 质量和可靠性评价技术研究相对滞后。目前国内CPU 老化试验方案都是由研制单位自己制订,不同厂家的老化方案间存在较大的差距。如额定工作频率为33MHz 的CPU,有的单位将老化时钟频率定为1MHz,有的将老化时钟频率定为20MHz,这样老化应力强度和老化效果完全没有可比性,因此无法通过老化试验进行CPU 产品质量和可靠性水平的评估和比较。作为用户,希望通过质量和可靠性试验,评估出更为理想的产品。因此,对CPU 进行等效老化试验技术的研究,成为CPU 质量和可靠性评估急需解决的问题之一。基于这样的技术需求,为了解决公正、科学地评估和比较不同CPU 的质量和可靠性水平,本文进行了通用CPU 等效老化试验技术的研究。

CPU老化试验技术动态

老化试验原理

集成电路的老化过程,实际上是在强环境温度应力下,通过对其施加电应力模拟其正常工作,使故障尽早出现。老化试验的目的是保证产品的使用可靠性和评估产品的质量与可靠性水平。集成电路的老化试验退化模型服从Arrhenius 方程,式(1)为Arrhenius 方程:

式中?R(T)是温度T(为绝对温度K)时的反应速率,A 为一系数,E a 为对应的反应激活能,k为Boltzmann 常数。温度T 越高,R(T)越大,退化越快,失效率越高,器件的平均无故障工作时间也越短。许多文献中的数据表明,对于Si 材料集成电路,在工作过程中,芯片温度每提高10C,器件的失效率约会增加一倍。因此,芯片温度在老化过程中起着决定性的作用,老化试验过程中的应力强弱可以归结为芯片温度的高低。

老化时,芯片温度一般可以用下式描述:

其中,TJ表示芯片温度,TA 是指环境温度,P 为芯片工作功耗,θJA?是芯片到环境的热阻。由于TA可以设置成相同的值,所以要确定老化时芯片温度TJ的关键就在于确定功率P 与热阻θJA?的乘积。

在老化试验中,外界可以控制的应力只有环境温度和电应力,以及被试器件的散热条件。同样的老化箱,其中空气的流速都是相同的,器件的热阻主要由芯片封装结构、材料和工艺决定,属于器件的本征特性。热阻特性的好坏与芯片功耗一样,由其设计和制造决定,热阻越小,产品的可靠性越高。在进行质量和可靠性评价试验时,对其本征的特性热阻是必须进行考核的,这样在考虑老化试验方案时,重点应该放在老化功耗上。

随着集成电路设计线宽的不断缩小,由等比缩小效应引起的漏功耗不可避免地增大,为了提高可靠性,集成电路纷纷采用低功耗设计技术。同一类产品,由不同的公司设计生产,尽管功能完全一样,其功耗却相差很大,功耗低的产品,工作时的芯片温度肯定低于功耗高的产品。如果在老化时仅仅考虑芯片温度,使功耗低的产品与功耗高的产品芯片温度一致,是不符合实际应用情况的,因而是不科学的,必须研究能够表征等效老化应力的物理量,以评估老化试验的等效性。

CPU 老化技术难点和存在问题

从本质上来说,CPU 老化与传统的集成电路老化的原理和作用是相同的。一般对于普通的组合逻辑电路,可以选取敏化通路法老化,对于单一的时序逻辑电路则可以采用状态变迁检查法老化。但对于CPU 这种功能非常复杂,集成的逻辑和存储功能模块繁多的芯片,简单的老化方法难以达到全面老化的目的。

迄今为止,国内CPU 的老化仍然参照MIL-STD-883“微电子器件试验方法”中方法1005A,该方法规定了老化环境温度及尽可能模拟实际应用的电激励等试验条件,但没有考虑到工艺变化对VLSI芯片特性的影响。随着CPU 的工作频率不断上升,芯片漏功耗急剧增加,老化时芯片自身功耗发热对芯片温度的影响成为必须考虑的因素。如何根据不同的工艺条件来确定老化频率是CPU 老化试验的一个关键问题。

老化向量集的确定是CPU 老化试验中遇到的另一个挑战。对CPU 老化而言,老化向量集和老化频率一样是十分重要的。不同的老化向量集,对CPU 内部单元的覆盖率千差万别,老化效果相差非常大。不同电路之间,只有其内部单元的覆盖率水平相当时,才能获得同等的老化效果。

只有在同样的试验原则下进行的评价,才具有实际可比的内涵。目前对国产CPU 的老化,老化线路、老化频率都由生产方自定,对老化方法没有评价的准则,老化结果可比性差。同时也很难保证到达用户手中CPU 的使用可靠性。因此建立一个等效的老化试验规范,是CPU 质量与可靠性评价技术的关键,也是业界非常关心的问题。

等效老化信号的确定

要建立一个具有可比性的CPU 等效老化试验规范,其实质就是将CPU 老化试验方案与等效老化信号确定方法有机地结合起来。本节主要阐述如何确定集成电路的等效老化信号,在后面的章节会专门讨论CPU 老化试验方案。

老化应力的表征

从老化原理可知,芯片温度在老化过程中起着决定性的作用。如果产品的功耗相同,老化时外加的温度和电应力都相同,根据(2)式可知,老化芯片温度能够表征老化应力强度。但如果考虑到芯片自身功耗的差异,仅用芯片温度就无法表征老化应力强度。产品老化时,功耗大的产品所加的电应力肯定大于功耗小的产品,当然功耗大的产品芯片温度也会高于功耗小的产品。在评估老化应力强度时,只比较外加电应力的绝对大小是不够的,必须将产品自身功耗的差异考虑进去,找到一个包含自身功耗差异的老化应力特征参数以评估老化应力的等效性。只有这一特征参数相等,才能使不同产品的老化效果相同。

归一化老化电流

集成电路的工作功耗与信号的频率有关,在晶体管翻转过程中,其功耗由三部分组成:动态功耗、漏电功耗(静态功耗)和短路(直流通路)功耗。其相关关系可用下式表示:

其中第一项是CV2f是动态功耗,C 是一个分布电容,是由设计和工艺决定的,当电源电压一定,动态功耗与信号频率呈线性关系。(3)式中第二项VI peaktsf 是短路功耗,I peak是MOS 管导通时的峰值电流,ts 为PMOS 和NMOS 同时导通的时间。漏电功耗相对于动态功耗和短路功耗来说比较小,(3)式没有考虑。由于Ipeak和ts参数在老化的过程中难以提取,本文只针对动态功耗CV2f进行研究。

如果老化时所加信号频率等于其额定工作频率,老化时由电应力引起的芯片温升与实际工作情况相似。但由于动态老化是一个长期的加电试验过程,而现代集成电路的工作频率越来越高,老化用的信号源根本无法达到其额定工作频率。现代最先进的老化设备提供的老化信号最高频率仅为20“30MHz,而CPU 动辄数百到数千MHz,实际上CPU 的老化频率远远低于其额定工作频率。

由于环境温度可以人为设定,器件热阻又为其本征特性,这样由公式(2)决定的老化芯片温度,只有在改变老化功耗时才发生变化。因此,老化的效果就由老化功率的高低决定。

由(3)式动态功耗CV2f可以推得老化功耗电流的表达式:

由老化原理可知,老化功耗电流越接近实际工作时的电流,老化功率和实际应用功率就越接近,老化就越能模拟实际应用状态,老化应力就越强,其老化效果也越好。但由于老化设备在工程中不可能达到实际应用的水平,一般老化电流都低于正常工作电流。不同的电路,只要老化电流与额定工作电流的比例系数相等,从逻辑上可以推出老化应力水平相同。这里将老化电流与额定工作电流的比例系数称之为“归一化老化电流”,用α表示:

其中Iccb为老化电流,Icco为额定工作电流,“归一化老化电流”α被定义为表征老化应力水平的特征参数。

等效老化信号的确定

对于不同的电路,由于其设计和制造工艺不同,其额定工作电流和分布电容都不一样,由(4)式可知,电流Icc随信号频率线性变化的斜率不同。因此,不同产品在相同的信号频率下老化,其“归一化老化电流”α会有较大的区别,老化应力水平并不一致。

针对两种功能相同,工艺和设计都不同的产品,老化的外围线路图是相同的。令两种产品的“归一化老化电流”为α,它们的额定工作电流分别为I cco1和I cco2,电流随频率变化的斜率分别为K1=C1V1、K2=C2V2,就可以分别确定出动态老化信号频率:(6),(7)式中,α是根据可靠性要求和工程情况综合确定的,额定工作电流I cco可以测试或从产品手册中查出,电流随频率变化的斜率k 可以通过试验的方法求出,等效老化的信号频率也就随之确定。

通用CPU 等效老化方案设计

通用CPU 老化线路设计

老化技术从静态老化、动态老化发展到功能性老化,功能性老化被认为是探测器件缺陷的一种更好的方法。然而进行功能性老化需要将测试设备与老化设备有机地结合起来,设备非常昂贵,目前国内还没有条件进行功能性老化。基于国内的现状,文中不涉及CPU 功能性老化及老化向量集的研究,重点在于研究等效的CPU 动态老化试验方法。

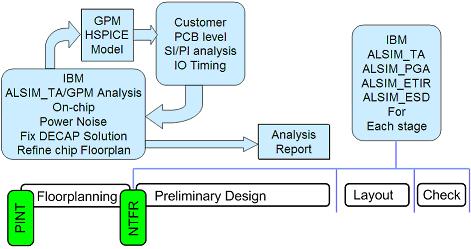

参照国内外一些老化方案,结合对CPU486 体系结构的研究,进行通用CPU486 老化试验方案设计。根据设计公司对通用CPU486 模拟仿真的结果可知,给CPU486 加复位和时钟信号,若所给复位信号和时钟信号能使CPU 正常复位,CPU 内部翻转的晶体管数可达60%~70%。仅给时钟信号内部翻转的晶体管数目是很少的,这一点从老化电流上就可反映出来,两种情况下其老化电流相差非常大,见图1。在无法进行功能性老化的情况下,采用时钟信号和复位信号进行CPU486 动态老化,可使老化覆盖率达到60”70%,不失为一种有效的工程方法。以CPU486 为例,本课题采用加时钟和复位信号的方式进行动态老化。老化时,在时钟端与复位端加上信号,其它输入端通过一个4.7k?的保护电阻接地或电源,使其有一个固定的状态,输出开路。老化状态可通过地址状态输出端ADS#进行观察,若ADS#端有正常的输出信号,表明其老化状态正常。

通用CPU 等效老化信号确定

通用CPU 老化时要同时加上时钟和复位信号,为了使得不同产品在相同的“归一化老化电流”下进行老化,必须确定时钟和复位信号频率对CPU 老化电流的影响。

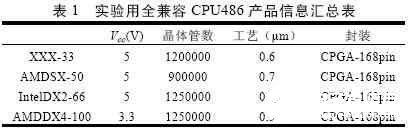

本文设计了一系列实验,实验采用了四种不同公司、不同设计、不同工艺,相同封装的几组样品,有关试验样品的具体信息见表1,其中XXX-33 为国内某公司产品。

采用前面确定的通用CPU 动态老化线路,对表1 列出的四种产品进行了实验。图1 是IntelDX2-66老化电源电流Icc随Reset、CLK 信号频率变化曲线,其他几种产品的实验结果与图1 类似。

从图1 可以看出不加Reset 信号时老化电源电流远远小于Reset 频率不为0 的情况;Reset 频率在500Hz、1kHz 直到10kHz,IntelDX2-66CPU486 老化电源电流Icc值随CLK 频率变化趋势几乎可以认为是相重合的直线,说明Reset 频率变化对老化电流的影响不大,而老化电流随CLK 的频率呈线性变化,CLK 频率对老化电流的影响十分显著。

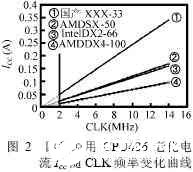

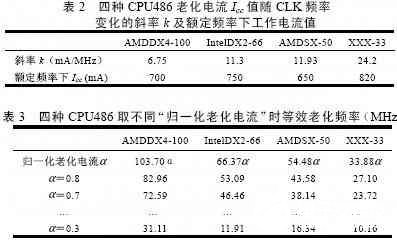

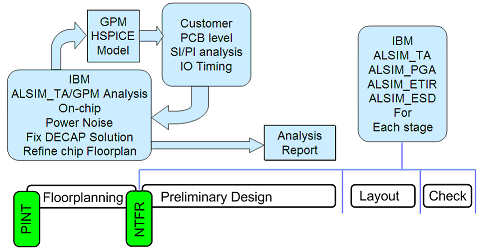

图2 是在Reset 频率为10kHz时,四种不同CPU486 老化电流随CLK 频率变化的曲线。从图2 可以方便地得出各款CPU486 的老化电流Icc随CLK 频率变化的斜率。同时从各自的数据手册上可以查出在额定频率下的工作电流值。表2 给出了四种CPU486 老化电流随CLK 频率变化的斜率k 值(为实验值)及额定频率下的工作电流值cc I 。

设归一化老化电流为α,根据(6)式可分别算出四种CPU486 等效老化的时钟信号频率,具体的计算结果见表3。“归一化老化电流”α的值,主要根据产品的额定功率、热阻、最高结温及老化设备能力等因素综合确定。α的值取范围为0“1,但α具体取什么值,主要受老化设备能力的限制,老化信号源频率高,可以将“归一化老化电流”α的值取得大一些,但只要所有的同类产品α值相同,老化的应力水平相当。但对于功耗特别大的产品,在老化时一定要注意α的取值,使老化时芯片温度小于最高结温的限制。

结论

通过对通用微处理器等效老化试验方法的研究,可以得出如下结论:1)等效老化试验是评估和比较不同工艺、不同设计的功能全兼容集成电路质量和可靠性水平的重要手段;2)“归一化老化电流”α是能够表征等效老化应力强度的特征参数;3)通用CPU 可以采用本文给出的等效老化试验方案实现质量和可靠性水平的有效评估和比较。

责任编辑:gt

-

集成电路

+关注

关注

5464文章

12685浏览量

375694 -

cpu

+关注

关注

68文章

11327浏览量

225878 -

微处理器

+关注

关注

11文章

2440浏览量

86143

发布评论请先 登录

触摸屏高难点精华技术大集合

涨知识,电动汽车充电桩设计技术、难点、优化方案

单片机之间的通信方式/难点/解决方案

针对物理设计难点进行分析及提出解决方案

通用CPU等效老化方案设计与试验技术的研究

无线充电测试难点及解决方案

无线充电测试难点及解决方案资料下载

CPU老化技术难点、存在的问题及解决方案

CPU老化技术难点、存在的问题及解决方案

评论