据麦姆斯咨询报道,1975年戈登·摩尔(Gordon Moore)做出了一项预测,这就是著名的摩尔定律:集成电路可以容纳的晶体管数量每两年(或18个月,取决于芯片类型)翻一番,见图1。简单来讲,集成电路的处理性能或处理速度每两年翻一番。通常情况下,对于图像传感器来讲,像素数量每两年翻一番,或像素尺寸每两年增加√2倍。其实没那么快,因为图像传感器更像是模拟芯片,而不是数字芯片,不会与技术节点成比例增长。彩色(RGB)图像传感器能够增加像素尺寸,但带来的是性能降低,因为尺寸/成本的比值非常重要。通过仅对像素区进行有针对性的工艺改进,或多片晶圆3D堆叠,将处理功能转移到较小工艺节点,这也在一定程度上起到了帮助作用。

图1:摩尔定律

将此规律运用到ToF像素领域进行综合思考,与RGB图像传感器不同,ToF像素值需要计量等级。这是因为ToF像素值支持深度测量,而不是让图像看起来“漂亮”。ToF像素值性能由信噪比决定。接下来让我们进行深入探讨。为了简化分析,在研究占主导地位的噪声源时,有三种不同机制。

1. 信号散粒噪声(Signal Shot Noise)

2. 环境散粒噪声(Ambient Shot Noise)

3. 读取噪声(Read Noise)

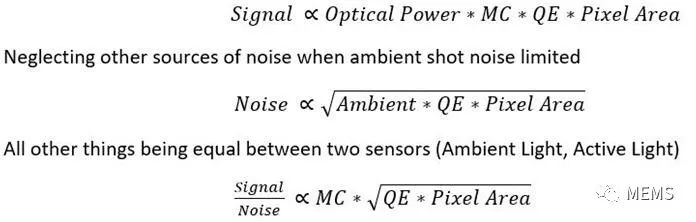

选择其中一种机制(如:环境散粒噪声)进行深入分析。这里,量子效率(Quantum Efficiency,以下简称QE)是从入射光子中收集光子电荷的概率,而调制对比度(Modulation Contrast,以下简称MC)是光子电荷生成可用于获取深度信号的概率,则:

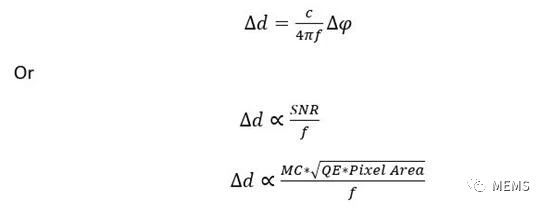

假设MC和QE的值处于上限,由于像素面积减少了一半,时间抖动就增加了√2。这是否意味着像素较小会导致性能不佳?事实证明,还有另一个杠杆参数可以提高性能,这是调制频率。来自微软的Cyrus曾在其博客文章中提到了基于相位的ToF测量方法。时间抖动的不同表达方式为:

图2:环境散粒噪声限制机制:频率标度与像素尺寸的关系

从图2看出,可以通过增加频率来恢复因为像素尺寸缩小产生的性能下降。但是,只有当MC在更高频率时不会显著降低,才可能这样做。微软的ToF技术是高频MC的领导者(频率在320 MHz时MC为78%)。此外,更高的频率会增加芯片功耗和激光光学功耗。

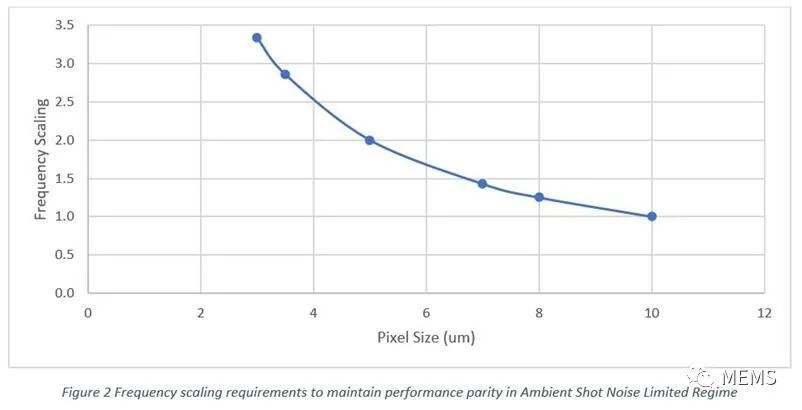

下图(图3)展示了ToF像素尺寸随着摩尔定律发展的规律。

图3:摩尔定律 vs. ToF像素尺寸发展

注:文章来自微软资深首席科学家Swati Mehta,由麦姆斯咨询编译。

责任编辑:lq

-

摩尔定律

+关注

关注

4文章

640浏览量

81153 -

图像传感器

+关注

关注

68文章

2088浏览量

132490 -

数字芯片

+关注

关注

1文章

120浏览量

19102

原文标题:当ToF像素遇到摩尔定律,剧情如何发展?

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

UWB 定位中的 ToF、TWR、TDoA 是什么?

Chiplet,改变了芯片

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

当摩尔定律 “踩刹车” ,三星 、AP、普迪飞共话半导体制造新变革新机遇

AI狂飙, FPGA会掉队吗? (上)

先进封装转接板的典型结构和分类

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

晶心科技:摩尔定律放缓,RISC-V在高性能计算的重要性突显

电力电子中的“摩尔定律”(2)

跨越摩尔定律,新思科技掩膜方案凭何改写3nm以下芯片游戏规则

电力电子中的“摩尔定律”(1)

当ToF像素遇到摩尔定律如何发展?

当ToF像素遇到摩尔定律如何发展?

评论