通过研究立体液晶显示器的图像获取及显示接口,完成了从摄像到显像的整体数字系统的电路部分设计。

立体液晶显示器是近年来新出现的虚拟现实显示设备,它真实地再现场景的三维信息,显示具有纵深感的图像。其最大特点就是观察者无需使用任何附加设备,直接用肉眼就可看到屏幕上显示的立体图像。观测者可以更容易、更快速地理解真实的景深信息,更全面、更直观地洞察图像空间位置的实际分布状况。

目前,国内外的自由立体液晶显示方式通常采用计算机采集图像并存储,处理后输出到液晶屏驱动电路板,然后通过板载模数转换模块等处理后在液晶屏显示立体图像。这种方式主要由计算机进行图像采集和处理,其开发周期短,但成本较高,体积较大,且需要液晶屏厂商提供驱动电路板。因此,本文以FPGA为核心,设计并开发了一套专用于立体液晶显示的图像采集和显示系统,可广泛应用于立体显微、测绘领域、工程设计、军事指挥等各个方面,有望形成产业规模。

1 方案设计

人们通常是两眼同时观看物体。由于两只眼睛视轴的间距(约65mm)及同一物体在两眼的构像不一致形成的生理视差,使得左眼和右眼所接收到的视觉图像不同。而大脑通过眼球的运动、调整,综合这两幅图像的信息,产生立体感。本设计通过两个完全相同的摄像机,使两个图像平面位于同一平面Q,两机坐标轴平行,水平轴重合。通过两摄像头模拟人眼视差来恢复物体的深度信息。视差越大说明物体离透镜的距离越近;反之,则越远。

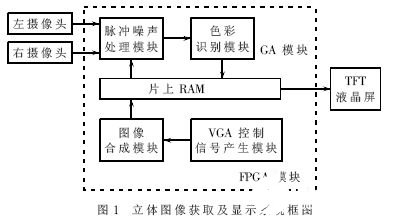

立体图像获取及显示系统框图如图1所示。CMOS双摄像头严格水平放置,获取立体图像对。数字图像数据并行进入FPGA,利用片上RAM作帧缓存,然后由FPGA中的图像处理模块模拟大脑对两眼图像的综合处理,按照VGA时序输出到液晶屏显示。

采用松下10.4英寸工控液晶屏EDTCB03Q2F,其接口为TTL电平,可用FPGA直接驱动,分辨率为640×480像素,色彩为262K(6bit/color),工作电压3.3V。

以OmniVision公司的OV9620这一较为典型的彩色1/2英寸CMOS图像传感器模块作为核心,实现双芯片成像系统。该芯片采用Bayer模式滤波,其中有1 310 720个有效像素,其他像素用于黑电平补偿和内插。它支持SXGA和VGA两种模式,支持摄像和快拍,带有光学黑电平校正、可编程/自动曝光和增益控制、可编程白平衡控制、水平和垂直次采样(4:2和4:2),可编程设定成像窗口和帧传输速率。内部集成了SCCB控制接口便于访问其57个片内寄存器,以实现对图像传感器芯片各种工作状态参数的设定。

采用FPGA实现数据的采集、处理及作为液晶屏的显示接口。相对普通微处理器,FPGA时钟频率高、接口多,满足高速数据传输需要;相对DSP而言,用户I/O较多,不需扩展即可实现数据实时采集和输出,且便于实现外加存储器扩展。采用Xilinx公司的spartan3系列XC3S1000,系统门级为1000K,片上分布式RAM为120Kbit,分块RAM为432Kbit。用户I/O共391个,片上锁相环(DCM)4个。它输出红、绿、蓝各6位信号,时钟信号、行/场同步信号以及复合消隐信号在液晶屏显示。

2 系统实现

2.1 双摄像头成像系统设计

该成像系统主要由两个CMOS图像传感器、外围控制电路和光学镜头组成。系统设计的主要任务是:(1)通过对管脚信号的控制设置成像系统的工作状态,输出VGA模式;(2)提供系统的工作时钟信号,保证两个摄像头工作时钟严格同步;(3)为系统提供稳定的工作电源和电平设置;(4)光学镜头的设计。

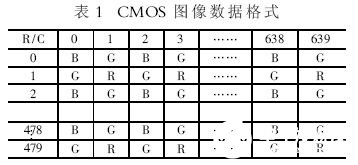

CMOS芯片为TTL电平接口,与FPGA兼容,其输出数据格式如表1所示。它输出10位并行红、绿、蓝信号,行、场同步信号,时钟信号供FPGA采集。

2.2 FPGA设计

FPGA作为整个图像系统的控制核心,实现数据采集接口及立体图像合成的功能。采用Top-down设计方法,首先划分为不同的功能模块,用VHDL语言进行行为级设计,然后采用原理图进行顶层设计,经过编程、综合、仿真和实现,最后在电路板上进行验证。

2.2.1 VGA控制信号的产生模块

参照VESA VGA标准,像素时钟频率为25.175MHz,行频为31.469kHz,每行包括800点,其中有效显示640点,行同步时间96点,行消隐前肩16点,行消隐后肩48点,共160点行消隐期;场频(刷新率)为59.94Hz,每场有525行,其中有效显示480行,场同步时间2行,场消隐前肩11行,场消隐后肩32行,共45行。

像素时钟由FPGA外接50MHz晶振二分频得到,作为液晶屏驱动控制信号发生的基准,行频和场频相与得到数据有效信号(DE)。

2.2.2 脉冲噪声处理

数字图像的噪声主要来源于图像的获取和传输过程。在成像阶段,因为成像系统的散焦、成像中的短暂停留、成像器材的固有缺陷等带来传感器噪声;在传输过程中的噪声主要因为电子电路噪声以及数据传输环境的不理想。这样,造成图像退化的主要因素为脉冲噪声(椒盐噪声),在数字传输结束后,总是以最大值表现出来。即负脉冲以黑点(胡椒点)出现,正脉冲以白点(盐点)出现,且具有小面积的特点。由于FPGA片上存储资源有限,以及视频流固有的限制,只能参考当前像素之前的像素进行处理。考虑到距离较远的像素相关性较小,如图2所示:以像素5为当前像素,选取1,2,3,4像素作为参考。标定后,脉冲噪声总是以数字化最大值表现出来,即黑椒点为0,盐点为255。当色彩数据进入FPGA时,首先判断其数值:如果是椒盐点,则该数据取1,2,3,4像素的该色彩分量平均值;如果不是椒盐点,则送入色彩识别模块。

2.2.3 色彩识别模块

如表1所示,CMOS摄像头输出格式为:第一行BGBGBG……,第二行GRGRGR……,即RGB信号按此顺序串行输出,而液晶屏接收RGB信号并行输入,必须识别出输入数据属于何种色彩分量,经组合后输出到数据处理模块进行处理。

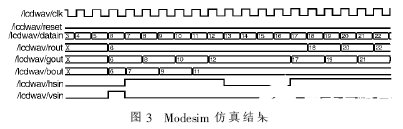

采用ModelSim对色彩识别模块进行仿真,结果如图3所示。摄像头帧频(vsIn)输出一个脉冲表示一帧到来时,若行频(hsIn)有效,则第一行开始,数据端口(dataIn)中的数据依次输出到蓝色分量端口(bOut)、绿色分量端口(gOut);若行频无效,则无数据输出;第二行依次按照绿色分量端口(gOut)、红色分量端口(rOut)……如此循环,使得相邻四个像素共享蓝色和红色分量,横向相邻的两个像素共享绿色分量。数据经过判断组合后,RGB信号并行存储到片上RAM,加快处理速度,便于实时输出至液晶屏。

2.2.4 图像合成模块

液晶屏上采用光栅对图像进行空分处理,实现双眼视差,只需对其输入相应数据即可实现立体显示。两个摄像头的图像数据并行读入(由于液晶屏接收RGB各6位进行显示,故只读入摄像头的高6位),经噪声处理及色彩识别并组合后放入片上RAM进行缓存。在VGA控制信号中的行、场频控制下,计算RAM地址,从片上RAM中读出数据并输出至液晶屏,输出效果如图4。其中黑色表示左摄像头数据,白色表示右摄像头数据,以像素为单位交替出现,即奇数列为左摄像头数据,偶数列为右摄像头数据。

本设计采用双CMOS摄像头模拟人眼获取图像。以FPGA为核心设计了图像采集、处理和显示接口,其图像数据可直接输出到TTL接口的液晶屏显示。对于目前市场上大部分LVDS接口的液晶屏,只需修改FPGA的I/O属性即可,无需液晶屏厂家提供驱动电路板,实现了立体液晶显示图像采集和显示系统的最小化设计,目前已成功运用于实时图像的立体液晶显示。整个系统结构紧凑,扩展性强,生产成本低。此外,该系统只需对FPGA进行重新编程即可用于其他多路视频采集、处理及显示方案。

责任编辑:gt

-

FPGA

+关注

关注

1655文章

22283浏览量

630181 -

显示器

+关注

关注

22文章

5130浏览量

143635 -

显示系统

+关注

关注

1文章

150浏览量

24890

发布评论请先 登录

如何利用FPGA和VHDL语言实现PCM码的解调?

用VHDL语言实现3分频电路

基于Zedboard FPGA的VGA图像信号采集系统的设计

关于通过FPGA中VHDL语言实现ALU的功能设计详解

使用Quartus和VHDL语言实现的LPC时序的工程文件

基于FPGA器件和VHDL语言实现的图像采集和显示系统的设计

基于FPGA器件和VHDL语言实现的图像采集和显示系统的设计

评论