来自复旦大学微电子学院的消息,该校周鹏团队针对具有重大需求的3-5纳米节点晶体管技术,验证了双层沟道厚度分别为0.6 /1.2纳米的围栅多桥沟道晶体管(GAA,Gate All Around),实现了高驱动电流和低泄漏电流的融合统一,为高性能低功耗电子器件的发展提供了新的技术途径。

据悉,相关成果已经在第66届IEDM国际电子器件大会上在线发表。

报道提到,工艺制程提升到5nm节点以下后,传统晶体管微缩提升性能难以为继,需要做重大革新。于是GAA晶体管乘势而起,它可实现更好的栅控能力和漏电控制。

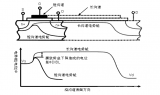

此番周鹏团队设计并制备出超薄围栅双桥沟道晶体管,驱动电流与普通MoS2晶体管相比提升超过400%,室温下可达到理想的亚阈值摆幅(60mV/dec),漏电流降低了两个数量级。

据悉,GAA晶体管也被译作“环绕栅极晶体管”,取代的是华人教授胡正明团队研制的FinFET(鳍式场效应晶体管)。按照目前掌握的资料,三星打算从2022年投产的第一代3nm就引入GAA晶体管,台积电略保守,3nm仍是FinFET,2nm开始启用GAA。

另外,中芯国际梁孟松日前也披露,该公司的5nm和3nm的最关键、也是最艰巨的8大项技术也已经有序展开, 只待EUV***的到来,就可以进入全面开发阶段。

双桥沟道晶体管示意图及其性能图

责编AJX

-

晶体管

+关注

关注

78文章

10443浏览量

148692 -

3nm

+关注

关注

3文章

238浏览量

15083 -

GAA

+关注

关注

2文章

38浏览量

8003

发布评论请先 登录

小米自研3nm旗舰SoC、4G基带亮相!雷军回顾11年造芯路

Cadence在CES 2026成功演示3nm eUSB2V2 PHY IP解决方案

半导体晶体管的发明历史

漏致势垒降低效应如何影响晶体管性能

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

电压选择晶体管应用电路第二期

台积电2纳米制程试产成功,AI、5G、汽车芯片,谁将率先受益?

晶体管的定义,晶体管测量参数和参数测量仪器

多值电场型电压选择晶体管结构

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

晶体管光耦的工作原理

下一代高速芯片晶体管解制造问题解决了!

什么是晶体管?你了解多少?知道怎样工作的吗?

跨越摩尔定律,新思科技掩膜方案凭何改写3nm以下芯片游戏规则

复旦教授成功实现3nm/5nmGAA晶体管

复旦教授成功实现3nm/5nmGAA晶体管

评论