1.引言

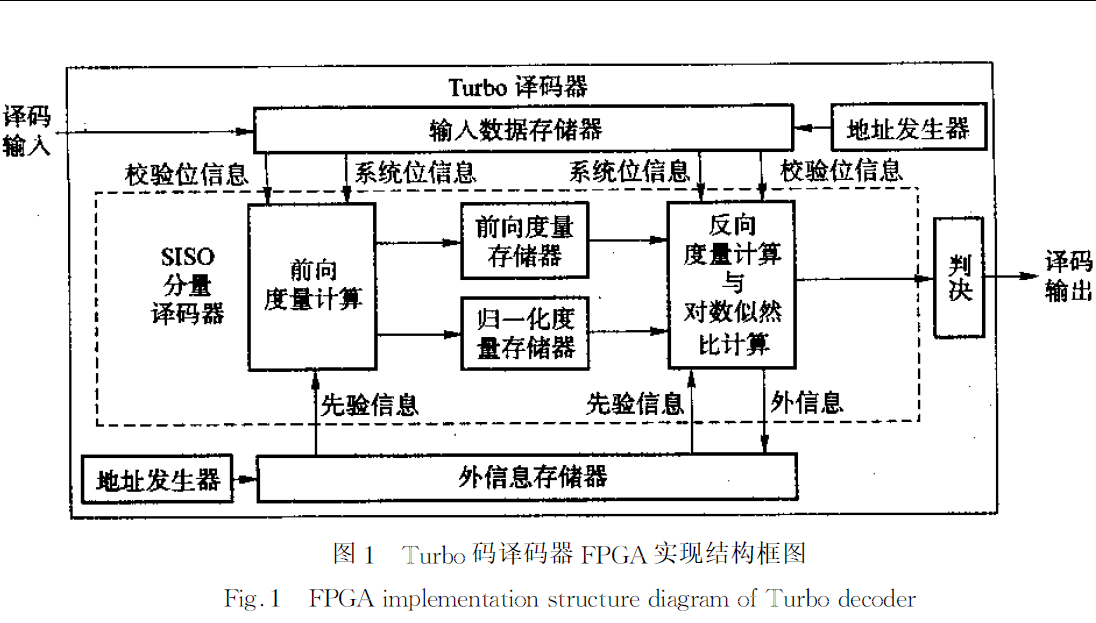

在无线通信系统中,可靠的数据传输是一个非常重要的论题。Turbo编码得到逼近香农限的译码性能,成为研究和应用的热点。Turbo码的译码采用迭代运算的方式,即将前级译码器的输出作为外信息输入到本级译码运算,如此反复进行直到达到相应收敛度才结束译码。

Turbo码有多种译码算法,基于Bahl-Cocke-Je-linek-Raviv(BCJR)算法的MAP译码是最为广泛应用的一种。MAP算法可以通过系统信息和外信息来获得对一个比特良好的概率估计,其译码输出的信息可以作为外信息由其他译码器在下一次迭代过程中使用。经过一定次数的迭代运算之后,对外部信息的运输结果收敛时,译码器盼陛能逼近香农限。

尽管Turbo码的性能接近最优值,但在实际集成电路硬件设计中,对于MAP算法的实现面临两个主要问题:

(1)时间延迟过大。

(2)对于存储器容量空间需求大。

MAP译码器采用迭代的方式工作,即在每次迭代过程中,MAP译码器首先利用前一次迭代中得到的外信息和信道接收信息,对待译码的码字从头部到尾部再从尾部到头部两个方向收集译码信息;利用收集到的译码信息,译码器做最大释然估计,估计值可以作为其他译码器做下一次迭代过程中的外信息使用。对于比特长度为n的数据帧,前向和后向的信息提取共需2n步处理,另外估计数据需要n步。从而MAP算法共需要3n步操作,因此其译码延迟较大。MAP译码器在新的外部信息生成之前需要保存之前所有的译码信息,对于一个长度为n比特的数据帧,且Turho码空间为S,则需要2×n × S个存储单元来保存信息。例如,在CDMA2000系统中的Turbo码中S=8,且n=20730,则MAP译码器需要331680个存储单元,这对于存储器的需求压力较大。为了降低对存储空间的要求以及提高MAP及其改进算法Log_MAP[3,4]的度量信息计算速度,本文提出了嵌入式度量存储(ESMS)。

本文内容组织结构如下:在第二部分介绍了Log_MAP算法;第三部分介绍了ESMS方法;第四部分给出ESMS方法的性能分析;第五部分是我们的结论。

2.Log_MAP算法

Turbo编码器根据编码约束关系利用源数据比特形成冗余的校验比特,源数据比特与校验比特形成码字一同被发送。接收机收到的是被噪声“污染”了的码字,MAP译码器根据编码约束关系对接收数据从头部到尾部扫描得到前向搜索网格状态信息,然后从尾部到头部扫描得到反向搜索网格状态信息。译码器通过得到的网格状态信息从所有可能路径中找到最佳译码路径,最佳路径即是对所有输人数据的最佳估计的译码路径。

每个译码器的输出为码字中每个比特的估计概率概率值,常用对数释然比(LLR)来表示,第k个比特的LLR定义为:

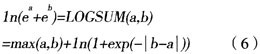

可以使用下面的公式简化Log_MAP算法中的幂运算。

在实际应用中,In(1+exp(-|b-a|))可以用查找表来实现。研究表明长度为8的表可以提供足够的精确度。在Log_MAP算法中对网格信息的归一化操作如下:

3.嵌入式状态信息存储(ESMS)

根据Log_MAP算法的原理,每步中的状态信息为0到负无穷间的一组数(实际应用中为0到一个有界的负数之间)。一个状态的度量接近0意味着该状态最优译码路径上的正确的状态的概率最大。如果αk(s)是最大值,αk(s)=0,s为前向搜索第k步正确状态的概率最大。如果βk(s)是最大值,βk(s)=0,s是反向搜索第k步正确状态的概率最大。

从(9)式可知,LLek的值取决于{αk-1(s′)}中的最大值和{βk-1(s′}中的最大值。如果编码器的输出为dsk=+1且译码器的估计正确,则LLek为正。如果编码器的输出为dsk=-1且译码器的估计正确,LLek为负。LLek的绝对值越大,第k步估计为正确估计的概率越大。如果LLek最大值与次大值之差越大,LLek会越快收敛于正确估计。因此,译码的关键在于得到最大信息的状态,而状态信息的绝对值不影响结果,即这个最大值是否为0并不影响结果。

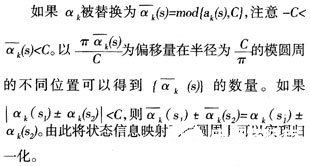

在Log_MAP译码算法中使用模圆周上的相对位置的状态信息度量而不是绝对位置的度量。令

由此,我们将状态转移到了新的位置,这里αk(0)和βk(0)永远为0。因此不需要存储{αk(0)}={α0(0), α1,(0)……αtength(0)和{β(0)}={β0(0),β1,(0)……βtength(0)。我们将这种技术称为嵌入式状态信息存储(ESMS)。它可以降低实际应用对存储器的要求。

ESMS使用二进制补码加法器和减法器。使用ESMS技术需要对Log_MAP算法进行如下修改。

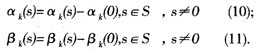

3.1状态度量信息更新

在ESMS度量更新的时候同时完成归一化操作,因此,在ESMS归一化过程中,不需要搜索每一步的最大状态信息,从而可以降低VLSI应用中的延迟和面积。

3.2外信息计算

由于在计算状态信息和外信息的过程中,αk(0)和βk(0)始终为0,所以相关的运算可以省略;因此ESMS可以减少译码运算量。

4.性能分析

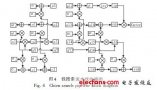

本文使用仿真来分析ESMS技术的性能。仿真中采用CDMA2000标准中的turbo码,。为性能评价,在设计数据路径时采用了Synopsys作为综合器。为了比较,同时采用了传统的Log_MAP算法。从而得出结论使用了ESMS技术的Log_MAP算法的译码器可以达到传统算法相同的性能。表3列出了采用ESMS技术的Log_MAP算法的译码器,采用MEPMUM技术的译码器以及采用传统方法译码器为存储度量信息所要求的存储器空间数值。从表3中显示MEPMUM和ESMS能极大的降低存储器用量,且ESMS能协助MEPMUM降低12.5%的存储器空间。

采用了ESMS和传统方法两种应用来实现Log_MAP译码器。为了比较,应用还采用了智能归一化[8]的Log_MAP译码器。在综合中选择速度最优化选项。表4列出了综合结果。表4显示智能归一化和ESMS相比传统方式能减少超过36%的面积和17%的延迟。采用了ESMS技术的Log_MAP算法比智能归一化实现多降低了1%的面积和延迟,但相比存储器空间竞降低了12.5%。因此,本文提出的这种新技术ESMS能够使Log_MAP译码器运算更快,面积更小,存储器空间消耗更小。

5.结论

本文提出的嵌入式状态信息存储技术能够提高Turbo译码器的运算速度,并减小面积占用,这种状态信息存储机制能够用于Log_MAP和Max-Log_MAP译码器的ASIC和FPGA设计中。

责任编辑:gt

-

嵌入式

+关注

关注

5209文章

20656浏览量

337002 -

存储器

+关注

关注

39文章

7756浏览量

172192 -

译码器

+关注

关注

4文章

313浏览量

52436

发布评论请先 登录

基于IP核的Viterbi译码器实现

译码器定义

基于DSP的Max-Log-MAP算法实现与优化

Viterbi译码器回溯算法实现

基于FPGA的RS码译码器的设计

Max-Log-Map算法优化

译码器的逻辑功能_译码器的作用及工作原理

嵌入式系统教程之嵌入式系统的IO模块详细资料说明

如何使用FPGA实现跳频系统中的Turbo码译码器

基于BCJR算法的MAP译码器嵌入式系统的应用设计

基于BCJR算法的MAP译码器嵌入式系统的应用设计

评论