无论您是选择将ADC内置于MCU还是作为外部组件,无论何时选择ADC,采样速率都是首要考虑因素,因为它将决定您再现测量信号的能力。射频应用,模拟传感器板和其他混合信号设备将需要至少一个具有适当选择的ADC采样率的ADC。

如果要使用混合信号板进行设计,则需要在所需的信号带宽,采样率和ADC的模拟输入带宽之间取得平衡。在使用谐波频率时,很少考虑最后一点,但是对于需要检测脉冲流,宽泛的谐波频率范围或任何其他宽带宽信号的情况,这一点非常重要。如果选择错误采样率的ADC,最终将导致混叠产生虚假信号伪像的情况。

这在模数转换器(ADC)和用于时域测量的示波器中会产生一些重要的后果。在ADC中,我们通常使用有限带宽的信号,因此需要在时域中对其进行数字表示。在示波器中,我们可能需要在时域中再现任何可能的信号(包括时钟或数字信号)。所有这些都取决于设置适当的采样率。

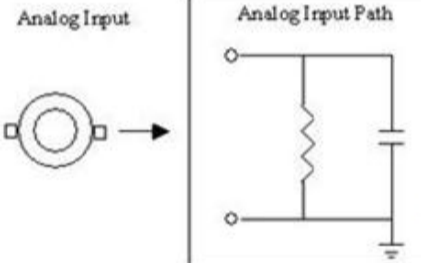

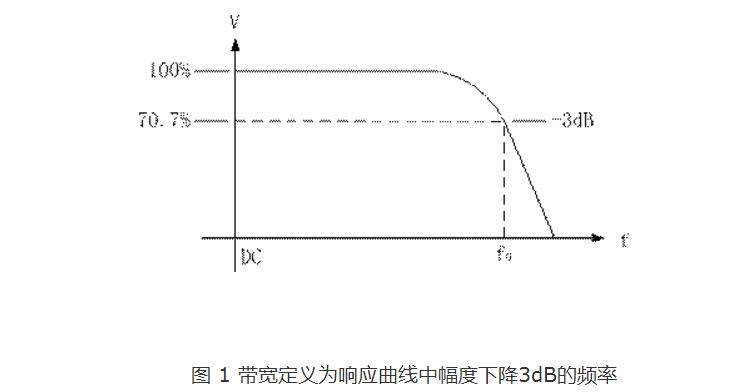

就像任何其他模拟组件及其信号一样,ADC本身也将具有一定的带宽。就像滤波器或放大器一样,模拟带宽(或全功率带宽FPBW)定义了-3 dB点,超出该点会有一些滚降。同样,就像放大器一样,ADC直到其带宽截止频率都不会具有无失真的输出。

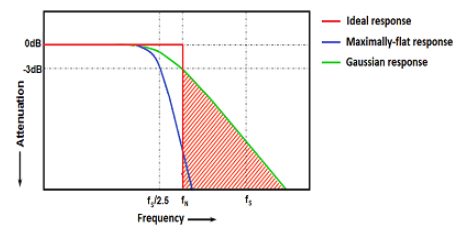

由于有限的输入带宽,除非您将采样率设置得非常低,否则ADC的带宽通常小于奈奎斯特频率。除奈奎斯特频率外,所有频率分量都将被混叠。下面显示了两种不同类型的响应,红色区域对应于ADC混叠的频率范围。

ADC中的理想,最大平坦度和高斯ADC输入频率响应曲线

对于红色曲线,ADC输入频率响应恰好在奈奎斯特频率处被截断。尽管您可以通过正确的过滤器集来接近,但这种理想的行为无法物理再现。大多数ADC的实际行为对于经常使用示波器的人们是熟悉的。响应是高斯或类似高斯的。处理PCB中的宽带信号的一个更好的选择是选择一个带宽接近蓝色曲线的ADC。在这里,我们有一个“有效”奈奎斯特频率,等于Fs / 2.5。

ADC采样率与输入带宽的关系

如果我们看上图,在为混合信号板选择ADC时,有两点要理解:

信号失真已经在混叠频率之前发生。这可以从ADC的高斯和最大平坦频率响应中看出。简单地增加采样频率将不会出现此问题。

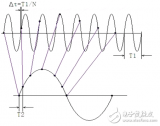

使用较低的采样频率可以降低成本,但会增加高频分量在信号输出上产生一些伪像的机会。任何在示波器轨迹上看到幻影轨迹,毛刺或人为调制的人都对信号再现中的这些伪像很熟悉。

再现此类信号需要正确的ADC采样率

使用ADC采样率降低PCB噪声

回到最初的问题:最佳采样率是多少?答案是……取决于!如果您的混合信号板在模拟信号上有过多的宽带噪声,则可以使用更高的采样率来降低这种噪声。对宽带模拟信号进行采样时,一个好的经验法则是将采样率设置为信号基本频率的2到5倍。

高速采样后,您可以将输出通过抗混叠滤波器。以更高的速率采样会将宽带噪声功率分布在更高的带宽上,使输出通过抗混叠滤波器将切断不需要的高频分量,包括高频噪声。

高采样率下ADC布局中的降噪

选择具有所需采样率的ADC之后,您必须考虑自己的布局策略。混合信号板上ADC的基本布局规则可能是让ADC跨接在接地层的数字和模拟部分,以确保这些不同类型的信号保持分离。像其他具有数字输出的组件一样,ADC容易受到接地反弹的影响,因此请确保使用旁路电容器来抑制该噪声源并提供准确的信号再现。将此旁路电容器与ADC的接地层接地,以提供尽可能低的环路电感。

如果ADC正在接收RF信号,请考虑使用共面波导配置来路由输入线。这将有助于将线路与其他模拟组件隔离开来,并减少串扰。要避免将时钟信号与时钟走线串扰,请小心在靠近ADC输入或输出走线的地方布线时钟信号。时钟和数字输出线之间的串扰在时钟线上产生正弦噪声信号。然后,它可以作为相位调制耦合回模拟输入,从而在高采样率下产生错误的信号再现。布线时,尽量减少时钟线和信号线之间的宽边耦合。

编辑:hfy

-

放大器

+关注

关注

146文章

14300浏览量

221020 -

混合信号

+关注

关注

0文章

533浏览量

65692 -

adc

+关注

关注

100文章

7405浏览量

553806 -

RF

+关注

关注

66文章

3197浏览量

171077 -

模拟传感器

+关注

关注

0文章

38浏览量

14250

发布评论请先 登录

ADC采样率与信号频率:关键概念与设计要点

采样定理-------------被检测信号和ADC采样率的关系?

示波器的带宽和采样率与奈奎斯特定理的详细资料说明

什么叫采样率 数字信号处理时钟与采样率的关系

ADC采样率与输入带宽的关系 高采样率下ADC布局中的降噪

ADC采样率与输入带宽的关系 高采样率下ADC布局中的降噪

评论