IBIS模型概述

IBIS是一种器件模型标准,允许使用行为模型进行开发,这些行为模型描述了器件内部互联的信号。IBIS模型保留专用的电路信息,不像SPICE这种结构化模型,IBIS模型是基于测量或电路仿真得到的 V/I曲线数据。

每个IOB标准都有IBIS模型,器件的所有I/O标准的IBIS模型组合在一起便是IBIS文件。IBIS文件还包含器件中所使用的管脚列表,这些管脚连接到配置为支持特定I/O标准的IOB上,该标准会将管脚与特定的IBIS buffer模型关联在一起。

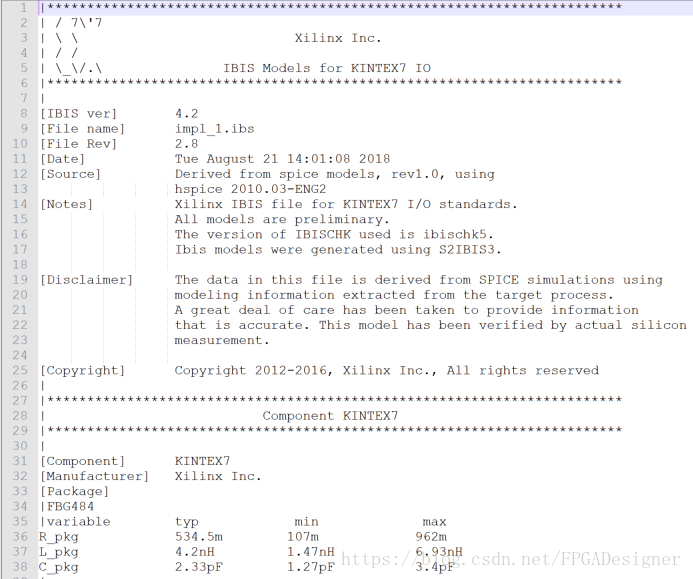

IBIS标准规定了输出文件的格式,包括一个文件头部分和一个组件描述部分。IBIS开源论坛小组开发了Golden Parser这款工具,可以通过检查IBIS数据格式中的语法来验证IBIS模型文件。

当使用Vivado IDE导出IBIS模型时,软件会生成一个.ibs文件,其中包含了:设计使用管脚列表、FPGA内部与管脚连接的信号、与管脚连接的IOB的IBIS buffer模型。

导出IBIS模型

设计者通常都会关心信号完整性问题,比如交叉干扰、地弹、同时转换噪声(SSN)。 PCB工程师使用IBIS模型仿真设计,可以更好的在系统级角度了解信号完整性情况。IBIS模型有助于描述电流电压(I-V)曲线和封装器件的信息。

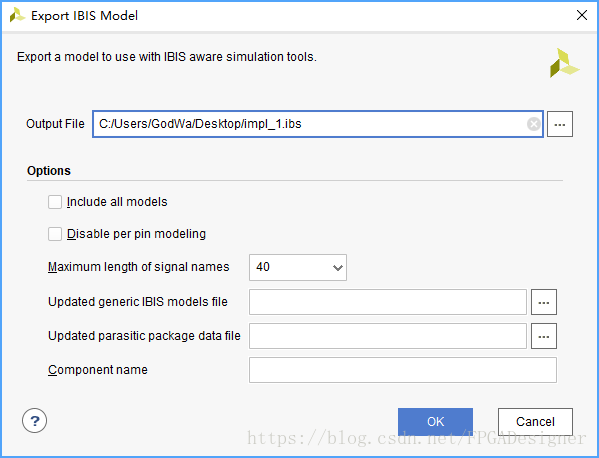

Vivado会使用设计中的网表和实现细节,将这些信息与可用的每个管脚的封装信息联合起来,创建一个IBIS模型。打开某一阶段的设计,点击File->Export->Export IBIS Model:

Output File:规定输出IBIS文件的名称和路径;

Include all models:默认情况下,只有设计中用到的buffer模型才会添加到IBIS文件中。选中此选项,会添加FPGA中所有可用的I/O buffer模型;

Disable per pin modeling:禁止包含每一个管脚的封装模型。勾选此选项,所有管脚的封装会简化为单个RLC传输线模型,并且在IBIS文件的Package部分中定义;

Maximum length of signal names:会将信号名称截断到限制的长度,可以设置为40、20或Unlimited.

Updated generic IBIS model file:可选地提供一个器件的IBIS模型;

Updated parasitic package data file:可选地提供一个用于每个管脚提取的pkg文件。上述两个文件在Vivado安装目录下data/parts目录中都有,一般只有在该目录中没有这些文件的情况下才需要在此处设置。

Component Name:默认名称为器件的系列,可以在这里设置改变IBIS文件中Component部分的名称。

导出的ibs文件可以用文本编辑器打开查看信息,包含文件头和Component(名称默认为FPGA系列KINTEX7)两部分,:

结合本系列第13篇~第16篇,除了IBIS模型外,Vivado还提供了CSV文件、DRC检查、SSN分析等工具,帮助设计者完成PCB设计。此外,为了在整个PCB环境下更好地优化I/O赋值工作,Xilinx还支持Cadence Allegro FPGA System Planner和Mentor Graphics I/O Designer两款第三方工具。有机会后面再做介绍。

编辑:hfy

-

PCB设计

+关注

关注

396文章

4944浏览量

96030 -

IBIS

+关注

关注

1文章

55浏览量

20681

发布评论请先 登录

静力水准仪的数据存储与导出方式解析

使用Vivado 2018.2编译E203的mcs文件,遇到的问题求解

allegro导出STEP器件丢失、错乱问题

在Windows10上运行vivado使用tcl文件创建E203项目路径错误的问题

vcs和vivado联合仿真

如何在vivadoHLS中使用.TLite模型

关于Detectron2的GenerateRCNN模型转RKNN问题

如何进行YOLO模型转换?

Vivado无法选中开发板的常见原因及解决方法

如何在Unified IDE中创建视觉库HLS组件

固定式测斜仪的数据存储和导出方式有哪些?

Vivado IBIS模型创建及导出方式

Vivado IBIS模型创建及导出方式

评论