实验室回来一批板子,上面有RGMII接口、SGMII接口等各种接口,怎么测试这些网口是否正常呢?的确需要一些经验。比如RGMII接口,最重要的是看在哪里去做的时钟和数据偏移。这时,常常需要使用VIO去读取PHY里面对应寄存器的值,看是否工作在正常RGMII接口时序模式。

测试场景

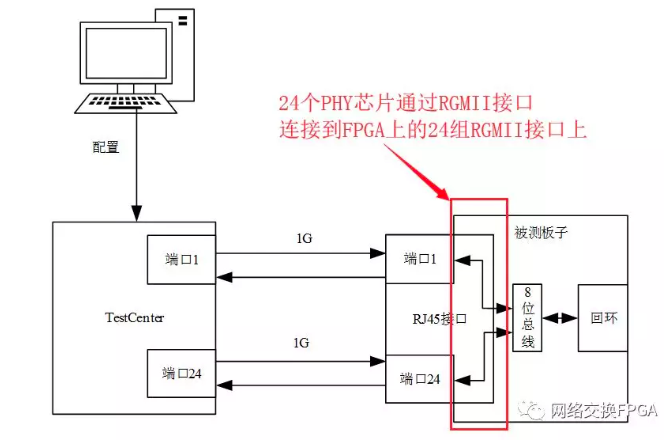

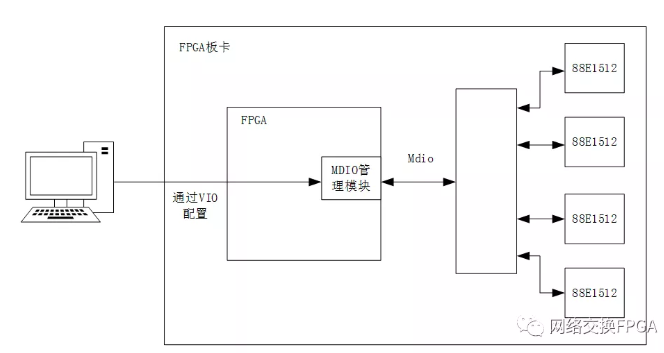

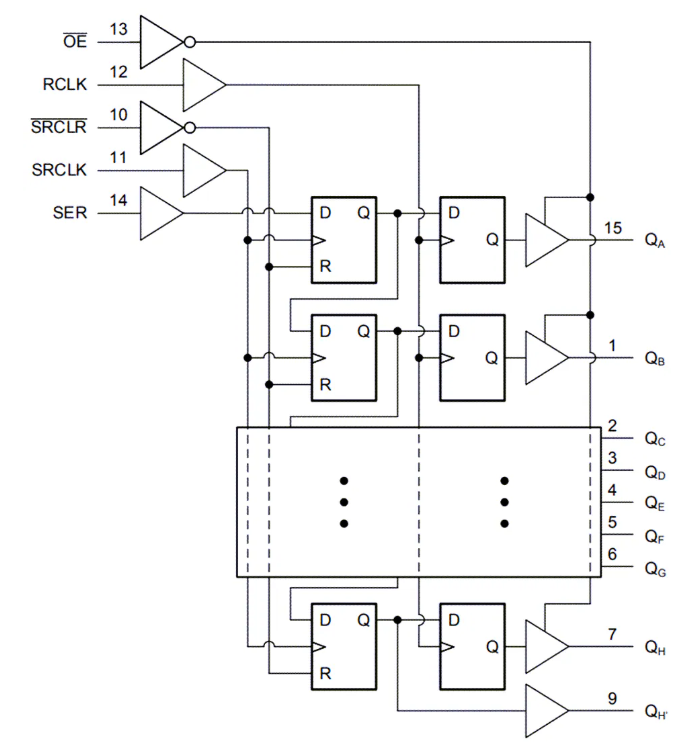

测试拓扑图如下

试场景连接图

测试方法:使用TestCenter向被测板子上的千兆以太网口打流,在FPGA内部通过自回环从源端口返回给TestCenter,通过看TestCenter控制界面上显示结果判断自回环是否正确。

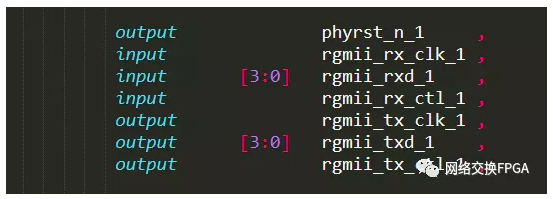

测试RGMII接口时使用的PHY芯片为MARVELL 公司的88e1512PHY芯片,RGMII顶层接口信号如图1所示。

图1 测试代码顶层接口信号

采用以往经验发现问题

按照以往的RGMII接口使用经验,通过约束将接口的输出时钟延迟了2ns,如图2所示。使用TestCenter对以太网口进行测试,以太网口无法正常发送数据。具体表现为,TestCenter接收的数据帧数目,和发送的数据帧数目相等,但是接收的bit数明显比发送的bit数少。抓取测试代码的内部信号发现,FPGA接收到的以太网数据帧均正常,所以推测FPGA给PHY芯片的发送数据的时序不正常。

图2 发送时钟偏移2ns约束代码

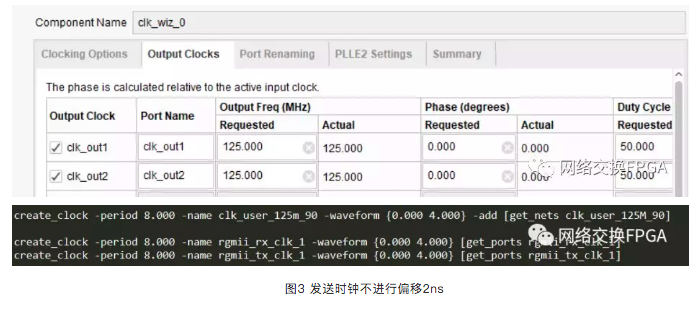

修改代码,不对发送时钟进行2ns的偏移,如图3所示。使用TestCenter对以太网口进行测试,以太网口正常地工作。

图3 发送时钟不进行偏移2ns

问题原因定位

推测在不同的PHY芯片的工作模式下,对时钟的要求不一样。

之前使用的REALTEK的RTL8211E PHY芯片,需要对发送时钟进行2ns的延迟,查找该 PHY芯片手册, PHY芯片对发送时钟有图4所示的要求。表格中明确指出,需要自己添加时钟和数据之间的2ns时延。

图4 RTL8211E的发送时钟

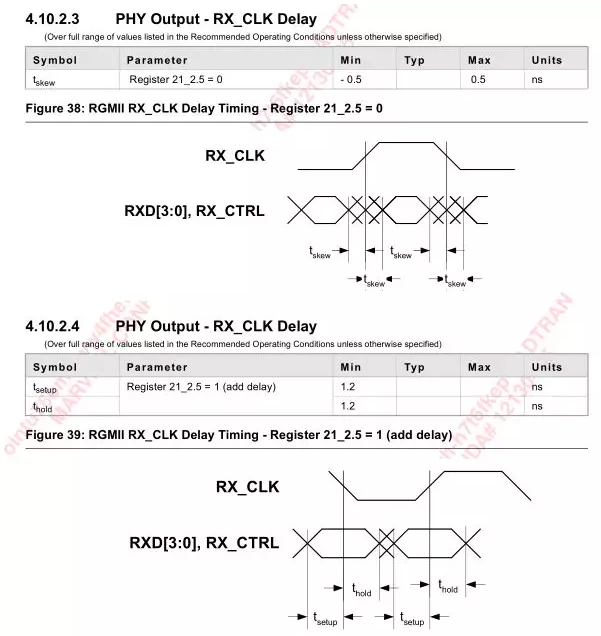

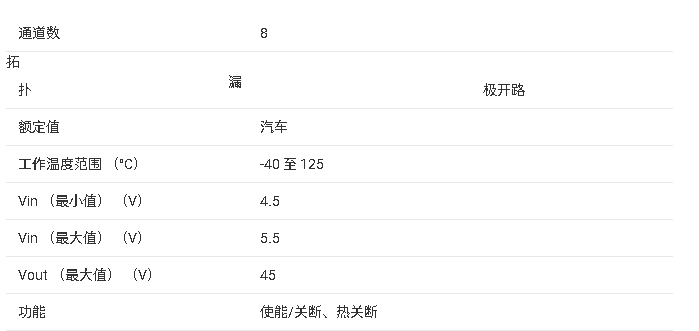

查找目前调试板子上所使用MARVELL的88e1512 PHY芯片的芯片手册,发现RGMII接口有4种不同的时钟工作模式。

图5 88e1512的4种时钟工作模式

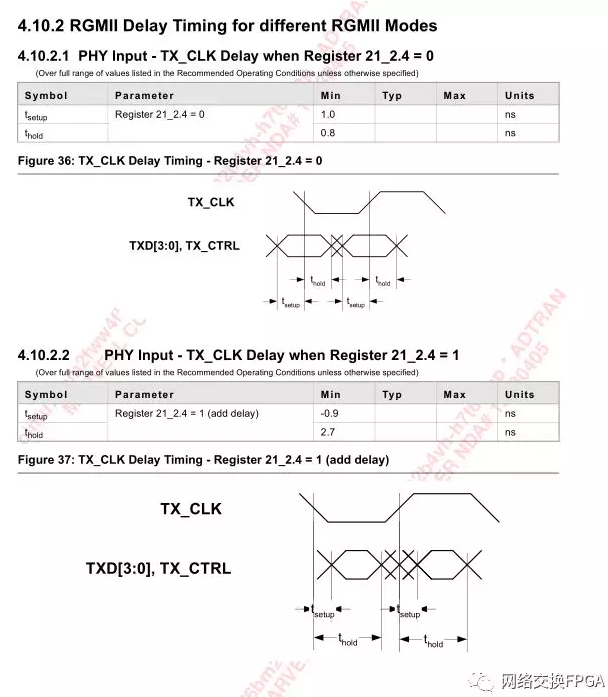

4种时钟工作模式下的信号时序图如图6、图7所示,结合上板现象,推测当前的工作模式为add delay模式,即Register21_2.4=1。

图6 RGMII发送时序

图7 RGMII接收时序

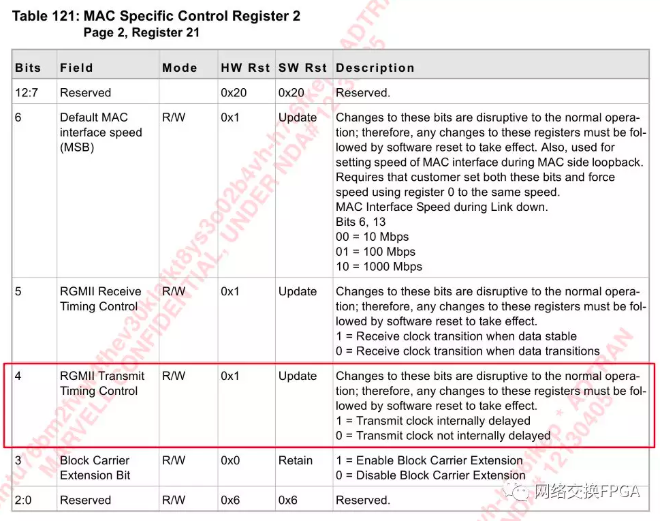

图8 寄存器的时钟模式配置

由上面图6、图7和图8可以看出,跟前面RTL8211E PHY芯片不同的是,MARVELL的88e1512 PHY芯片可以配置PHY与FPGA的RGMII接口时钟信号和数据信号是否已经相对偏移2ns。也就是说,可以通过读取PHY芯片相应寄存器的方法来看默认的工作模式。

经验总结:遇到RGMII接口调试时,最关键的是要查看PHY芯片的型号,查阅PHY芯片手册,通过MDIO读取PHY芯片寄存器的值,看RGMII接口上数据和时钟是否偏移2ns,再决定FPGA对应管脚约束是否进行偏移!

用VIO方法读取或配置PHY芯片的寄存器

在没有CPU的情况下,对PHY芯片中寄存器在线读取的最好办法使用VIO通过MDIO接口对PHY芯片中的寄存器进行读取。具体方法可以查看本公众号之前文章:

一种动态调整RGMII接口时序的方法

Vivado进行FPGA调试“犯罪现场”,在仿真环境中重现方法

使用VIVADO中VIO模拟CPU接口进行在线寄存器读写调试(附源代码)

干货:Vivado 直接修改RAM初始化文件,避免重新综合、实现的方法

上图为测试场景,由FPGA芯片通过24个Mdio接口控制24个88E1512 PHY芯片。

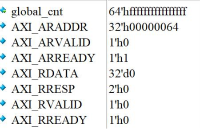

具体的测试步骤为:通过VIO配置MDIO管理模块PHY地址、寄存器地址,然后选择读操作读取某一PHY芯片的寄存器的值,结合PHY的工作状态,判断该寄存器是否被正确读取。由于执行读操作时是采用先写入地址,在读取数据的方式,因此只测试读操作就可以完整的测试MDIO管理模块的功能。以下是VIO对应的调用代码。

//-----------------------------

mdio_module_VSC8658 U_mdio_module (

.mdc(mdc_o),

.mdio(mdio),

.reset(reset),

.mdir (mdir),

.execute(execute), //

.req(req), //读 tb用

.phy_addr(phy_addr),

.reg_addr(reg_addr),

.data_phy(data_phy),

.data_rd(data_rd),

.op_done(op_done)

);

//-----------------------on board-----------------------------------

vio_0 u_vio (

.clk(clk), // input wire clk

.probe_out0(req), // output wire [0 : 0] probe_out1

.probe_out1(phy_addr), // output wire [4 : 0] probe_out2

.probe_out2(reg_addr), // output wire [4 : 0] probe_out3

.probe_out3(data_phy) // output wire [15 : 0] probe_out4

);

//-----------------

//----------------------mdc generate--------------------------------

//mdc should be 0~12.5MHz, the module is n*2 Divide

mdio_clk #(.Divider(25)) U_mdio_clk(

.reset (reset),

.clk(clk) ,

.clk_o(mdc_o)

);

//-------------------------------------------------------------------

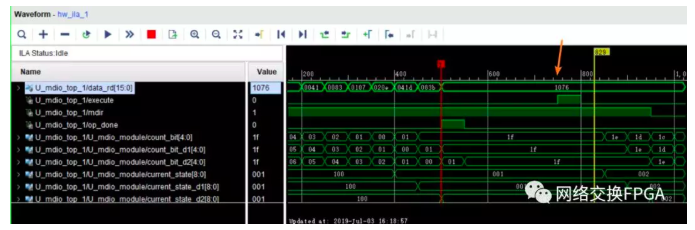

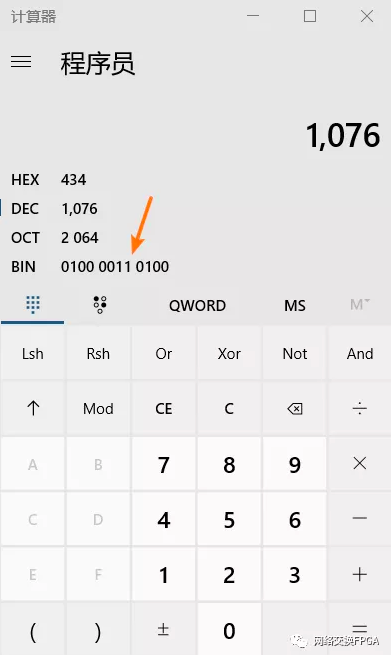

通过VIO和MDIO读取相应寄存器的值,如图10所示,读取到的值为1076,换算成2进值为0000_0100_0011_0100,对应的工作模式为图8所示的Transmit clock internally delayed,即 add delay模式,不需要对时钟进行2ns的偏移。

图9 寄存器的地址

图10 读取的寄存器数值

图11 用windows自带的计算器看二进制

确认完之后,Testcenter打流,一切OK。但有时候,因为PCB设计的问题,比如RGMII接口的时钟未采用专用的时钟管脚,或者是对应的4bit数据信号不在FPGA芯片的同一个BANK,就会导致RGMII接口无论如何调整时钟与数据之间的相位关系,该RGMII接口都无法正常工作。所以,能够正常工作的前提是硬件的连线关系及PCB板是OK的。

FPGA使用RGMII接口与PHY芯片连接时经验总结

事实上,相对于Altera的FPGA,Xilinx的FPGA在使用RGMII接口与PHY芯片相连时会比较讲究。以下归纳几点与大家分享。

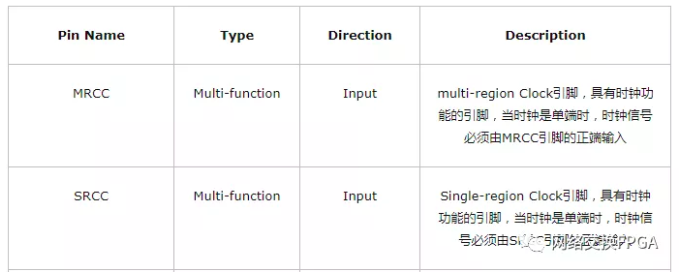

1、rgmii信号中的接收时钟phy_rxclk为单端时钟,如果将此时钟接到FPGA中多功能时钟引脚(MRCC或SRCC)上时,必须从正端(P)输入;

每个PHY芯片的tx和rx信号接在FPGA的同一个bank中,其中tx_clk和rx_clk需要接入bank中时钟专用管脚的P端,且其N端不能够接其它信号;

2、rgmii中接收信号(rxd、rxclk、rxctl)必须在FPGA中同一个bank或者相邻bank上,如果是在相邻bank上,rxclk必须接到MRCC中;

每个PHY芯片有4个rxd、4个txd、2个ctl信号,每个PHY共10个,4个PHY共40个信号;接收发送每个PHY各有两个时钟,总共1个PHY占用12个引脚。理论上1个bank可以接4个PHY芯片;

3、注意PHY芯片的供电电压与FPGA的供电电压是否相同;

4、每个PHY芯片采用单独的晶振产生参考时钟;(本公众号之前文章SDN先驱Nick教授以及netFPGA无法完美实现6802时间同步一文中就曾指出netFPGA就疑似存在此问题,由于抖动过大,多个端口无法实现6802同步);‘’

RGMII接口与GMII接口

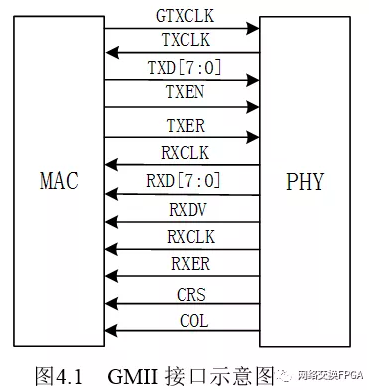

在MAC核与PHY芯片的通信过程中,存在多种接口形式,如MII、GMII、RGMII、XGMII等,千兆以太网端口中以GMII(GigabitMedia Independent Interface)和RGMII(ReducedMedia Independent Interface)最为常见。GMII能够支持10Mbps、100Mbps、1000Mbps的数据传输,其关键接口信号如图4.1所示。

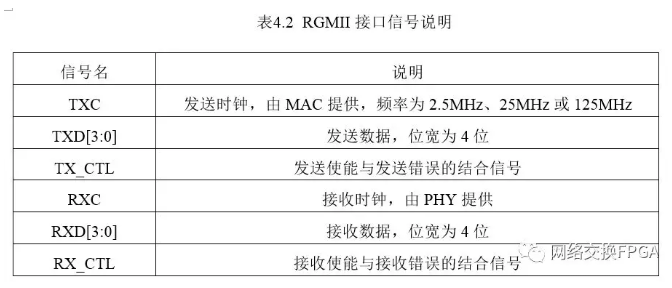

相比与GMII,RGMII接口的信号线大幅减少至12根,移除了其中不必要的TXER、RXER、COL、CRS,并将数据线宽度由8位缩减至4位,但同样能够支持10Mbps、100Mbps和1000Mbps传输,其接口信号如下图4.2所示。

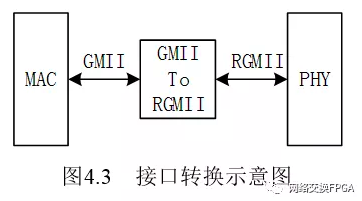

RGMII接口中的双沿数据信号适于传输,但并不适于数据处理,因此在MAC核内处理PHY侧数据时首先需要将双沿数据变换为单沿数据。在Crossbar交换机实现时硬件平台采用的是RGMII接口,故需要实现RGMII接口与GMII接口的相互转换,如图4.3所示。

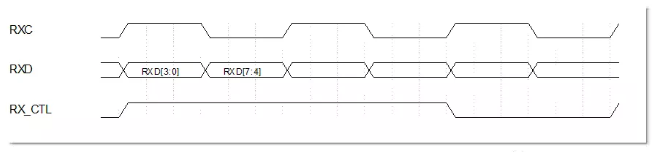

RGMII虽然相比于GMII缩减了大量信号线,但仍能实现1000Mbps数据传输,原因在于RGMII采用双沿传输技术,在时钟的上、下沿同时传输数据,那么在一个时钟周期内就能完成8bits数据的传输,与GMII的收发效果相同,如图4.4所示。而在RGMII中单向只有一个指示信号RX_CTL(TX_CTL),在双沿传输时可将GMII中的RXEN与RXER也分别在RX_CTL的上、下沿进行传输即可。

在上图4.4中,RGMII数据在时钟的上升沿传输GMII中的3~0位,在时钟的下降沿传输GMII中的7~4位,一个时钟完成8bits数据的传输。RX_CTL信号持续拉高,表明当前帧正确无误。

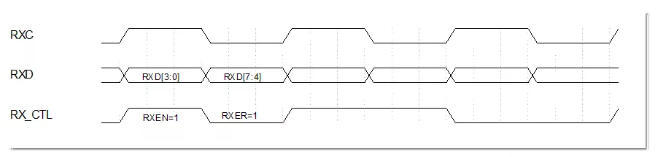

在上图4.5中,数据传输与图4.4相同,而RX_CTL在时钟的下降沿跳变为0,代表了GMII中的RXER信号为1,表明传输错误。而在RX_CTL持续时间结束时,是在时钟的上升沿拉低,此时在一个完整的时钟周期内RXEN=0,RXER=0,可知RX_CTL与RXEN、RXER的关系为:RXEN xorRXER = RX_CTL,xor代表异或运算。

为实现RGMII信号与GMII信号的相互转换,本文借助了Xilinx提供的基于FPGA的几类原语,原语指Xilinx针对其器件特征开发的一系列常用模块的名字。下面列出所用原语的名称及介绍。

(1)IDDR、ODDR

DDR(Dual Data Rate)即双倍速率,数据在时钟的上升沿、下降沿均发生变化,IDDR用作将一路双沿时钟数据转换为两路普通数据,ODDR用作将两路普通数据帧转换为一路双沿时钟数据,如图4.6所示。

(2)BUFIO

一种特殊的时钟buffer,该buffer独立于全局时钟之外,适合用作接收源同步数据,但需要之处的是,该buffer输出的时钟无法直接驱动逻辑资源,适合驱动IDDR等专用组件。

(3)BUFR

一种特殊的时钟buffer,独立于全局时钟外,该buffer输出的时钟用作驱动该区域内的逻辑资源。

(4)IBUFG

一种全局时钟buffer,在FPGA的时钟输入处都应添加IBUFG进行缓冲,使得缓冲后的时钟线拥有最小的延迟与抖动,且驱动能力大幅增加。

(5)IODELAY1、IDELAYCTRL

IODELAY1为一种可编程的绝对延时组件,可对某一线路添加一定的延时,其延时值由IDEALYCTRL决定。IDELAYCTRL的延时精度为参考时钟的1/64,如提供200MHz的参考时钟,延时精度为5ns/64 = 78ps,二者需配合使用。

在接口转换的硬件实现过程中,分为接收转换与发送转换,二者存在较大区别,下面分别给出接收转换与发送转换的实现过程。

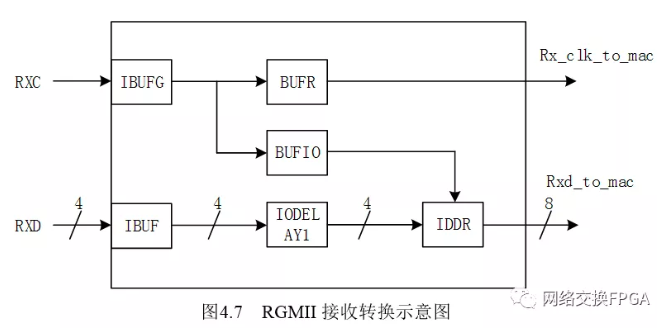

接收转换即为对RXD、RX_CTL的转换,在千兆模式下RGMII接口接收数据时,随路时钟即RXC为125MHz,且为双沿传输,因此不仅要使用IDDR取出双沿数据,更要对时钟进行额外处理,转换过程如图4.7所示。

在图4.7中,并未给出RX_CTL的转换,其转换原理与RXD转换类似,在IDDR转换后Q1为GMII下的RXDV,Q1 xor Q2为GMII下的RXER。图中,IBUFG用于将外部输入的性能较差时钟RXC转换为内部可用的高效时钟RXC_BUFG,BUFIO用于将RXC_BUFG转换为适合采集源同步数据的时钟RXC_BUFIO,BUFR用于将RXC_BUFG转换为适合区域内逻辑资源使用的时钟Rx_clk_to_mac,相比于RXC_BUFG更适合驱动Rxd_to_mac。IBUF与IBUFG功能相似,但IBUFG只适用于时钟信号,IBUF为数据线buffer。IODELAY1用作给RXD信号添加一定的延时,抵消时钟线在经过BUFIO时与在硬件布线时引入的延时,其延时值需要视硬件特性决定,在本文中使用Zedboard实现Crossbar交换机时延时值设置为0。IDDR在图中只给出一个,在实现时需要用到5个IDDR分别对应于RXD0~RXD4以及RX_CTL。

发送转换即为对TXD、TX_CTL的转换,在RGMII的发送过程中,时钟信号由FPGA内部给出,因此不需要对时钟线添加额外的buffer,需要指出的是,RGMII的发送时钟与发送数据并非是沿对齐的,而是如图4.8所示的中心对齐,采用这样的时序好处在于对于对端接收来说,双沿采样更加稳定。

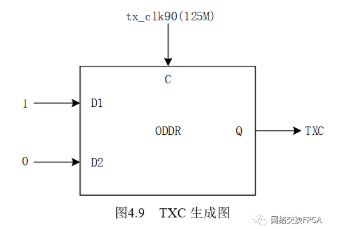

在实际的发送转换中,首先利用125MHz的时钟驱动ODDR获得TXD以及TX_CTL(TX_CTL的转换中D1为GMII中的TXEN,D2为GMII中的TXEN xorTXER),此时的TXD与TX_CTL与最初的125MHz时钟是沿对齐的。特殊之处在于,TXC同样由ODDR产生,该ODDR的驱动时钟为最初的125MHz时钟相移90度后的另一时钟tx_clk90,如图4.9所示。之所以采用ODDR产生TXC是因为此时的TXC就与TXD、TX_CTL经过了相同的ODDR延时,最终TXC与TXD、TX_CTL就是中心对齐的。

编辑:hfy

-

寄存器

+关注

关注

31文章

5619浏览量

130422 -

PHY

+关注

关注

2文章

341浏览量

54327 -

RGMII

+关注

关注

0文章

31浏览量

12758

发布评论请先 登录

IDT SSTVF16857AGLF DDR寄存器:特性与应用解析

PF5020 – TBB 模式:用于访问镜像寄存器的页面寄存器的前 3 位是什么?

RDMA设计38:寄存器功能验证与分析

汇编寄存器的知识

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

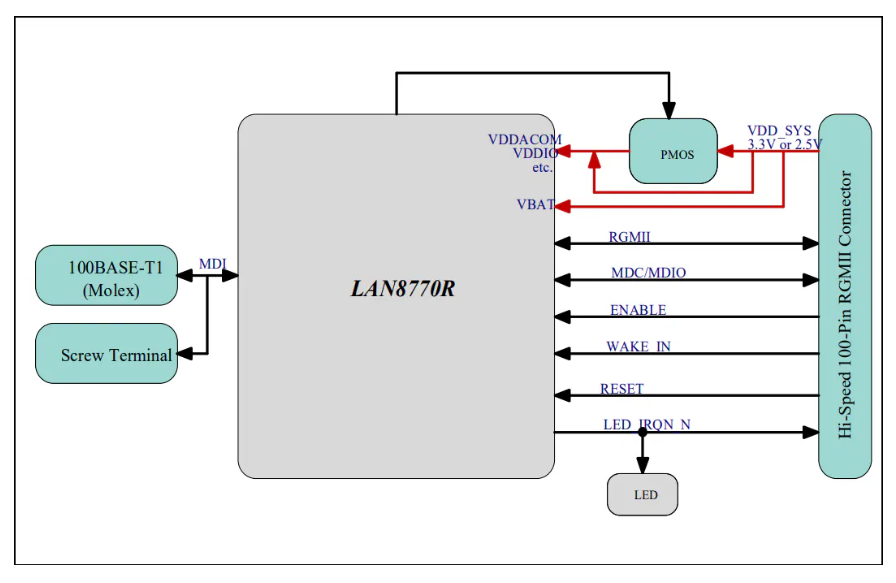

EVB-LAN8770-RGMII评估板技术解析与应用指南

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

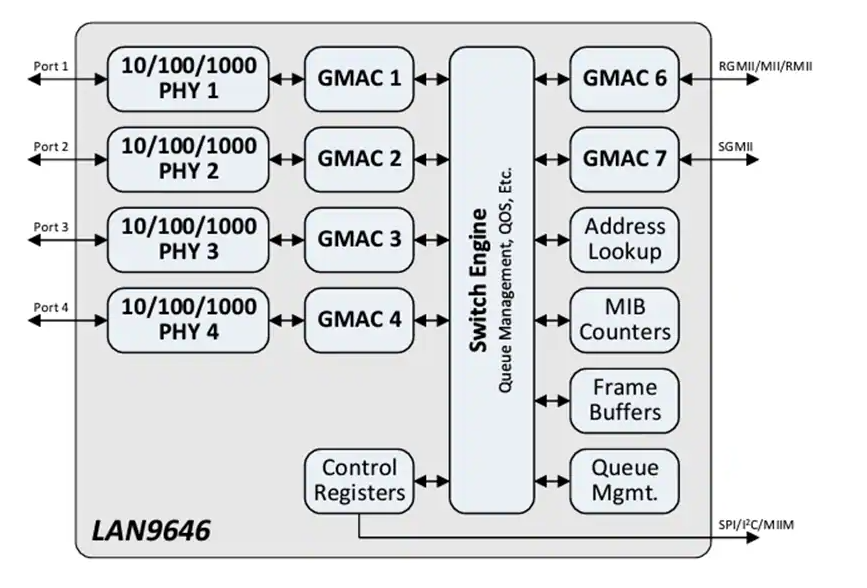

基于LAN9646六端口千兆以太网交换机的技术解析与应用

NVMe高速传输之摆脱XDMA设计31: 寄存器功能验证与分析1

SN74HCT595 8位移位寄存器技术解析与应用指南

如何通过CYUSB3014的设备寄存器读取主机发起的数据传输的ACK?如何通过寄存器读取主机发送的复位命令?

FPGA调试方式之VIO/ILA的使用

使用寄存器点亮LED灯

如何使用VIO去读取PHY里面对应寄存器测试RGMII接口

如何使用VIO去读取PHY里面对应寄存器测试RGMII接口

评论