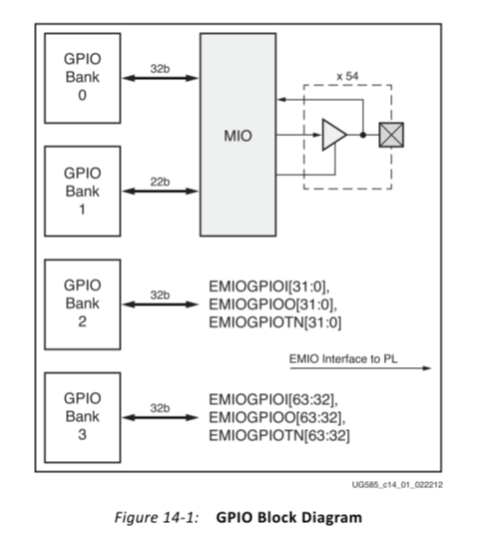

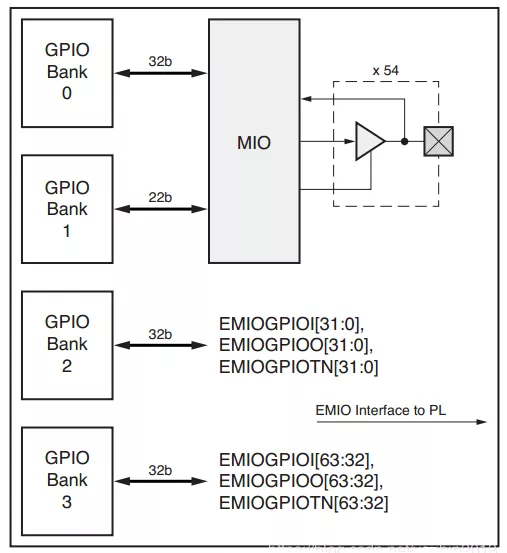

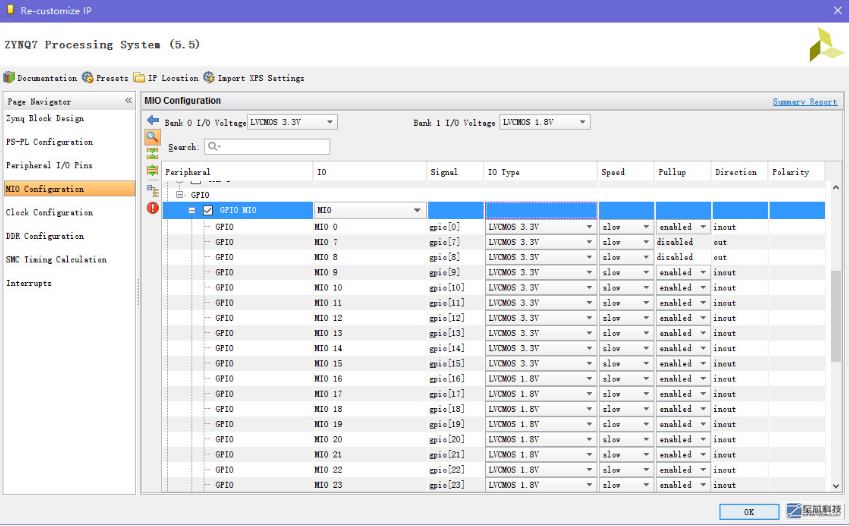

在编写程序之前,先来了解GPIO的BANK分布,在UG585文档GPIO一章中可以看到GPIO是有4个BANK,注意与MIO的BANK区分。BANK0控制32个信号,BANK1控制22个信号,总共是MIO的54个引脚,BANK2和BANK3共能控制64个PL端引脚,每一组都有三个信号,输入EMIOGPIOI,输出EMIOGPIOO,输出使能EMIOGPIOTN,共192个信号。

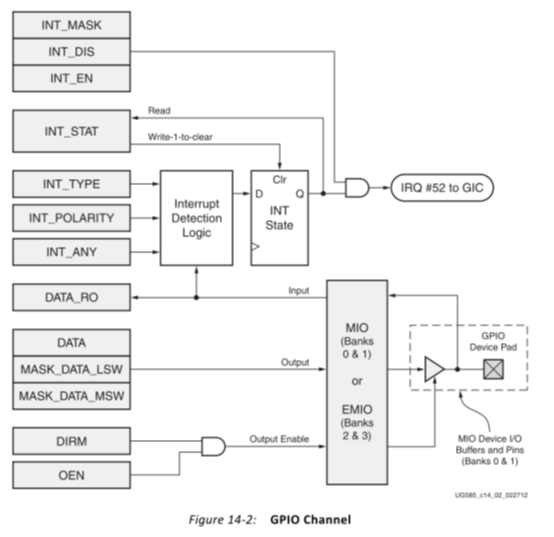

下图为GPIO的控制,实验中会用到输出部分的寄存器,数据寄存器DATA,数据掩码寄存器MASK_DATA_LSW,MASK_DATA_MSW,方向控制寄存器DIRM,输出使能控制器OEN。

程序中利用以下函数设置方向和输出使能:

int main()

{

XGpioPs_Config *GPIO_CONFIG ;

int Status ;

//通用手法,查找GPIO列表

GPIO_CONFIG= XGpioPs_LookupConfig(MIO_0_ID);

//Exception的检测

Status= XGpioPs_CfgInitialize(&GPIO_PTR, GPIO_CONFIG, GPIO_CONFIG->BaseAddr) ;

if (Status != XST_SUCCESS)

{

return XST_FAILURE ;

}

//设置MIO的PIN引脚方向

XGpioPs_SetDirectionPin(&GPIO_PTR,0, GPIO_OUTPUT) ;

XGpioPs_SetDirectionPin(&GPIO_PTR,13, GPIO_OUTPUT) ;

//使能MIO的PIN引脚输出

XGpioPs_SetOutputEnablePin(&GPIO_PTR,0, GPIO_OUTPUT) ;

XGpioPs_SetOutputEnablePin(&GPIO_PTR,13, GPIO_OUTPUT) ;

while(1)

{

XGpioPs_WritePin(&GPIO_PTR,0, 1) ;

XGpioPs_WritePin(&GPIO_PTR,13, 0) ;

usleep(100000);

XGpioPs_WritePin(&GPIO_PTR,0, 0) ;

XGpioPs_WritePin(&GPIO_PTR,13, 1) ;

usleep(100000);

}

return 0;

}

实现两个LED的闪烁

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5589浏览量

129058 -

GPIO

+关注

关注

16文章

1313浏览量

55727 -

MIO

+关注

关注

0文章

12浏览量

8343 -

Zynq

+关注

关注

10文章

625浏览量

49239 -

bank

+关注

关注

0文章

16浏览量

15206

发布评论请先 登录

相关推荐

热点推荐

ZYNQ开发案例:GPIO的结构体系及使用案例

GPIO的结构体系 zynq的GPIO,分为两种,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)。 ZYNQ的

Xilinx ZYNQ开发GPIO的三种方式:MIO、EMIO、AXI_GPIO

前言: ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源

浅谈GPIO的操作

本帖最后由 芯灵思FAE 于 2016-7-31 12:48 编辑

浅谈GPIO的操作很久很久以前,我们如果在Linux系统下操作GPIO是这样的......gpio.c申请

发表于 07-31 12:47

玩转Zynq连载2——Zynq PS的GPIO外设

的设置,可以实现对一个bank中特定一个或多个GPIO的控制。 其它几个主要寄存器的功能如下。 ● DATA寄存器。当GPIO配置为输出时,该寄存器用于配置

发表于 04-18 16:33

将LVDS输出驱动器连接到ZYNQ 7030的HP Bank的方法?

你好我需要将LVDS输出驱动器连接到ZYNQ 7030的HP Bank。LVDS输出驱动器的电源电压为VCCO_LVDSout_DRIVER = 2.5V,HP bank为VCCO_HP_BA

发表于 08-12 09:34

ZYNQ的GPIO相关资料推荐

ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚

发表于 02-08 07:27

ZYNQ 的三种GPIO :MIO、EMIO、AXI

。 我们先看一下MIO和EMIO:下图EMIO和MIO的结构。其中MIO分布在BANK0,BANK1,而EMIO则分布在BANK2、

发表于 02-08 10:23

•3706次阅读

被zynq的GPIO唬住,告诉你zynq的3种GPIO

我们先看有哪三种GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接挂在PS上的GPIO。而AXI_GPIO是通过AXI总线挂在PS上的

发表于 07-07 08:23

•5839次阅读

zynq中三种实现GPIO的方式

GPIO功能,PS部分通过M_AXI_GP接口来控制该GPIO IP模块;另外EMIO模块虽然使用PS部分GPIO但也使用了PL部分的管脚资源。MIO方式实现GPIOvivado中

LINUX GPIO如何驱动源码移植

GPIO是嵌入式系统最简单、最常用的资源了,比如点亮LED,控制蜂鸣器,输出高低电平,检测按键,等等。GPIO分输入和输出,在Montavista linux-2.6.18中,有关GPIO

发表于 06-26 17:43

•4次下载

ZYNQ的GPIO简介

ZYNQ 分为 PS 和 PL 两部分,那么器件的引脚(Pin)资源同样也分成了两部分。ZYNQ PS 中的外设可以通过 MIO(Multiuse I/O,多用输入/输出)模块连接到 PS 端的引脚

发表于 12-04 18:51

•16次下载

ZYNQ学习笔记_GPIO之输入输出

ZYNQ学习笔记_GPIOGPIO介绍MIO介绍EMIO介绍控制GPIO接口的寄存器原理GPIO介绍GPIO的英文全称为General-purpose input/output,即一种

发表于 12-04 19:36

•10次下载

浅谈Zynq中GPIO的BANK分布

浅谈Zynq中GPIO的BANK分布

评论