在高速数字电路设计流程中,第一步需要做的就是根据系统的复杂程度,成本因素等相关方面决定印制电路板(PCB)的叠层结构(Stack),而在PCB stack设计的过程中,特征阻抗也是一个重点关注的问题。

1 叠层结构的选择

电路板的叠层结构分为2层,4层,6层,8层,10层等等。目前常用的用于主板设计的主要有4层与6层,至于8层。而对于更为复杂的系统,像小面积的Add-in Card,大型通信设备中的某一模块,像SDH,Multi-serve Router,这些设备常用12层甚至是更多层。本文主要的出发点就是以较为简单的例子,介绍PCB叠层设计中的参数问题。

1.1 4层电路板

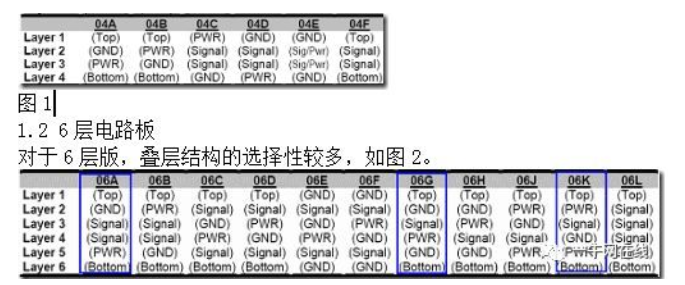

对于4层电路板,这是市场上最常用的一种叠层结构,它的结构无外乎下面几种方案,如图1,具体取决于哪种方案最好,主要是看布线层面的选择,参考平面的选择以及EMC/EMI的考虑。这里把signal层放在内层有利于屏蔽辐射,便于EMC的设计,但不利于系统的Debug。常用的方案是04A。

最常用的叠层结构主要是06A,06G,06K。06A有四层布线层,便于布线。06G有两个GND,这样的话Top与Bottom层参考平面都是GND,是一种很好的选择。对于06K,这样做,主要是3个信号层布线有点紧张,让第四层作为备用的信号层,最后不用的地方都铺上铜箔,即确切的说,该种叠层结构的layer4是signal/GND。对于其他的叠层结构,像10层,18层,这里不多介绍,下图以便参考。

2 特征阻抗的计算

设计完叠层结构,具体的就要设计各个叠层的厚度了,这里主要的切入点就是特征阻抗,电源平面和地平面的目标阻抗了。

对特征阻抗的理解可以类似于软水管,特征阻抗类似软水管对水流的阻力,电流类似于水流,走线与参考平面的距离类似于软水管与地平面的距离——可想象为体现在压强方面。

2.1 影响特征阻抗因素

影响特征阻抗的因素很多,主要体现在下面几个方面:

介电质常数,与阻抗值成反比 [Er值愈高 , Z0值愈低]

线路层与接地层间介电层厚度,与阻抗值成正比,参考基板及PP之压合厚度,[介层愈厚 , Z0值愈高],介电层厚度类比于软水管离地平面的高度,介电层厚度越大,表示离地平面越高,从而导致水流变缓,好比软水管对水的阻力变大,从而特征阻抗变大。

线宽,与阻抗成反比 [线宽愈细 , Z0值愈高],线宽越细,表示软水管截面积变小,对水流的阻力变大,从而水利变小,特征阻抗变大。

铜厚,与阻抗值成反比 [铜愈厚 , Z0值愈低],铜厚变小,表示软水管截面积变小,对水流的阻力变大,从而水利变小,特征阻抗变大。

=》一般来说,内层为基板铜厚,厂内1OZ=1.2 mil~1.4mil,外层为基板铜箔厚度+镀铜厚度

差动阻抗相邻线路与线路之间的间距,与阻抗值成正比 [Spacing愈小 , Z0值愈低],这个很好理解,间距变小,表示耦合越好,从而软水管对水流的阻力越小,特征阻抗变小。

线路层与线路层间介电层厚度,与阻抗值成反比。

防焊漆厚度,与阻抗值成反比[绿漆愈厚 , Z0值愈低],绿漆可以类比于堤坝对水流的保护作用,绿漆越厚,堤坝越厚,表示对水流的保护作用越好,水流都不会丢失,从而水流越大,对水流的阻碍越小,特征阻抗越低。

2.2 Microstrip单端阻抗模型

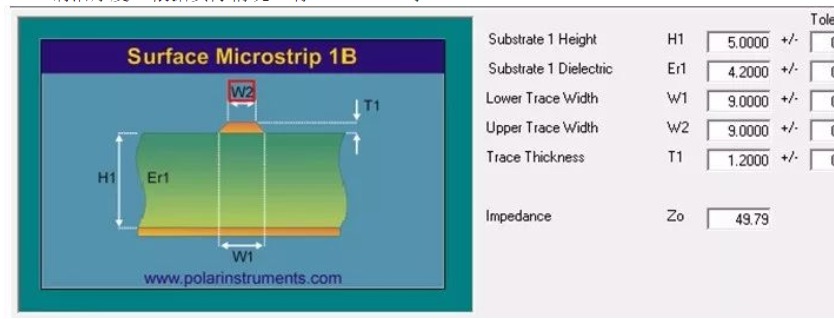

下图是表示微带线(Microstrip)的单端阻抗计算方法:

Surface Microstrip

2.3 Microstrip差分阻抗模型

下图表示微带线的差分阻抗计算方法:(带状线计算方法后面章节会介绍)

Edge-coupled Surface Microstrip

说明:

关于铜厚T :内层,1 oz=1.2mil~1.4mil左右,需要向PCB版厂确认,一般取为1.4mil。外层,厚度应该为基铜的厚度+镀层厚度

关于线宽:内层0.5oz上幅=下幅–0.5mil , 1oz / 经电镀上幅=下幅 – 0.8mil。外层,上幅=下幅 *(85-90%)

防焊层厚度:一般最小是0.4mil。单端阻抗:防焊前后约差7 ohms, 标示下限 +4mil 上限 +2mil。对于差动阻抗:防焊前后约差14 ohms, 标示下限 +10mil 上限 +4mil。

一般的PP型号与厚度是(仅供参考):型号---resin to glass ratio---厚度

对于Pre-Preg推荐使用2116,Core推荐使用7628,这是根据lql-008(个人编号)关于Stackup描述而来的,读者可参阅该篇文档关于PCB的细节。

2.4 Strip单端阻抗模型

这个模型可参阅图12。

2.5 Strip 差分阻抗模型

这个模型可参阅图13。

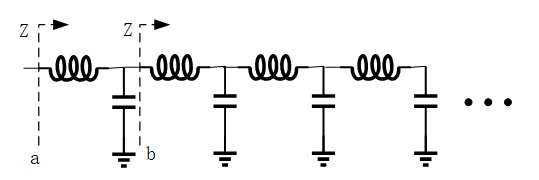

3.阻抗计算实例说明

传输线阻抗是从电报方程推导出来(具体可以查询微波理论),当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现象等等。在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来。

由图5可知,这是一个8层电路板的叠层结构,这就可以理解了,PP表示Prepreg。PP是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是PP类型介质,只不过他两面都覆有铜箔,而PP则没有。

那么每一层的铜箔厚度是怎么表示的呢?铜箔重量一般以Oz来表示。重量的单位1Oz(盎司)=28.3 g(克)。在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,它与Mil对应的关系是:

为了更好说明特征阻抗计算方法,在此假设板厚为1.6mm,也就是64mil 左右, 单端阻抗要求55Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

采用Polar Si8000计算Top与Bottom层微带线的单端阻抗为:

为了验证覆绿漆与不覆绿漆的区别,参照下图与图7的区别,可以看出,在这里不覆绿漆时特征阻抗比覆绿漆时增加了大约3.5Ohm。

这也验证了绿漆越厚,特征阻抗越小的说法(不覆盖可以表示为厚度为0)。

这里在举一个6层板的例子,更好的说明带状线特征阻抗计算的方法。在此假设板厚为1.5mm,也就是60mil 左右, 单端阻抗要求55Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线。

编辑:hfy

-

pcb

+关注

关注

4417文章

23967浏览量

426184 -

印制电路板

+关注

关注

14文章

978浏览量

43299 -

电路板

+关注

关注

140文章

5344浏览量

109027 -

emc

+关注

关注

177文章

4453浏览量

192273 -

数字电路设计

+关注

关注

0文章

28浏览量

12902

发布评论请先 登录

缩小阻抗差距,解决PCB传输线之SI反射问题

PCB特征与PDN性能的关系

PCB stack设计的特征阻抗

特征阻抗简介

pcb layout培训基础之传输线的特性阻抗

高速PCB中的阻抗匹配

PCB stack设计之特征阻抗

PCB stack设计之特征阻抗

评论