S3c2440是三星公司推出的一款基于ARM920T的处理器,采用ARM内核,不同于单片机,无片上rom与ram,必须搭配相应的外围电路进行使用,现在,让我们从零开始进行这一块MCU的学习,为了入门简单方便,前期我不会搭载任何操作系统,本手册写到哪算哪.

1.什么是nor flash启动和nand flash启动

在任何视屏教程里面,都会告诉你一个开关左右选择就能norflash启动或者nand flash启动,norflash启动能直接运行代码,nand flash启动不能直接运行代码,可是为什么呢?

要知道这一点,首先要明白nandflash和norflash的区别,首先,norflash是随机存储介质,也就是说,对norflash的操作时可以进行任意单字节的读写的,而nanaflash是块存储介质,对nandflash的读写只能以块的方式读写,也就是说,nand要修改一个字节,必须重写整个块

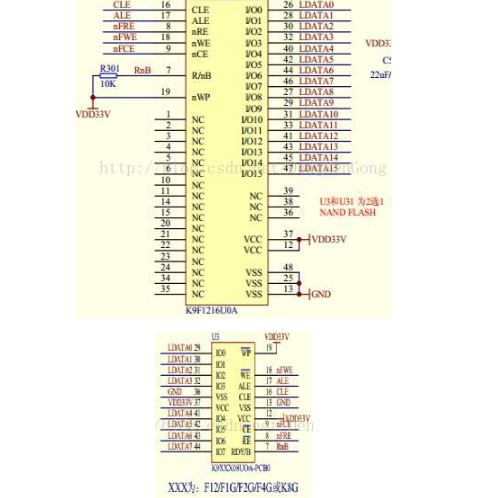

由此我们就可以知道,nand flash不可能作为代码直接执行的介质了,理论上,就算我们通过电路实现了nand flash执行代码也不可能,因为代码执行很重要的一点是可以随机的对任意一个字节的数据进行任意修改,而nand写一个字节要重写整个块,这速度太慢了,还有一个原因,因为某些工艺因素的影响,nandflash生产过程中就可能出现坏块,另外,nandflash在多次擦写中也可能出现坏块,所以这也决定了nand不可能实现直接运行代码,只能做存储器的功能,以下是nandflash电路(TQ2440)

可见,nand flash分为八位和16位,地址线和数据线复用,依靠控制总线来切换地址数据时序,主要的控制线有

CLE:命令锁存使能线,输入命令时使用

ALE:地址锁存使能,输入地址时使用

nFCE:芯片使能,读写芯片时,这一位必须有效

NFRE:连接NRE读使能,读数据之前,要先让nre有效

NFWE:写使能,写数据的时候这根线有效

RNB :就绪/忙标志,主要用于发送完编程/擦除命令后,检测操作是否完成

WP :写保护使能

说完nandflash说说norflash,首先norflash的地址线和数据线是分开的,其次,是可以单字节读取写入的,另外,可靠性好,不易出现坏块,使用时间更长,(norflash上带的是通用sdram接口)

电路图如下,

因为是16位数据,所以没有接data0的必要,初始地址是0x00000000,

OE:读使能

WE写使能

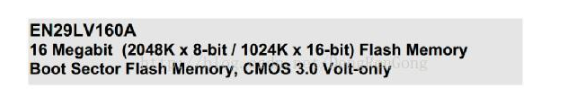

片选接了GCS0,那么norflash寻址范围是多少呢?首先,选用的芯片是EN29系列,

该系列芯片说明书中说明

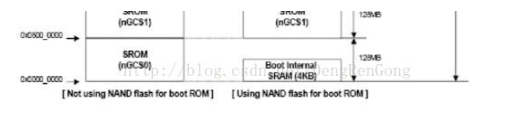

可见,NORFLASH是16M的,但是寻址范围是不是16M我们还需要确认NGCS0的选通时间,查看memory说明,有这样一段

也就是说2440的NGCS0分区大小为128M,驱动16M足足够了,所以,我们可以说,norflash启动,16M完全可用

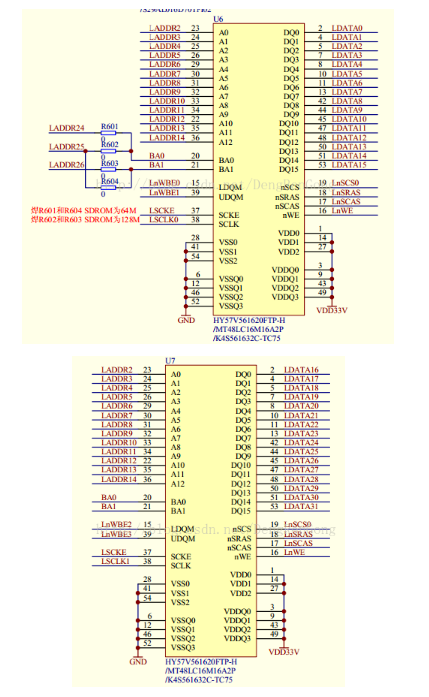

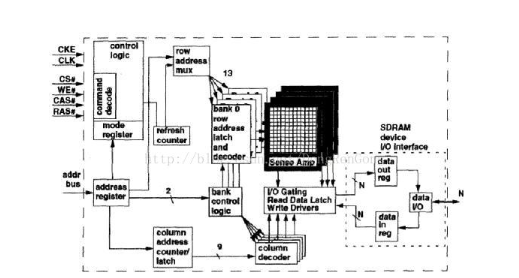

接下来说一下SDRAM,电路图如下

这是两块相同的芯片,两块16位芯片合起来将数据总线扩展到32位

可以看到,地址线和数据线是分离的,控制接口主要由以下几根线组成

CKE:INPUT控制norflash内部时钟的使能与禁止,从而进入三种状态,掉电,挂起,自刷新(为了保持内部数据,设备自身也需要一个时钟来进行数据自刷新,和外部读写时钟并不是一个概念)

CLK:INPUT外部读写时钟,用于外部读写同步

其他的控制总线想要明白必须要先明白SRAM的架构,虽然不用去设计,但是明白SDRAM架构看不懂这个电路图,来,我们说说

以下是标准4bank的SDRAM内部结构

其写入原理如下

要存取数据时,先选中一行( wordline加高电位),于是这一行上挂着的所有的行选通NMOS都导通,电容中的数据就沿着bitline进入感应放大器,经其放大后到达列选通NMOS处。接下来,当某根CSL置高后,相应的列选通NMOS就导通,数据沿着bifline继续向IO接口传,或者外面的数据立即写入存储阵列。当然,具体实现肯定更复杂,但是基本原理就是这样

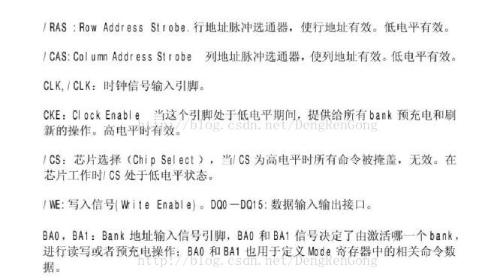

那么,这些控制线什么作用呢

LDQM UDQM:数据屏蔽,当LDQM为高,数据线上低8位被屏蔽UDQM高八位被屏蔽,这样就可以进行bank选择了(不管内存怎么设计,最终还是八位一个字节,所以需要屏蔽)

接下来我们看看SDRAM寻址,通过电路可以看到,WBE0 1 2 3分别四根线控制,也就是说,同一个地址,选择不同的WEB,可以依次读出0-7 8-15 16-23 24-31四个八位数据,CPU内部自动将这四个数据组合起来,形成一个32位数据,所以,实际上,依次读写操作获得或者写入数据单纯数据上就要四步,另外,地址写入也分两步,之前说了,SDRAM寻址分为行和列,所以写入地址分为写入行地址,写入列地址,简化来看,一共就是6步(没有说各种控制总线过程,大家有兴趣可以研究)

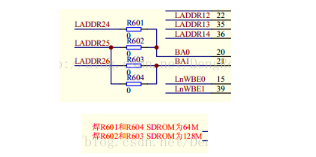

连接的ba0 ba1

首先四字节对其寻址(32位数据线),那么DAT0 DAT1的寻址线肯定是0,所以没有接上的必要,24 25 26决定最高位,如果为64M r601 r604接上,地址线24-25连接,CPU设置0x30000000为基地址的话,最高地址是0x33FFFFFF,(0x30000000-0x33ffffff) = 0x3ffffff个字节,一共就是64M字节

注意,这中间涉及到一个比较复杂的解码过程,就是将物理地址解码成总线地址,(两个数据),并不是说25 26连接了地址空间就绝对是0X36FFFFFF了,具体过程,请查阅相关资料

-

处理器

+关注

关注

68文章

20325浏览量

254693 -

mcu

+关注

关注

147文章

19110浏览量

403233 -

SDRAM

+关注

关注

7文章

458浏览量

57827 -

存储器

+关注

关注

39文章

7753浏览量

172158 -

nandflash

+关注

关注

0文章

48浏览量

21094

发布评论请先 登录

NOR FLASH和NAND FLASH的对比

从NOR Flash 到 NAND Flash 和SD NAND,从底层结构到应用差异

Atmel SAM3S系列32位Flash微控制器深度剖析

SD NAND 为何不能存启动代码,SPI NAND 与 NOR Flash 却可以 —— 接口、传输、启动机制全对比

SPI NOR Flash和SPI NAND Flash存储芯片的区别

Infineon SEMPER NOR Flash与HYPERRAM™ 2.0 Gen2 Flash+RAM MCP产品解析

从NOR Flash到NAND Flash和SD NAND,从底层结构到应用差异

SPI NOR FLASH是什么,与SPI NAND Flash的区别

Nor flash芯片低温无法启动

兆易创新推出GD5F1GM9系列高速QSPI NAND Flash

S3c2440处理器中nor flash启动和nand flash启动问题

S3c2440处理器中nor flash启动和nand flash启动问题

评论