开始讲解第一章了!

有哪些内容呢?

肯定先从原理讲起了!

环路意味着有反馈!

什么是反馈?

那么有没有前馈呢?

后续会详细讲解!

要求看似简单,

其实比较难!

很多知识点可能是大家第一次见到!

数学模型必须能够看懂!

不然后续高阶的环路无从分析!

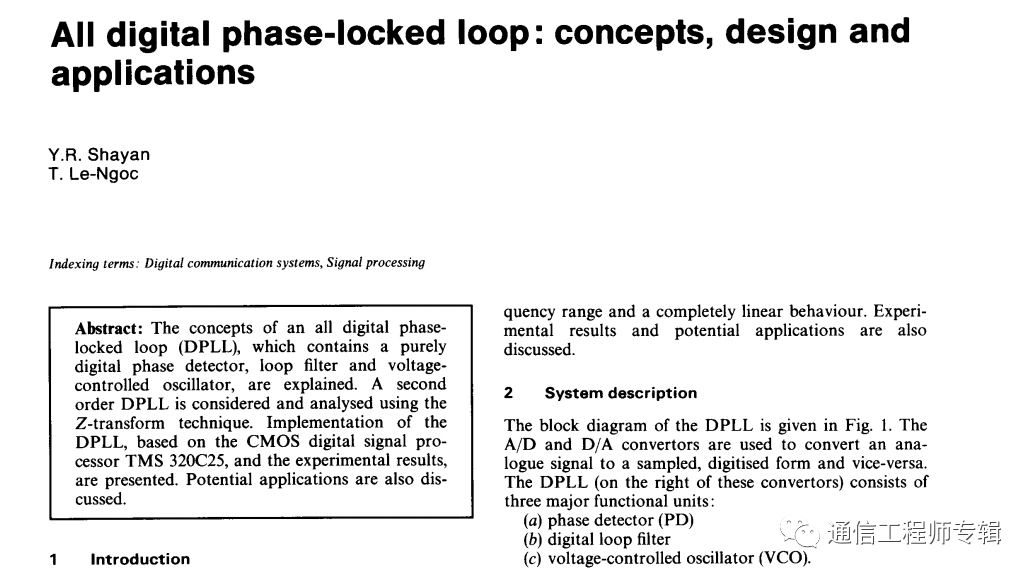

互联网时代,看看网上关于这方面的内容吧!比如在IEEE上下载的文章!强烈建议大家去IEEE下载论文,需要仔细阅读!论文的质量是很高的,当然也有灌水的文章,比例非常低。

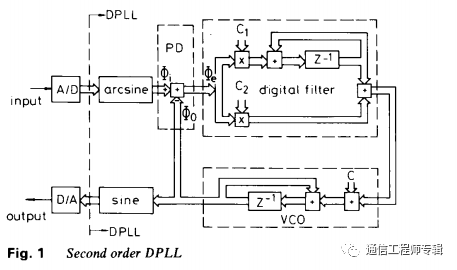

当年还被认为是新概念的DPLL现在已经是老掉牙的技术了,不过想要搞懂它依旧需要花功夫!模拟环路如何转化为数字环路,如何在MATLAB中仿真,如何在FPGA中实现都是需要逐步完成的!

直接给出二阶环路的架构。

难道还要三阶和更高阶的概念?

这些概念有点难了,

先从基本的概念开始学习吧!

比如先搞懂一阶环路!

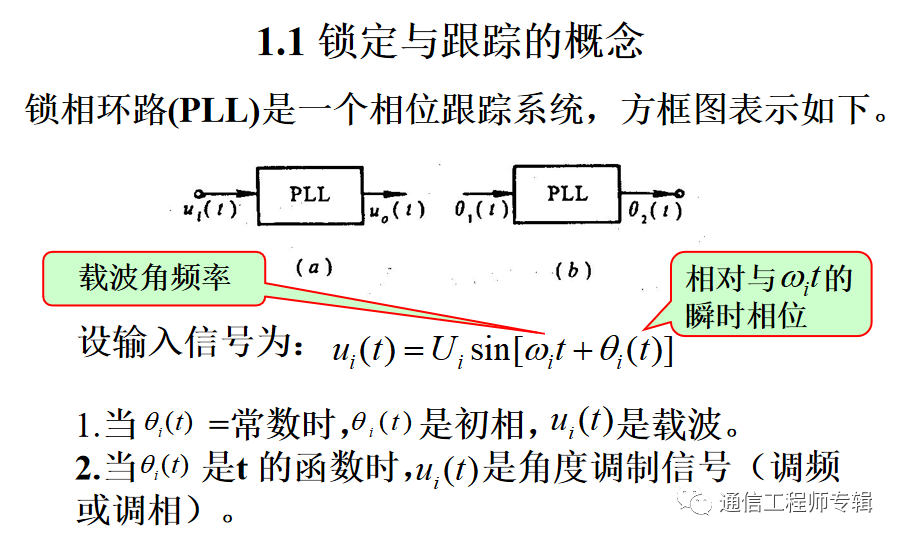

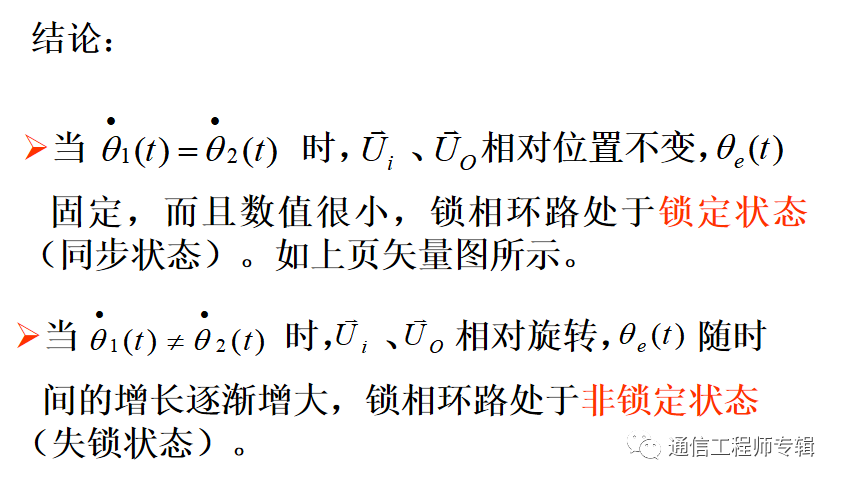

先来学习锁定和跟踪!

有没有疑问?既然已经有这个信号了,为什么还要本地复现这个信号呢?不是多此一举吗?这是本人当年学习的真实想法。大家有这个疑问吗?

锁相环的核心是锁这个字!!!

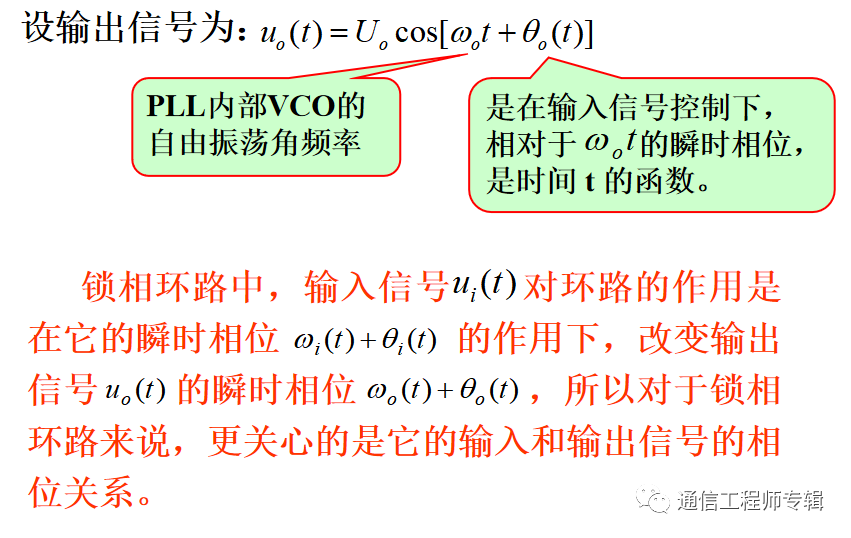

这些都是模拟信号的表达方式。后面一定会改写为数字信号的表达方式。不然怎么仿真呢?再次提醒大家,在这门很难的课程里,请大家务必做好迎接很多困难的准备!方法总比困难多!锁相和锁频有差别吗?

请思考:

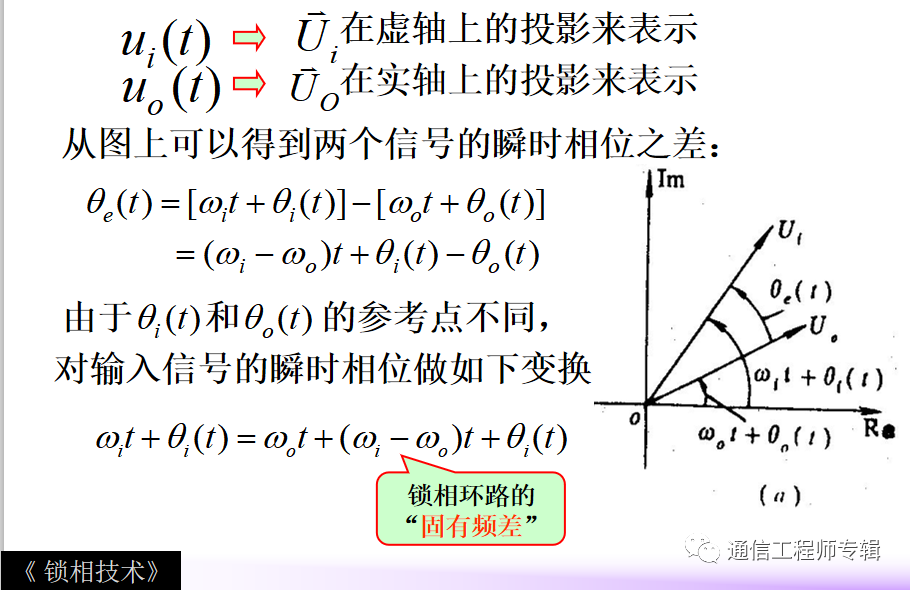

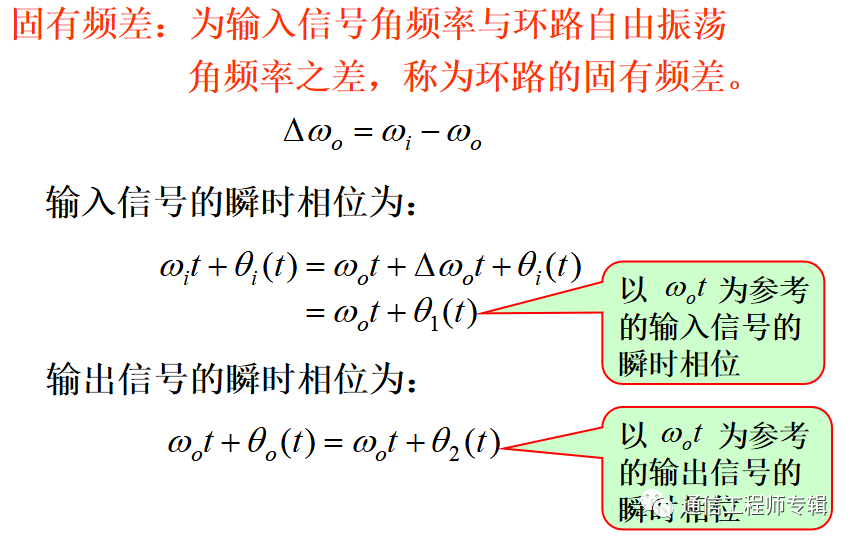

输入信号和输出信号的相位关系!

想在通信领域深造的学生肯定会接触到锁相环,因为这是经典知识!我们没有理由松懈!

还是那句老话!

仿真必不可少!

比如仿真锁频环和锁相环!

有了仿真过程可以让大家对环路有着更深的了解!

后续会给出相关的仿真来促进大家“消化”!

提示一下:调相可以完成调频!

反过来则不可能!

后续会讲哪些呢?

先把之前的内容做个总结。

原文标题:锁相技术 第一章 锁相环路的基本工作原理(1)

文章出处:【微信公众号:算法工匠】欢迎添加关注!文章转载请注明出处。

-

电路

+关注

关注

173文章

6063浏览量

177476 -

锁相环

+关注

关注

36文章

633浏览量

90816

原文标题:锁相技术 第一章 锁相环路的基本工作原理(1)

文章出处:【微信号:gh_30373fc74387,微信公众号:通信工程师专辑】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

CDCVF2510A 3.3V锁相环时钟驱动器技术文档总结

基于锁相环的无轴承同步磁阻电机无速度传感器检测技术

【RK3568+PG2L50H开发板实验例程】FPGA部分 | Pango 的时钟资源——锁相环

高压放大器在锁相环稳定重复频率研究中的应用

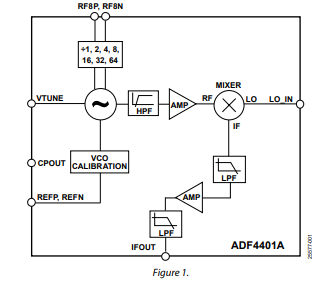

ADF4401A转换环路、PLL、VCO模块技术手册

锁相环是什么意思

AN-1420:利用数字锁相环(DPLL)实现相位增建和无中断切换

可编程晶振的锁相环原理

可编程晶振的关键技术——锁相环原理讲解

TMS320C6000 DSP软件可编程锁相环控制器指南

MS72300——无杂散、2.1GHz、双环路小数 N 分频频率综合器

锁相环路电路的作用

锁相环路电路的作用

评论