在本文中,我们将讲解如何在 Vivado Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台。 您既可以采用已确认的成熟设计作为平台,这样只需稍作增强便可灵活运用于加速软件功能,或者也可以采用仅含加速所需拓扑结构的简单基础平台。重点在于,此平台并没有必要采用一次性设计,而应采用可有机变化的设计,这样即可随您的设计需求而变。

01 引言

加速软件组件就意味着将其从 CPU 卸载至可编程逻辑中的加速 IP。Vitis 工具将负责处理在加速 IP 与 CPU 之间添加数据移动程序的操作。 但它确实需要用户提供输入信息。它需要了解从 SoC 和加速 IP 连接到哪个接口。它还需要了解有哪些时钟/复位可供使用。

并且由于我们在 CPU 与加速 IP 之间发送数据块,因此需要中断信号。基本上就这些……好吧,其实还要向 Vitis 工具提供一些其它信息,这个我们稍后再聊。

先继续往下看。启动 Vivado 并创建工程。我使用的是 ZCU104 评估板。但以下步骤对于所有 Zynq UltraScale 开发板都是通用的,无论是开发板还是定制板都一样。

02 创建硬件设计

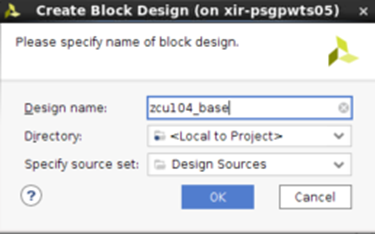

创建块设计 (BD)。此处名称与用于命名平台的名称相同。

从 IP 目录添加 Zynq UltraScale 处理器子系统 IP 块。如果使用的是开发板,那么应启用“块自动化设置 (Block Automation)”功能。

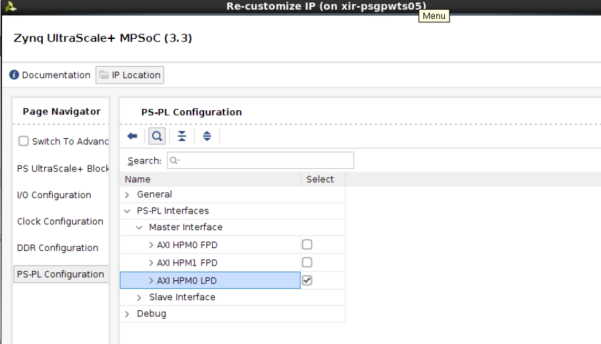

我把默认接口更改为仅包含 LPD:

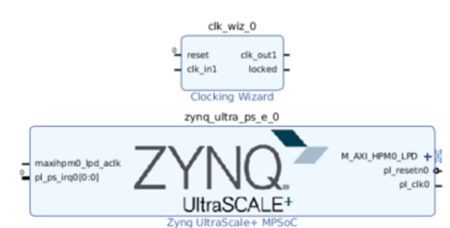

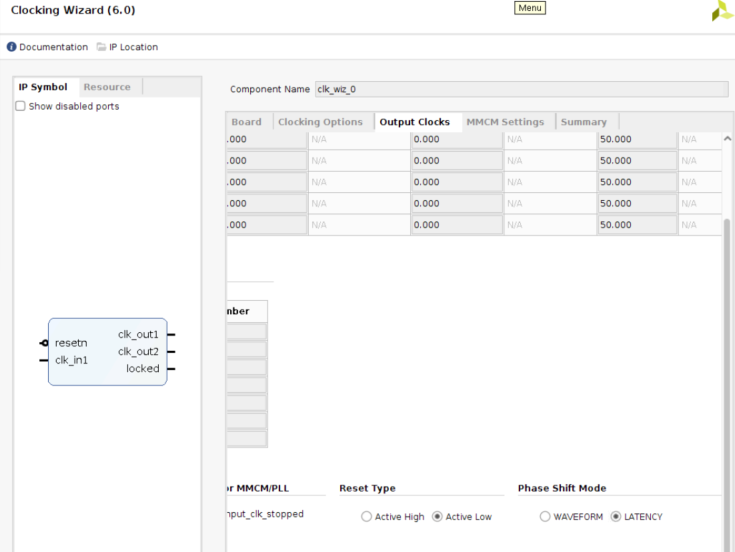

在我们的简单平台中,可以只创建 2 个时钟。这些时钟将在 Vitis 中使用。 我们可从 IP 目录添加 Clocking Wizard:

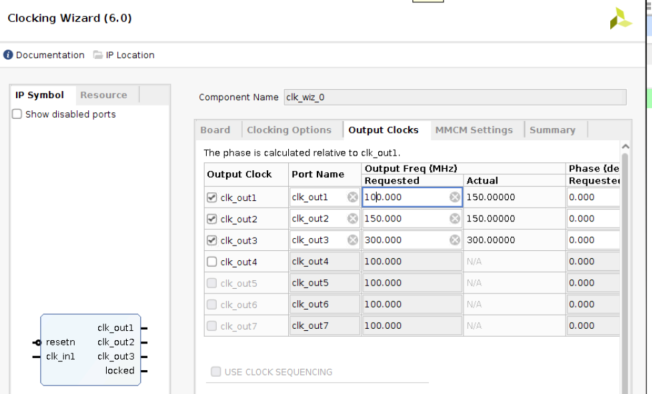

默认情况下,复位处于高电平有效状态,而复位源(位于 Zynq UltraScale 器件上)则处于低电平有效状态。因此,在进行时钟设置配置时需牢记此信息。 我添加了 3 个输出时钟:100Mhz、150Mhz 和 300Mhz:

并将复位极性设置为低电平有效(Active Low):

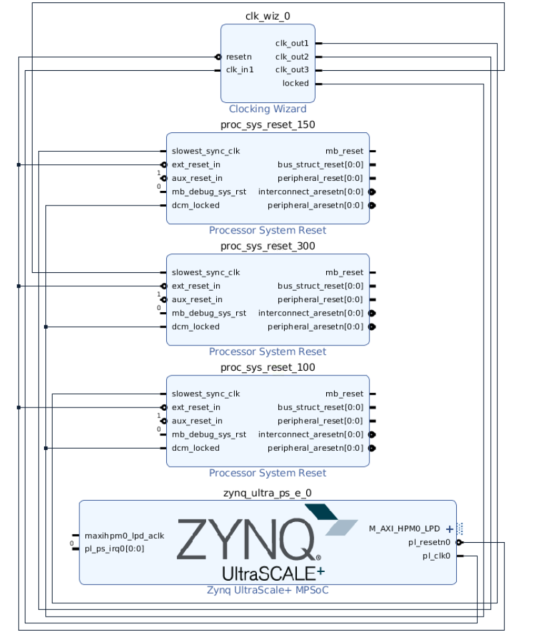

针对每个时钟都需要提供同步复位。我们有 3 个时钟,因此需要从 IP 目录添加 3 个 Processor System Reset IP 核:

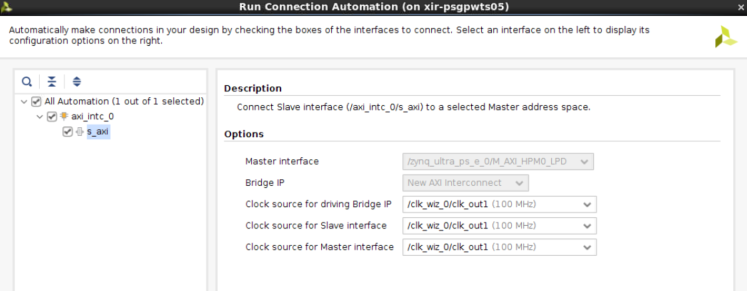

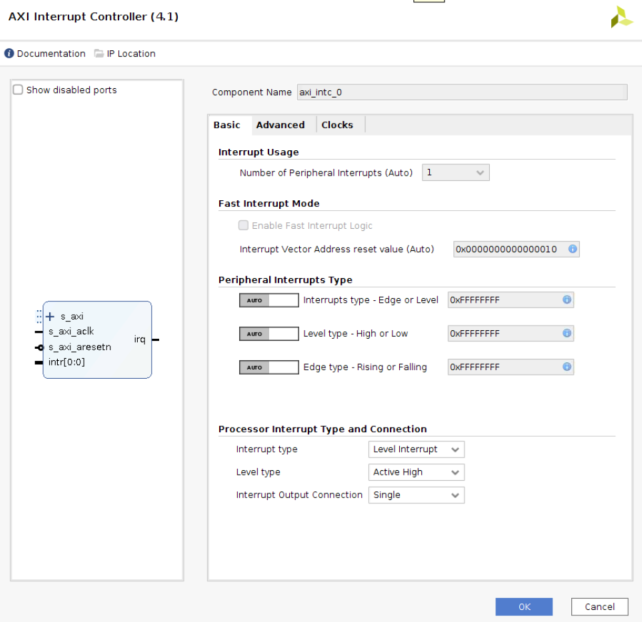

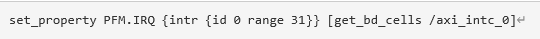

下一步,需要添加中断信号。这里我们从 IP 目录添加 AXI Interrupt Controller。用户可以使用 IP integrator 中的“运行自动连接(Run Connection Automation)”功能来处理 AXI 连接。

使用 100Mhz 时钟

在 AXI Interrupt Controller 中,将“中断输出连接(Interrupt Output Connection)”设置为“单连接 (Single)”,并将其连接到 Zynq UltraScale IP 上的 pl_ps_irq:

对于基本硬件平台,这样设置就可以了。 现在,我们只需设置元数据,以便通过 Platform (PFM) 属性将硬件信息告知 Vitis 即可。

03 添加 PFM 属性

PFM 属性是将元数据传递给 Vitis 所必需的。 Vitis 会提取这些数据以判定哪些接口、时钟和中断信号可用于在现有平台中添加加速部分。

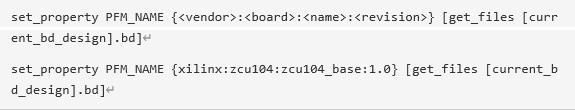

平台名称

首先,对平台命名:

完成命名后,您将看到一个新的“平台 (Platform)”选项卡。其中将显示整个设计中的所有时钟、接口和中断信号。 我们需要筛选可用于 Vitis 的资源。

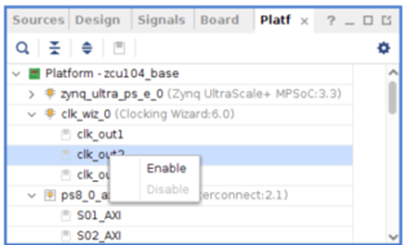

启用时钟

右键单击时钟,然后单击“启用 (Enable)”:

针对 clk_out3 重复此操作。

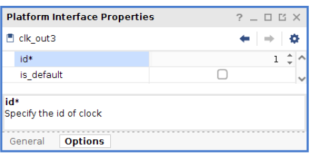

时钟属性

选中“选项 (Options)”选项卡:

注:时钟 ID 必须以 0 开头并递增,因此,请更改此处设置。我们还必须指定默认值。 此处默认值即 Vitis 中使用的默认时钟:

设置 clk_out3 的索引:

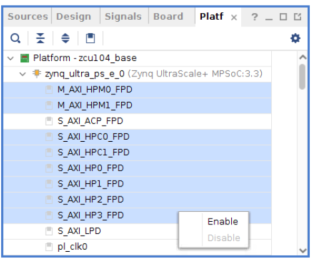

启用接口

可采用块设计中可用的任意接口,例如,Zynq UltraScale 器件上的接口或 AXI Interconnect 上的接口。 在此例中,我只添加 Zynq UltraScale 器件上的接口。

启用中断

04 工程属性

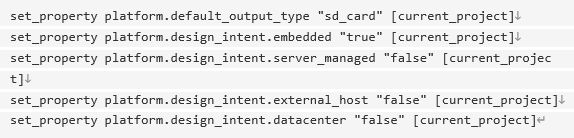

Vitis IDE 是支持众多不同流程(例如,数据中心、加速或嵌入式流程等)的统一工具。我们需要将此用途传递给 Vitis 工具。 如果要创建嵌入式设计,就需要指定该用途。在此示例中,我们将把 Vitis 用于加速。此用途必须明确指定,因为 Vitis 需要告知下游工具如何处理该平台。 此处可看到下列属性:

05 创建 XSA

完成以下任务以创建 XSA

•生成块设计 •创建 HDL 封装 •生成比特流 •依次单击“File -> Export -> Export Hardware” o 依次单击“Expandable -> Pre Synthesis”,然后选中“Bitstream”

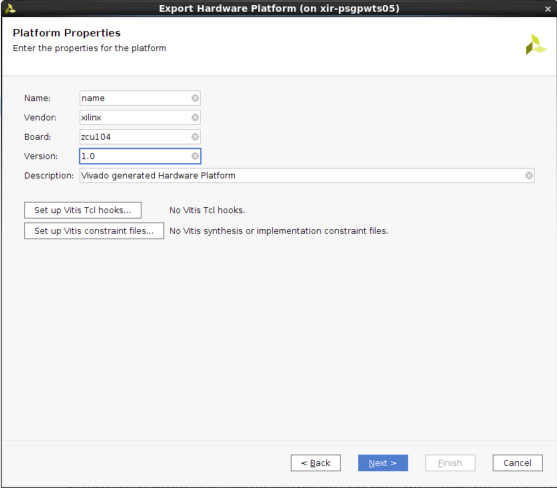

用户可在此处输入详细信息:

至此大功告成。

-

cpu

+关注

关注

68文章

11216浏览量

222952 -

可编程逻辑

+关注

关注

7文章

526浏览量

45307 -

Vivado

+关注

关注

19文章

846浏览量

70475

原文标题:如何在 Vivado 中为加速平台创建硬件工程

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序

元服务发布准备工作

亚马逊云科技推出Amazon Quick Suite,引领Agentic AI驱动的工作新范式

土压力计在使用前需要进行哪些准备工作?

Vivado无法选中开发板的常见原因及解决方法

想做好PCBA贴片加工?这些前期准备工作要做好!

AMD Vivado Design Suite 2025.1现已推出

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

Vivado 2018.3软件的使用教程

AMD Versal自适应SoC器件Advanced Flow概览(下)

Vivado Design Suite用户指南: 设计分析与收敛技巧

Vivado Design Suite用户指南:逻辑仿真

如何在Vivado Design Suite中完成平台准备工作

如何在Vivado Design Suite中完成平台准备工作

评论