很多小伙伴都知道在挑选内存的时候不光要看频率,还要看时序,或者叫延迟。也就是经常标注在内存表面,在测试软件中也能看到的那些中间的带短线连接的两位数。不过要问它们到底具体代表什么意思,相信很多小伙伴就只能摇头了。那咱们今天就来说一说它们的具体含义吧。

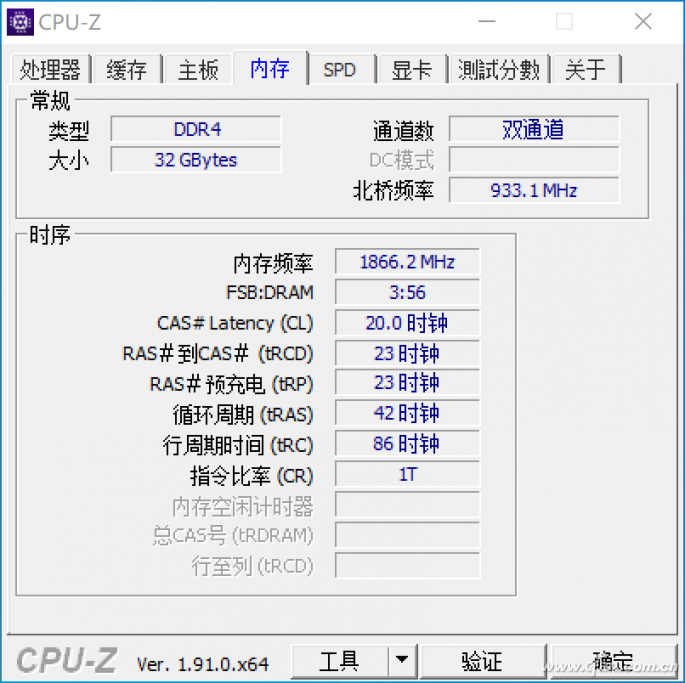

时序的意义非常简单,因为访问内存数据需要几个动作,这些数字就表示各个动作的延迟,或者说反应时间。其数字表示的是经过几个时钟周期,比如3000MHz的内存,一个22的延迟就表示需要22/3000M秒(7.3纳秒)。也许3600MHz的同一个动作延迟是24,那么它就需要24/3600M秒(6.6纳秒),后者看起来“延迟”大,但实际上比前者的动作还快一些。

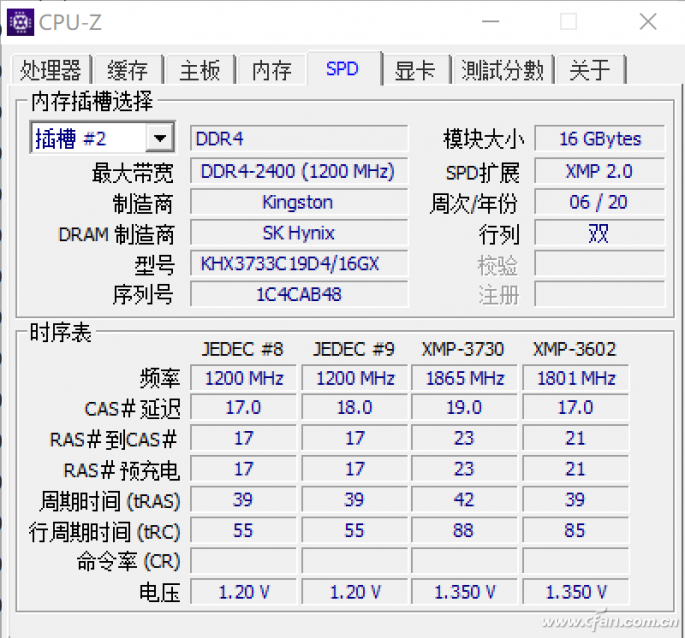

那么,这些时序具体是什么动作呢?我们最常见的时序主要是“CL-tRCD-tRP-tRAS”,它们的含义依次为:

CL(CAS Latency):列地址访问的延迟时间,是时序中最重要的参数;

tRCD(RAS to CAS Delay):内存行地址传输到列地址的延迟时间;

tRP(RAS Precharge Time):内存行地址选通脉冲预充电时间;

tRAS(RAS Active Time):行地址激活的时间。

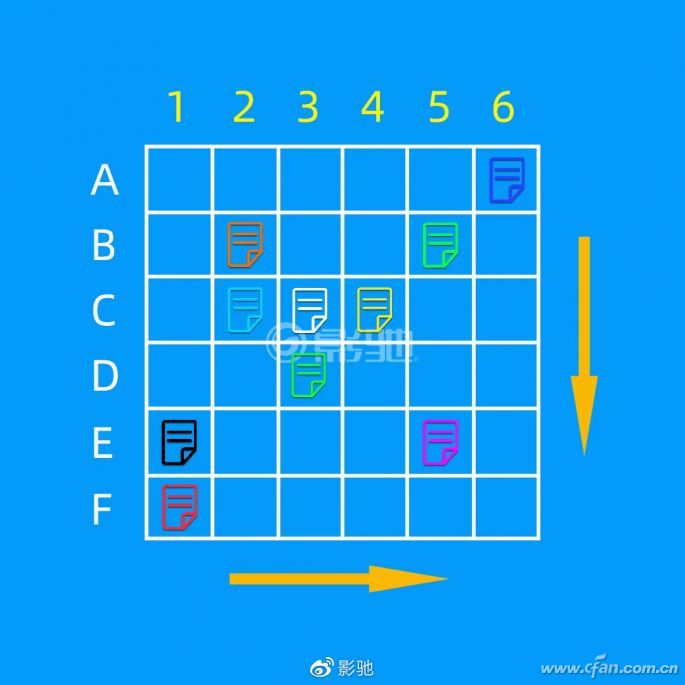

这里要注意内存的“行”与“列”的概念,它就是一种定位方式,用来帮助确定内存中的模块,对其中的数据进行读写。我们可以把内存想象成一个网格,每个方格内都存储着不同的数据。CPU需要什么数据,就向内存发来指令,比如想要C4位置的数据。

接下来内存就要先确定数据具体在哪一行,所以时序的第二个参数tRCD就是代表这个时间,意思就是内存控制器接收到行的指令后,需要等待多长时间才能访问这一行。仅靠行指令内存并不能哪一个数据才是CPU需要找的,所以tRCD的值是一个估值,而且是最大值,也就是找到“最里面”的数据需要多久。因此小幅改动这个值并不会影响内存的性能表现。

内存确定了行之后,要想找出数据,还得确定列。那么时序的第一个数字,也就是CL(CAS),表示内存确定了行数之后,还得等待多长时间才能访问具体列数的时间(时间周期)。确定了行数和列数之后,就能准确找到目标数据,所以CL是一个准确的值,所以它在时序当中是最关键的一个参数,任何改动都会影响内存性能的发挥。

内存时序的第三个参数tRP,就是如果我们找到这个数据后,根据CPU指令去寻找下一个数据,再确定另外一行所需要等待的时间。

第四个参数tRAS则可以简单理解成是内存写入或者读取数据的总时间,所以一般接近于前两个参数,既CL和tRCD的和。

所以在保障稳定性的前提下,同频率内存时序越低越好。那么,时序对内存性能影响有多大呢?我们来看看内存厂商自家的测试吧。

可以看到,内存时序的降低确实可以提升内存速度,不过主要变化还是在响应时间方面,而不是大家更关注的带宽。要注意的是,厂商拥有更好的样品和平台,测试的时序修改是比较“猛烈”的,小伙伴们只能在消费级主板上超频,实际上做到的修改幅度大约只相当于其中某两个相邻例子,很难重现从例1到例3这样的大幅修改,更不要说从例1到例4了,大家实际操作的时候千万不要贪多。

-

内存

+关注

关注

9文章

3238浏览量

76524 -

频率

+关注

关注

4文章

1588浏览量

62368 -

内存时序

+关注

关注

0文章

4浏览量

3086

发布评论请先 登录

keil中c语言的动态分配内存

【「Linux 设备驱动开发(第 2 版)」阅读体验】+读深入理解Linux内核内存分配

rk基于linux/android内存管理

Credo发布业界首款内存扇出Gearbox

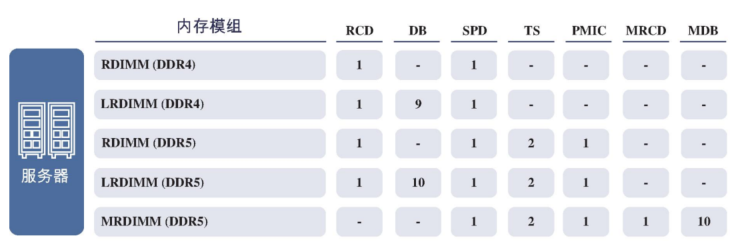

行业资讯 I 火爆的“内存接口芯片”

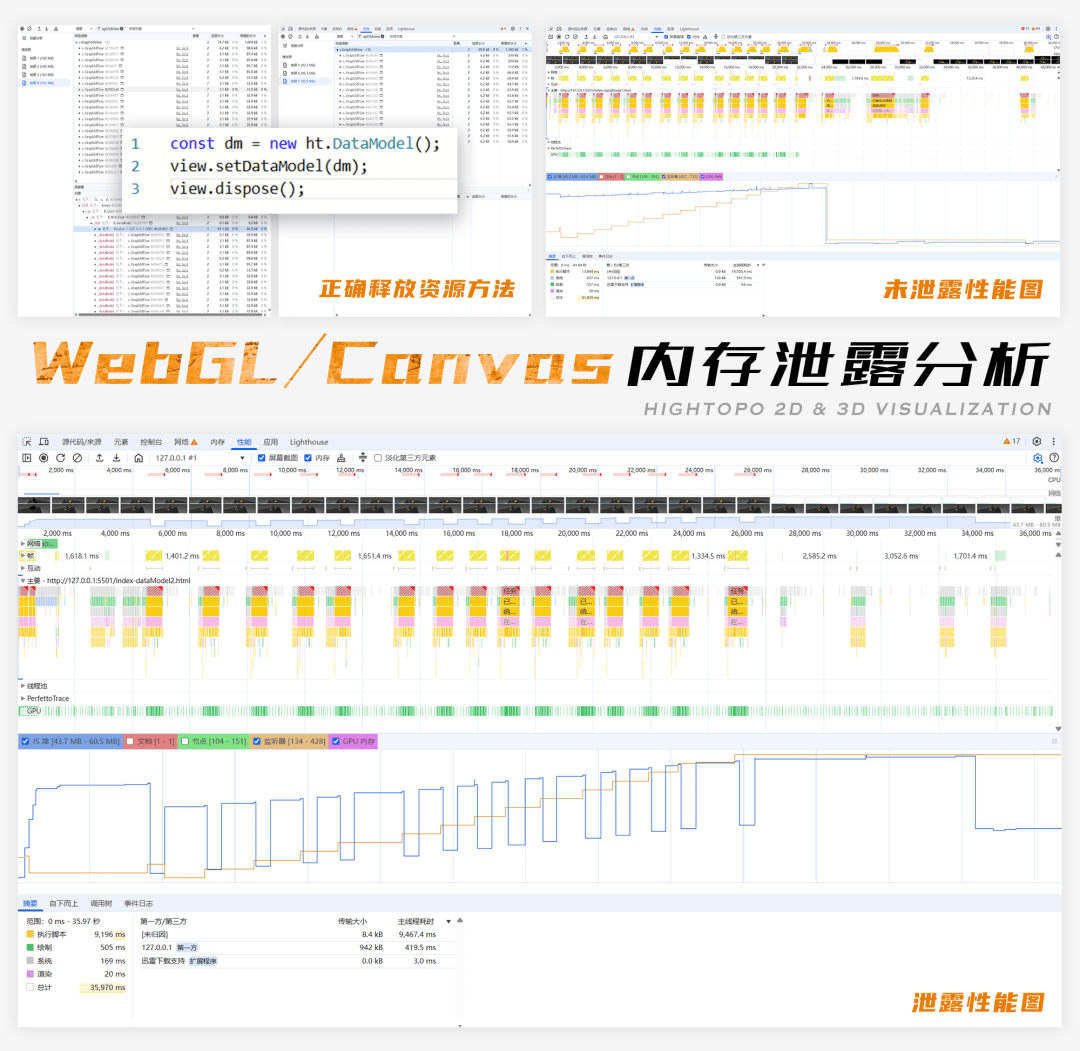

WebGL/Canvas 内存泄露分析

科普:什么AI 内存技术

灵活高效ZBUFF — C内存数据操作库:优化内存管理的利器

内存中隐藏的内存时序的意义分析

内存中隐藏的内存时序的意义分析

评论