线电阻的电压降的影响——地电平(0电平)直流引起的低电平提高

图中虚线为提高的情况。提高幅度与IC的功耗大小、IC密度、馈电方式、地线电阻(R) 、馈电的地线总电流有关。 ΔV地= ΔI× ΔR

信号线电阻的电压降的影响

a) IC输出管脚经过印制导线或电缆到另一IC的输入脚,输出低电平电流在印制导线或电缆电阻上引起一个低电平的抬高,其值为ΔVOL=IOL×R 。 见图中的上面一条虚线。

显而易见,低电平的抬高与印制导线电阻值及输出低电平电流有关,如下图所示:

B点的低电平比A点的低电平高

注意:当IC输出脚为低电平时,如果此器件不是驱动器, 而是一般器件,则由于输出低电平电流太大, 远大于器件手册给出的值,输出三极管将退出饱和区,进入工作区,

使输出低电平抬高很多。如下图中上面一条虚线所示:

决定因素:

端接方式

端接电阻大小

输出管饱和深度

输出管β值

b) IC输出管脚经过印制导线或电缆到另一个IC的输入脚,输出高电平电流在印制导线或电缆电阻上引起一个高电平的降低,其值为ΔVOH=IOH× R,见下图中高电平上的下面虚线:

IOH由下列因素决定:端接方式、端接电平、端接电阻大小

R由下列因素决定:线宽、线厚、线长

显而易见,高电平的降低与印制导线或电缆电阻值及输出高电平电流有关,如下图所示:

B点的高电平比A点的高电平要低

注意: IC输出脚为高电平时, 如果此器件不是驱动器,而是一般器件, 则由于输出高电平电流太大,远大于器件手册给出的值时,输出管也会退出饱和区,进入工作区,使输出高电平降低很多。如下图中下面一条虚线所示:

电源线电阻的电压降的影响

IC的电源电压(如+3.3V),如果系统中存在差值,当小于+3.3V时, 输出高电平将产生一个下降值, 如上图中高电平上的虚线所示:

由于系统电源有集中电源和分散的电源模块之分,此差值不同,由于IC功耗的大小、IC密度、馈电方式、电源线的馈电电阻值以及电源电流值,引起一个 ΔVCC (ΔVCC =ΔI×ΔR)

以上原因,使TTL信号波形变得离理想波形很远了。 低电平大为提高了,高电平也大为降低了。 对这些值若不严加控制, 对系统工作的稳定可靠工作是不利的。此外,结温差,即不同功耗的器件的P-N结的温度不同,还会影响高低电平及门槛电平的变化也会影响系统工作。

除上面所说的直流成分之外,更为重要的是系统是以极高频率在工作,也就是说, 系统内的器件、导线有各种频率的, 各种转换速率的信号在动作、传递。 首先是相互之间的信号电磁藕合 (串扰) 和信号在不同特性阻抗传输路径上的反射, 以及电源, 地电平由于IC高频转换引起电流尖峰电平,使TTL信号波形变得更坏。

转换噪声

由于系统工作时, 器件以高频转换, 造成供电系统上有高频率变化的电流尖峰,而供电的电源线路和地线路都可看成是很小的电阻、电感、电容元件。电流尖峰值太大, 在它们上面会产生较大的交流尖峰电压,其电源上的尖峰电压基本上会串扰到高电平上,而地电平上的尖峰电压会串扰到低电平上,如下图所示:IC内部同样存在这种尖峰电压。

串扰噪声

由于系统组装越来越密, 印制导线之间的距离越来越近,邻近导线上有高速转换的电平信号。 如正跳变信号跳变的时间tr和负跳变的时间tf都很小,使得导线上已有信号上叠加一个较大的电磁藕合信号(串扰信号)。如下图中较大的尖峰信号。这些信号还包括插头座上的信号针之间的串扰信号以及电缆中信号之间的串扰。

决定因素:tr与tf值、线宽、线间距、(基材)介质的厚度、介质的介电常数、平行线长、重叠线长、插头座信号针地针比、电缆信号线地线比。

反射噪声

如果IC之间的互连线比较长 (复杂系统往往是这样) ,线的特性阻抗又不均匀,或者终端没有匹配,会引起反射,如果始端也不匹配, 则会来回 反射而造成振铃。 如下图所示:

决定因素:特性阻抗、匹配方式、失配大小

终端反射系数、始端反射系数、线长

边沿畸变

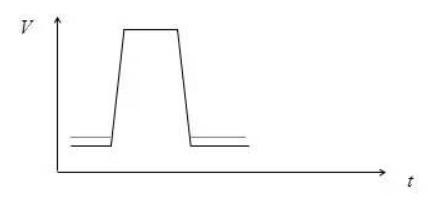

如果信号频率升高到一定程度,也就是器件工作频率达到一定的高度极限,而且印制导线又较长或者负载电容较大时, tr ≥tw上升时间等于或大于脉冲宽度,信号畸变到没有高低电平平顶或者远离平顶。如下图所示(实线):

决定因素:线宽、线长、基材介质厚度、介质介电常数、负载数、工作频率(脉宽)、tr数字信号的变化。讨论了上面七条,可见其畸变不容忽视。如果任其自流,不严加限制,造出来的系统不可能稳定、可靠的工作。

lw

-

示波器

+关注

关注

113文章

6982浏览量

194778 -

IC

+关注

关注

36文章

6270浏览量

184371 -

信号完整性

+关注

关注

68文章

1473浏览量

97780

发布评论请先 登录

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

受控阻抗布线技术确保信号完整性

信号完整性测试基础知识

电源完整性分析及其应用

iic协议的信号完整性测试

信号完整性不好的原因

差分信号对信号完整性的影响

听懂什么是信号完整性

详解影响信号完整性不好的原因

详解影响信号完整性不好的原因

评论