ARM架构处理器虽然进军PC桌面市场不太顺利,但是在云端、边缘计算、高性能计算领域,确实硕果累累,产品丰富,应用广泛,已经对x86构成了不小的威胁。

最近,亚马逊发布了64核心的Graviton2,Ampere推出了80核心的Altra,Mavell(美满电子)现在又带来了新一代ThunderX3。

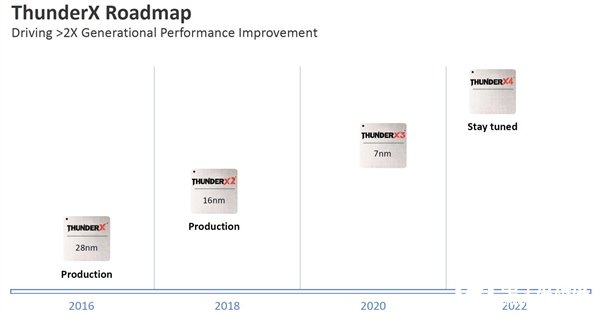

Marvell ThunderX系列已经走过两代产品,并承诺每两年升级一次。2018年的ThunderX2采用台积电16nm工艺制造,最多32个核心,基于自研的四发射、乱序执行ARM v8.1架构,每核心最多四线程,也就是总共最多128线程,运行频率2.5GHz。

今年晚些时候,Marvell将会发布第三代ThunderX3,2024年则会有第四代ThunderX4。

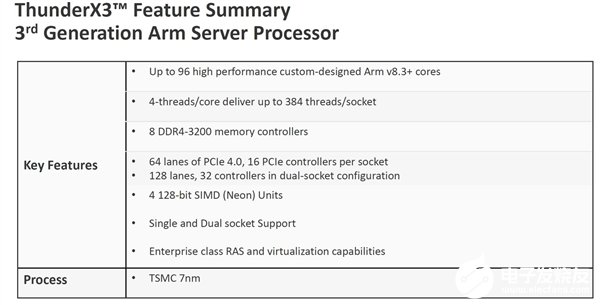

ThunderX3采用台积电7nm工艺制造,升级为ARM v8.3指令集架构,最多96个核心,比上代增加了两倍,相比AMD霄龙也多了一半,同时继续支持四线程,总计最多128线程。

核心频率没说,但是热设计功耗范围100-240W。

新的内核集成四个128-bit Neon SIMD单元,就宽度而言等效于一个x86 AVX-512,当然最高端的Intel至强有两个,AMD霄龙则每核心支持两个256-bit SIMD单元。

I/O方面支持八通道DDR4-3200,类似AMD二代霄龙和Intel下代至强,并有64条PCIe 4.0,AMD二代霄龙的一半。

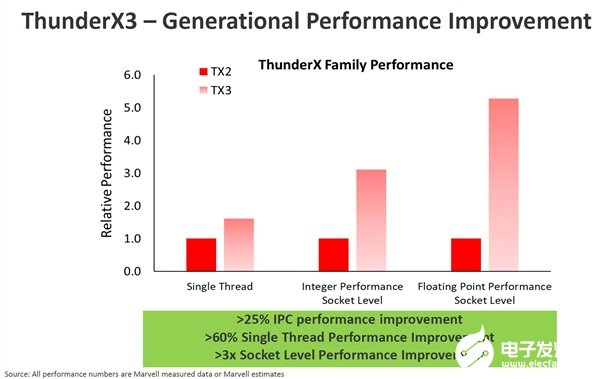

Marvell官方宣称,ThunderX3 IPC性能比上代提升超过25%,单线程性能提升超过60%(那意味着频率也会大大提高),平台级整体性能提升最多3倍,浮点性能更是得益于新增的SIMD单元而可以增加5倍多。

Marvell ThunderX家族的生态支持已经相当繁茂,官方号称部署最广泛的ARM服务器处理器,已得到了20家客户的采纳,甚至第一次进入了超级计算机。

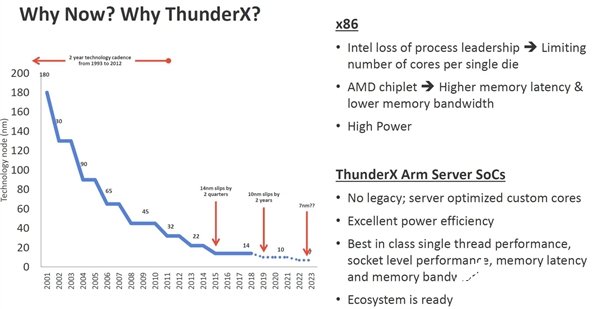

面对x86,Marvell信心十足,尤其是强调Intel受制于工艺无法增加更多核心,已丢失领导地位,AMD则存在内存延迟偏高、带宽不足的问题,自家的ThunderX系列则优点多多:服务器优化定制核心、出色的能效、最佳单线程性能/平台性能/内存延迟/内存带宽、生态就绪。

责任编辑:gt

-

处理器

+关注

关注

68文章

20333浏览量

255045 -

ARM

+关注

关注

135文章

9588浏览量

393687 -

亚马逊

+关注

关注

8文章

2736浏览量

85890

发布评论请先 登录

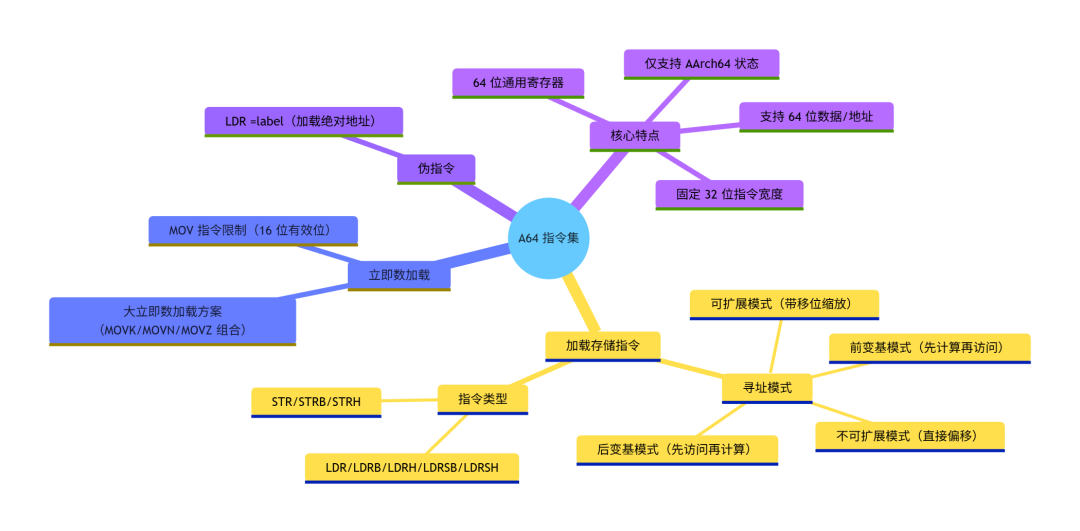

A64指令集通关笔记:加载与存储指令全解析

Mavell新一代ThunderX3发布,升级为ARM v8.3指令集架构

Mavell新一代ThunderX3发布,升级为ARM v8.3指令集架构

评论