尽管有关摩尔定律濒临消亡或跟不上时代的传闻不绝于耳,但半导体行业似乎多半仍在继续开发新工艺节点和日益复杂的设计。因此,各家公司几乎无休止地在为下一节点做准备,进而过渡至新的节点。

对晶圆代工厂而言,这种准备工作以新器件、新工艺工具和新工艺流程为中心。同时,他们必须确保为客户提供合格规则集(规则文档)。设计公司专注于定义电路功能和性能目标,同时确保他们拥有所需的设计软件和硬件并已经准备好进行使用,以便在合理的周转时间内实现设计 signoff。

虽然很少谈论到,但电子设计自动化 (EDA) 行业也一直在为下一节点做准备。随着各种新工艺技术和新设计功能的不断涌现,现在越来越需要提高自动化能力,以自动利用一套经过晶圆代工厂验证的工具进行验证,同时在不增加运行时间的情况下保持最高的准确度。本文将深入探讨下一节点的开发挑战,以及Mentor, a Siemens Business 如何为每个“下一节点”准备 Calibre®nmPlatform。

下一节点的计算挑战

衡量半导体行业向前发展势头的经典指标是设计中的集成电路 (IC) 晶体管数量。摩尔定律描述的是经验观察:每片 IC 的晶体管数量以往大约每两年翻一番。近年来,宣称摩尔定律濒临消亡的声音似乎一直不绝于耳,但经验证据持续表明事实并非如此。图 1 显示了最广为人知的 IC 芯片的晶体管数量随时间变化的最新复合图 [1]。数据显示,晶体管数量在整个四十五年间一直稳定增加,大多数现代芯片的晶体管数量接近 20 万亿个。

图 1:IC 晶体管数量随时间的变化。

(数据来源:https://en.wikipedia.org/wiki/Transistor_count;数据可视化:OurWorldinData.org;Max Roser 根据CC-BY-SA授权使用。)

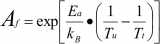

设计规则检查 (DRC) 复杂度与设计中的多边形数量成正比。虽然晶体管数量对前道工序 (FEOL) 层多边形数量有直接影响,但它本身并不能说明多边形总数的整体增加。中段工序 (MOL) 和后道工序 (BEOL) 层不仅显示每层多边形数量的增加,而且显示先进工艺节点通常需要额外的互连层。多边形数量增加的多种来源意味着像 Calibre 套件这样的验证工具必须应对超过摩尔定律增长率的多边形处理量。

当然,与晶圆代工厂工艺相关的设计规则不只是与设计中的总设计层数呈函数关系。随着时间推移,由于更复杂的环境感知且对变化敏感的设计组件和工艺技术被整合到最先进的工艺节点中,在任何给定层上必须检查的问题类型也会增加。图 2 显示了其中几项新工艺技术和设计敏感性,它们不仅需要更多的检查,而且需要全新的检查类型。该图将层数的增加与所需检查类型的增加相对照,说明了设计规则的数量和实现这些规则所需的运算是如何随着工艺节点发展而增加的。每次检查都需要很多行编码来实现,图上的平均 DRC 运算数说明了软件为正确检查设计而实际必须执行的步骤数。

图 2:不同工艺节点的新功能要求和 DRC 规则/代码复杂度。

最终,验证现代 IC 所需的计算能力和资源是由规则复杂度乘以设计的总多边形数决定的。任何懂数学的人都会立即注意到,两个指数增长的趋势相乘会带来相当困难的问题需要克服。Mentor 意识到,为了解决这个似乎巨大无比的挑战,我们要跳出传统解决方案的思维,探求所有可能的途径来扩展和提高工具集的性能与生产力。Calibre 团队不断为 Calibre 工具库添加基本的新功能,以便为新的和扩展的需求提供准确的自动检查,同时仍然让公司能够满足其上市时间安排。

夯实基础

应对这种爆炸性计算挑战的两个最明显要素是原始引擎速度和存储器。尽管 Calibre 套件已经存在了几十年,但基础代码库在不断优化,甚至完全重写,不仅仅是为了添加新功能,还为了显著提高其执行现有功能的能力,以及利用现代分布式和云计算基础设施。

图 3 显示了同一 Calibre® nmDRC™ 运行集(运行文档)的不同软件版本的归一化运行时间趋势。每个数据点代表平均 20 个实际的客户设计,反映了 Calibre 底层引擎这个单一因素(其他因素均保持不变)随着软件版本的更替所实现的改进。在这三年的时间跨度内,引擎速度提高了 80%。这一趋势表明了 Mentor 优化所有 Calibre 物理和电路验证工具性能的方式。

图 3:不同软件版本的归一化 Calibre 引擎运行时间趋势。

存储器使用率也是提高工具性能的关键因素。图 4 比较了最近的两个 Calibre nmDRC 版本在六种不同 7 nm 设计上的表现。随着底层数据结构和存储器管理技术的改进,存储器使用率稳定下降 40-50%。同样,这一进展代表了 Calibre nmPlatform 所实现的性能改进。虽然 Calibre nmPlatform 在使用最少存储器方面已经处于业界领先地位,但 Mentor 仍在不断寻求进一步改进的机会。

图 4:Calibre nmDRC 工具最近发布的各版本在存储器使用率方面的改进比较。

-

IC

+关注

关注

36文章

6258浏览量

184237 -

摩尔定律

+关注

关注

4文章

640浏览量

80613 -

节点

+关注

关注

0文章

226浏览量

25418 -

晶体管

+关注

关注

78文章

10250浏览量

146273

发布评论请先 登录

中科曙光scaleX640超节点亮相2025世界计算大会

如何验证电网关键节点的电能质量监测装置的现场接地系统是否符合单点接地标准?

负载开关IC数据表中相关术语和功率损耗计算方法

华为发布全球最强算力超节点和集群

多达 48 个计算节点!Firefly 推出 CSC2-N48 AI 算力服务器

车用IC寿命如何精准计算

HarmonyOS NEXT应用元服务布局优化精简节点数

HarmonyOS NEXT应用元服务布局优化精简节点数

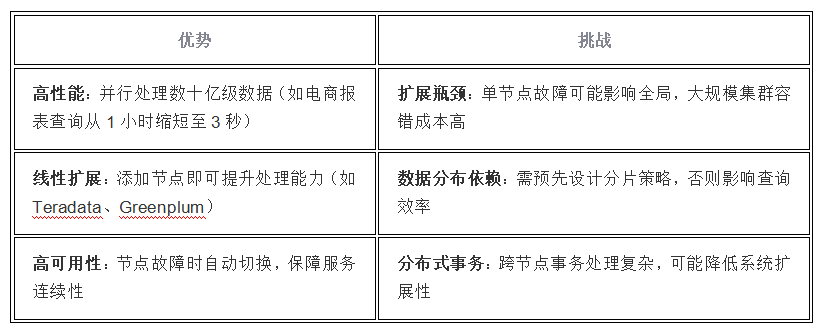

多节点并行处理架构

使用AD2428时,通过主节点发现从节点的过程中遇到的问题求解

CAN通信节点多时,如何减少寄生电容和保障节点数量?

如何优化CMOS逻辑IC的性能

怎么准备ic节点的计算

怎么准备ic节点的计算

评论