前面介绍的都是模拟电子电路,接下来在介绍一些数字逻辑电路的知识,先介绍555集成电路。555集成电路大量应用于电子控制、电子检测、仪器仪表、家用电器、音响报警、电子玩具等诸多方面。可用作振荡器、脉冲发生器、延时发生器、定时器、方波发生器、单稳态触发振荡器、双稳态多谐振荡器、自由多谐振荡器、锯齿波产生器、脉宽调制器等。

555集成电路的特点

1.555在电路结构上由模拟电路和数字电路组合而成,他将模拟功能与逻辑功能融为一体,能够产生较为精准的时间延迟和振荡。而且还扩宽了模拟集成电路的应用范围。

2.555集成电路采用单电源。双极型555的电压范围为4.5~15V,而CMOS 型的电源适应范围更宽,为2~18V。这样,它就可以和模拟运算放大器还有TTL或CMOS数字电路共用一个电源。

3.555可独立构成一个定时电路,且定时精度较高。

4.555最大输出电流(双极型)可达200mA,带负载能力强,可直接驱动小电机、喇叭、小继电器等负载。

555集成电路实物图

目前市场卖的555集成电路的封装外形多为8脚双列直插式封装,当然还有贴片封装,这里不做解释,外形见图示。

NE555P芯片实物图

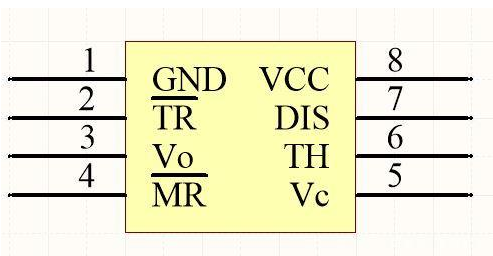

引脚排列图如图示

555芯片引脚图

1——接地(负极);2——触发端;3——输出端;4——复位端;

5——控制电压;6——阈值电压;7——放电端;8——电源端(正极)。

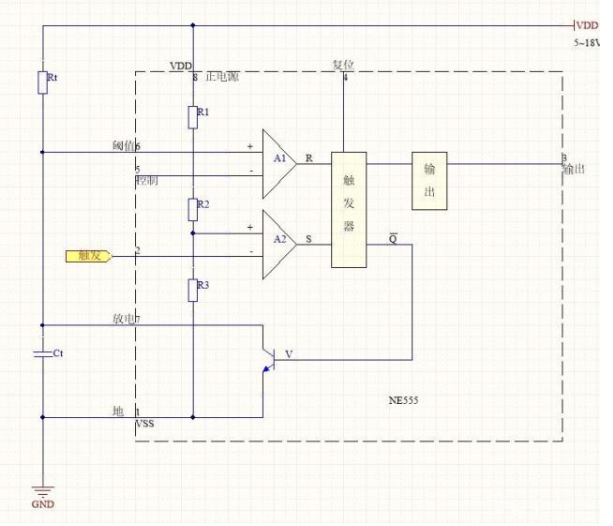

555结构组成

虽然很多半导体公司都在生产各自型号的555芯片,但是其内部电路大同小异,且都具有相同的引出功能端。

555集成电路内部一共有21个三极管、4个二极管和16个电阻,组成两个电压比较器、一个R-S触发器、一个放电三极管和由3个5KΩ电阻组成的分压器。图中A1、A2是两个高增益的电压比较器,它们的输出端分别接到触发器的R(置0)端和S(置1)端。V是放电二极管,R1、R2、R3就是3只5KΩ电阻,组成分压器,555芯片的名称因此而得名。

A1称为上比较器,A2为下比较器,由于R1、R2、R3阻值相等,所以电路的第5脚电位固定在2/3Vcc上,Vcc为工作电源电压,第6脚是阈值输入端。下比较器A2的同相输入端,电位被固定在1/3Vcc上,反相输入端即在第2脚作为触发输入端。A1与A2的输出端分别送到R-S触发器的置位端S(即置1),和复位端R(即置0),以控制输出端第3脚的电平状态和放电三极管VT的导通与截止。

555内部等效图

555集成电路原理介绍

图中的外部元件Rt、Ct,与555集成电路接成的是单稳态电路。由于A1的基准设在反相输入端(2/3Vcc),所以当阈值端即第6脚电压高于或等于2/3Vcc时,A1输出高电平,使触发器复位,输出端第3脚为低电平,Q=0,所以!Q=1;(!Q代表非Q),此时放电管VT导通,555电路的第1、7两脚被VT短接,外部电容Ct,可以通过第1、7脚间放电。而A2的基准是设在同相输入端,因此只有触发端第2脚电位低于或等于1/3Vcc时,A2输出高电平,触发器被置位,第三脚输出高电平,!Q=0,放电管VT截止,第1、7两脚间断开,等效为第7脚悬空,此时外接电容Ct,可通过电阻Rt充电。阈值端第6脚只对高电平(≥2/3Vcc)有效,对低电平不起作用。触发器第2脚只对低电平(≤1/3Vcc)有效,对高电平不起作用。因此触发端第2脚电位低于1/3Vcc时,555的第3脚就输出高电位,当触发端第6脚电位高于2/3Vcc且第2脚电位高于1/3Vcc时,555的第3脚输出低电平。

555集成电路还设置了强制复位端第4脚,如果该脚为低电位(≤0.4V)时,不管第2/6脚电位高低如何,第3脚总是输出低电平。555集成电路的第5脚为控制端,可以通过外接分压电阻或稳压管来改变A1、A2两个电压比较器的基准电压以扩大其应用范围, 如果在第5脚与第1脚之间外接一只5.1V稳压管,则上比较器A1的基准电压就是5.1V,而比较器A2的基准电压便为5.1V×1/2=2.6V。如果在第5脚接一个交变电压,则A1、A2两比较器的基准电压将随时间而变化,从而使外部电路充放电时间也随之变化,也就是起到调制作用。大部分电路通过103(0.01uF)电容器接地,以消除干扰。

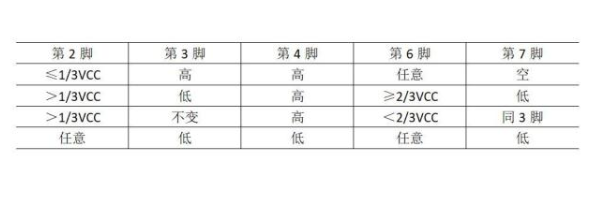

555集成电路简明真值表

555集成电路真值表

555集成电路分为双极型和CMOS型两种。CMOS型的555电路一般命名为7555,也叫NE7555,而双极型的为NE555,有所区别。上述所讲的是双极型的555芯片,工作电压为4.5V~15V,第3脚输出驱动电流可达200mA,可直接驱动小型继电器,但缺点是静态电流也偏大。

先了解一下555集成电路的基本原理,积少成多,对学习数字逻辑电路有一定的帮助,建议小伙伴多学学。领悟之后可对相关电路进行学习用三个555芯片设计声光计时器项目。

-

电源

+关注

关注

185文章

18974浏览量

264438 -

集成电路

+关注

关注

5464文章

12669浏览量

375615 -

模拟电路

+关注

关注

126文章

1610浏览量

105776

发布评论请先 登录

技术资讯 I 如何识别同步开关噪声

集成电路制造中常用湿法清洗和腐蚀工艺介绍

门控时钟(Clock-gating)介绍

集成电路可靠性介绍

华大九天Empyrean Liberal工具助力数字集成电路设计

555数字集成电路介绍

555数字集成电路介绍

评论