FREMONT,加利福尼亚州 - 两家主要芯片组装商 - 香港ASAT有限公司和亚利桑那州Chandler的Amkor科技公司 - 正在寻求新的微型线焊无铅封装的联合电子器件工程委员会(Jedec)规范.ASAT位于加利福尼亚州弗里蒙特的美国子公司首席执行官理查德布兰卡托表示,新的封装“已经起飞在无线手机市场,并将在各种新应用中扩展。“他表示,所有供应商的开放式行业标准将确保新芯片封装的广泛采用。

Amkor将其封装称为MicroLeadFrame,而ASAT则称其为无铅塑料芯片载体(LPCC)。 Amkor发言人证实,两家公司都在寻求新型无引线封装的Jedec标准。

两种版本都消除了引脚,并通过芯片底部的阵列将封装引线键合。这使得封装尺寸几乎与球栅阵列器件相同,但成本要低得多,因为可以使用传统的引线键合。

Bancato表示,新型微型封装的首次应用是适用于较小的20至30引脚数,可轻松适应底部连接技术。然而,他说,除了中心底部阵列之外,通过在封装内部周边运行环或一系列环,可以实现更大的引脚数。他说,一个更大的17×17毫米封装可以在这种无引线配置中拥有多达256个引脚。

Amkor已经表示该公司正在考虑授权第二个来源制造其MicroLeadFrame封装。 ASAT的Brancato表示他的公司正在考虑授权其技术,尽管“两家公司都在全面生产,我认为新包装现在有足够的容量。”

Brancato说ASAT也在研究如何将其目前的基于胶带的包装技术扩展到更广泛的产品。当前的方法在磁带上形成一个小电路,基芯片连接到该电路上。

ASAT官员表示,该磁带的功能与通常在印刷电路板上的互连电路相同。然而,这项技术的成本低于电路板互连,并且直接将芯片连接到磁带上可以消除芯片封装与电路板外部连接时产生的电感和阻抗。

执行官表示,ASAT正在开发中磁带上的多层电路用于更复杂和更高性能的芯片互连。他还表示,该磁带可用于降低传统多芯片模块的成本,这些模块需要将金凸块连接到每个单独的芯片上。 ASAT正在探索将金凸块放在磁带上,准备将裸芯片放在它们上面。

他说无源器件也可以预先安装在磁带电路上,然后连接有源芯片。他认为这比现有的无源印刷电路板上的无源方法成本低。

ASAT正在弗里蒙特及其香港工厂的研发中心进行开发工作。

-

封装

+关注

关注

128文章

9143浏览量

147900 -

PCB打样

+关注

关注

17文章

2977浏览量

23338 -

华强PCB

+关注

关注

8文章

1831浏览量

29131 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44389

发布评论请先 登录

叠层固态电容:小型化封装,释放PCB更多空间

CR-2450型小型液压纽扣电池封装机

基于JEDEC标准的闩锁效应测试方法

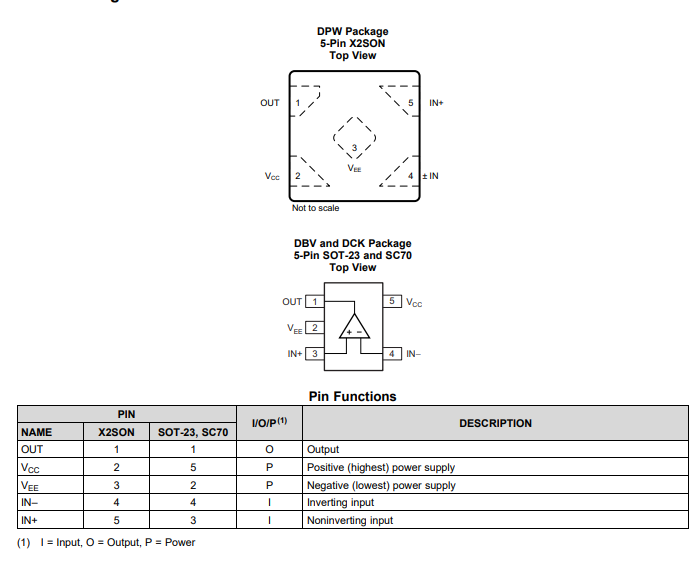

TLV7021 具有漏极开路输出的低功耗小型比较器技术手册

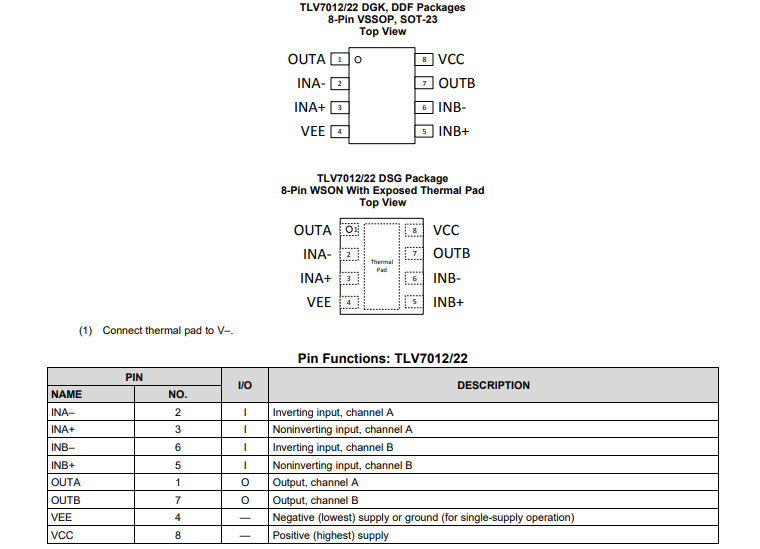

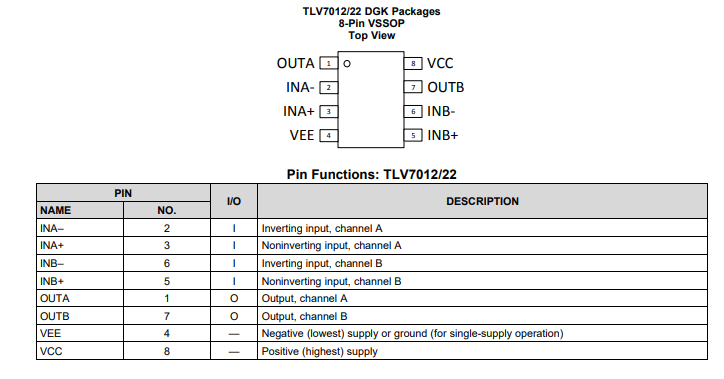

TLV7022 微功耗小型比较器(双通道、漏极开路输出)技术手册

TLV7012 微功耗小型比较器(双通道、推挽输出)技术手册

ASAT,Amkor寻求Jedec批准小型无铅封装

ASAT,Amkor寻求Jedec批准小型无铅封装

评论