您正在设计最新的子系统,并且有人告诉您尽可能多地放置100 nF去耦电容,尽可能接近所有集成电路,就像我们在上一颗卫星上所做的那样。作为一名设计工程师,很自然地质疑这种解耦的定性方法。它的目的是什么?为什么100 nF?其他价值怎么样?多少个电容?有多接近芯片和方向?

您是否知道在某些情况下,您可以移除PCB上的许多去耦电容,而不会影响子系统的性能或可靠性?如何优化去耦,避免过度设计设计,减少BOM,并提供更便宜,更可靠的硬件,正确的第一次?

为什么要去耦?

配电网络(PDN)的目的是为其必须提供的每个集成电路提供定义的稳压电压。然而,在DC-DC转换器和其负载之间,PDN内有许多互连;例如迹线,焊盘,过孔,平面,封装引线,键合线等,如下图所示:

图1提供FPGA的PDN及其互连的示例。

如果每个芯片的电流消耗恒定,由于各种互连的串联电阻,这将导致PDN内的恒定IR压降。然而,集成电路的瞬态需求在每个时钟周期变化,并且PDN的阻抗包括电感和电容元件。通过复阻抗的快速变化的电流将产生称为轨道下垂或轨道坍塌的电压降,如果电容器无法供电,则可能导致纹波过大,调节器不稳定,时序裕度减小,电压下降或功能故障它的负载与所需的电流。下垂会将噪声注入电源和接地层,从而在PCB边缘发出不必要的EMI,而去耦也可以减少这种干扰。

调节器对瞬态电流需求的响应要慢于它所提供的器件的运行速度。在PDN内旁路或去耦电容器的目的是通过存储在下垂期间释放的电荷来消除瞬态电压降。去耦的作用是为每个集成电路提供这种电容,在很宽的频率范围内具有最小的寄生阻抗。整个环路电感决定了从PDN到负载的电荷传输速度,每个电容器都会引入固有的ESR和ESL,以及不需要的安装,通孔和平面扩展电感。 PDN设计的目标是通过最小化电感来最大化电容的有效性,从而将阻抗保持在所需带宽上的目标值以下。这将供电轨的任何变化限制在可接受的规定极限,例如, 5%的波纹。点击航天工业希望利用需要低电压,高电流电源轨的超深亚微米集成电路的性能优势。这些芯片在更快的频率下工作,并且当它们更频繁地切换时,每个周期中消耗的能量也更频繁地消耗。将所有这些结合起来意味着更高的电流将在更短的时间内发生变化,并且可以容忍的相对噪声量将减少。

多少去耦?

在设计PDN时,目标应该是选择最小数量的去耦电容,以确保阻抗在所需带宽内保持低于目标值。

来自直流的低频在10 kHz时,调节器控制着集成电路看到PDN的阻抗。从10到100 kHz,大容量电解电容和钽电容提供低阻抗去耦路径,之后PCB级去耦接管。

离散板级去耦的有效性受到很大影响其整体回路电感包括固有ESR和ESL,以及安装,通孔和平面扩展电感。在更高的频率下,PCB的电源和接地层的平行板电容接管以提供低阻抗路径。原则上,分布式平面电容提供了提供高达GHz频率的低电感的潜力;然而,由于芯片封装PDN的串联电感,PCB级去耦限制在几百MHz。

通过利用相邻电源和地平面之间的嵌入电容,即通过增加平面的相对面积通过减小它们的间隔和/或通过使用具有更高相对介电常数的电介质,可以将更宽带宽上的平面间电容的有效性提高到可以去除许多物理的,离散的去耦电容器的水平。电介质厚度影响平面扩展电感,并且最小化这种间隔降低了电容器的整体安装电感,使其能够进一步远离其负载。然而,在实践中,ESA的ECSS-Q-ST-70-12C标准规定了最小间隙为100μm(3.9密耳),这限制了嵌入式解耦对ESA任务的有效性。

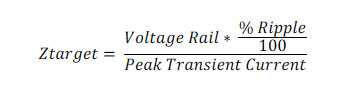

高于几百MHz,芯片看到的阻抗由片内电容(栅极和电源接地金属化)决定,而板级去耦将无法将其降低到封装的固有PDN电感以下。 BR>对于要去耦的每个电源轨,可以通过根据器件数据手册中规定的最大容许纹波以及瞬态电流计算目标阻抗来启动PDN的设计:

对于许多组件,仅列出最大功耗,并且可以使用多种方法来推断峰值瞬态需求,例如 0.5 * Imax 。一些FPGA供应商在地点和路线之后或者从功率预测电子表格中提供更多的定量估计。

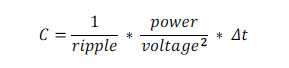

我们还可以通过假设去耦提供在某段时间内必须流动的所有电荷来估算所需的电容总量,Δt:

例如,如果ADC从3.3V电压轨消耗2W且指定纹波为5%,并且稳压器在不到10μs内无法响应电压变化,那么我们需要提供37μF的去耦。低于此值,电容器上的电压下降将超过允许的5%纹波。

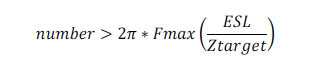

对于每个电压轨,还可以估算并联所需的最小电容数,以满足目标阻抗直至最大频率:

等式表明,为了减少电容器的数量,必须减少ESL。每个电容器的环路电感越低,在更高频率下实现目标阻抗所需的电感越少。具有较低固有ESL的较小电容器是可用的,例如, AVX将在今年晚些时候提供符合空间要求的0402,并且应尽一切努力减少整体回路电感,即附件,通孔和平面扩展电感的几何形状。

设计人员通常只会增加电容器的数量希望通过并联添加更多电容来降低环路电感。然而,当电容器紧密间隔时,由于通孔之间的互感,在平面和电容器焊盘之间看到的电感不会降低为1/N,这是标准做法。

-

电容

+关注

关注

100文章

6525浏览量

160093 -

PCB打样

+关注

关注

17文章

2982浏览量

23680 -

华强PCB

+关注

关注

8文章

1831浏览量

29330 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

在什么情况下以移除PCB上的许多去耦电容

在什么情况下以移除PCB上的许多去耦电容

评论