声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半导体

+关注

关注

339文章

31248浏览量

266592 -

PVD

+关注

关注

4文章

51浏览量

17674

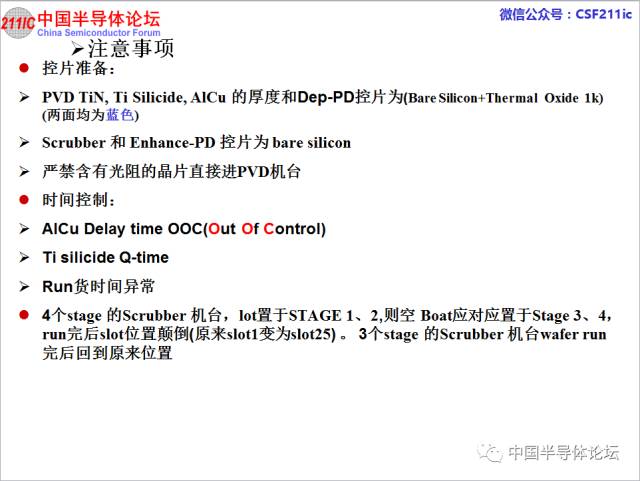

原文标题:半导体知识:PVD金属沉积制程讲解

文章出处:【微信号:CSF211ic,微信公众号:中国半导体论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

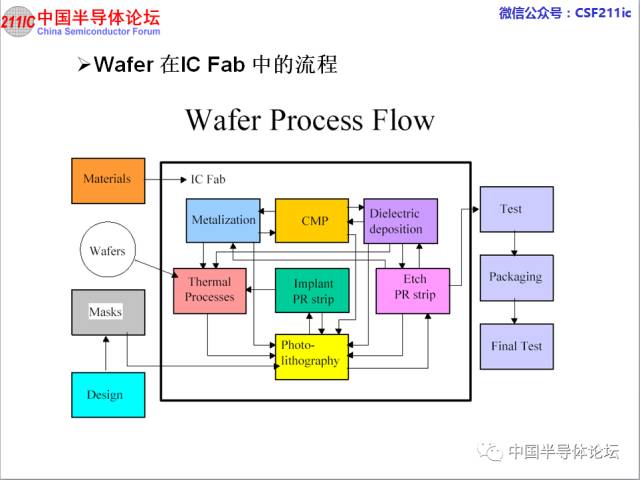

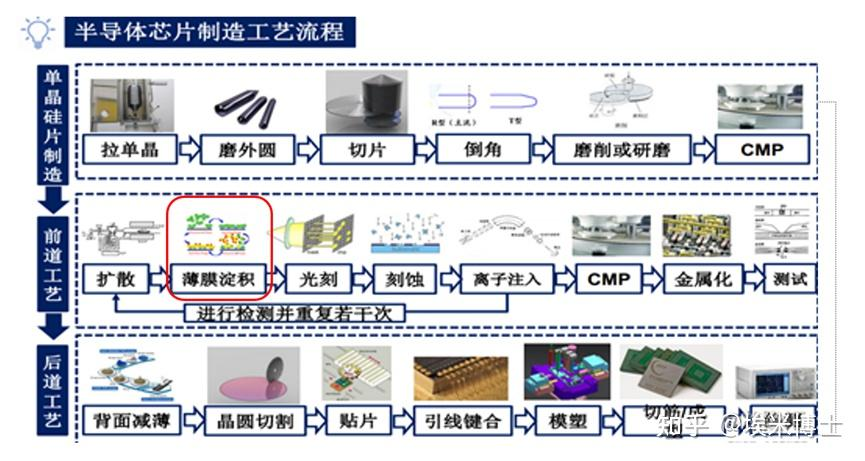

半导体制程简介

`半导体制程简介微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术(silicon- based micromachining),原本就肇源于半导体组件的制程技术,所以必须先介

发表于 08-28 11:55

半导体制程

的积体电路所组成,我们的晶圆要通过氧化层成长、微影技术、蚀刻、清洗、杂质扩散、离子植入及薄膜沉积等技术,所须制程多达二百至三百个步骤。半导体制程的繁杂性是为了确保每一个元器件的电性参数和性能,那么他的原理又是

发表于 11-08 11:10

《炬丰科技-半导体工艺》硅纳米柱与金属辅助化学蚀刻的比较

书籍:《炬丰科技-半导体工艺》文章:硅纳米柱与金属辅助化学蚀刻的比较编号:JFSJ-21-015作者:炬丰科技网址:http://www.wetsemi.com/index.html摘要

发表于 07-06 09:33

半导体制程基本知识

微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术(silicon- based micromachining),原本就肇源于半导体组件的制程技术,所以必须先介绍清楚这类制程。

发表于 08-28 11:56

•286次下载

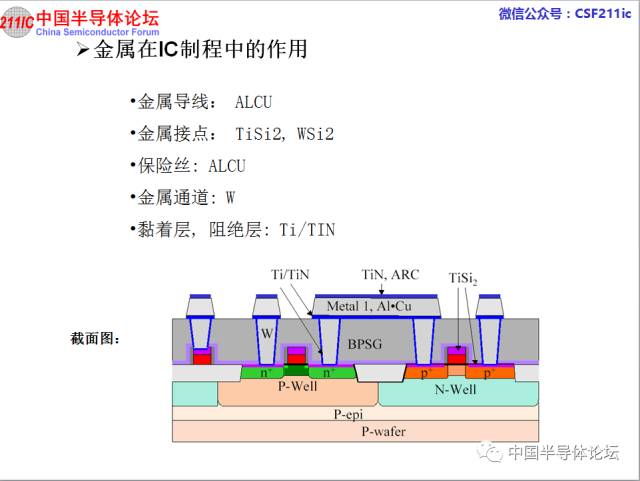

半导体工艺之金属布线工艺介绍

本篇要讲的金属布线工艺,与前面提到的光刻、刻蚀、沉积等独立的工艺不同。在半导体制程中,光刻、刻蚀等工艺,其实是为了金属布线才进行的。在金属布

发表于 04-25 10:38

•3141次阅读

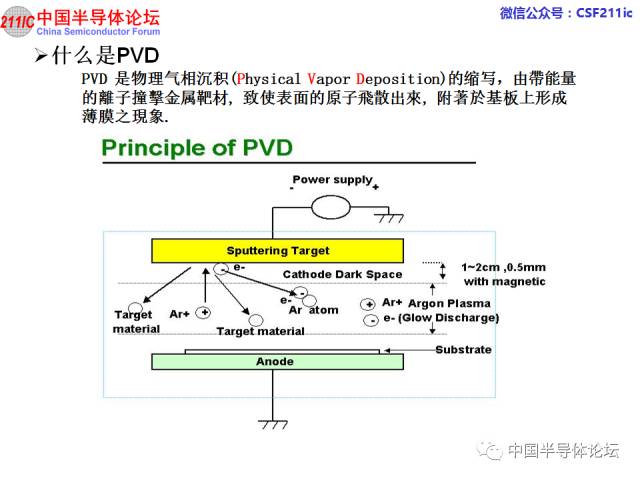

半导体前端工艺之沉积工艺

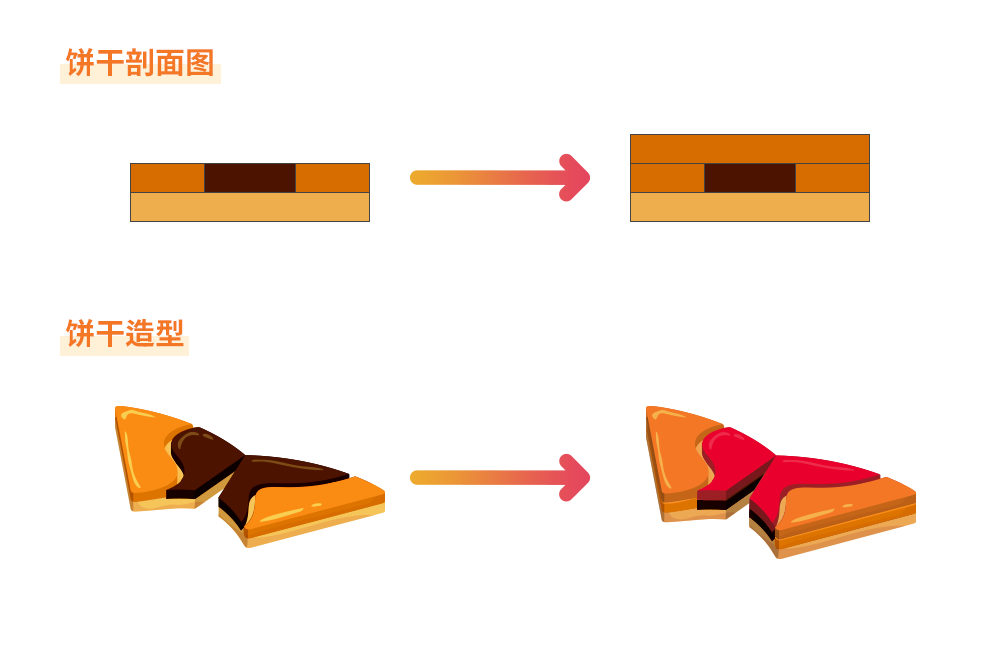

在前几篇文章(点击查看),我们一直在借用饼干烘焙过程来形象地说明半导体制程 。在上一篇我们说到,为制作巧克力夹心,需通过“刻蚀工艺”挖出饼干的中间部分,然后倒入巧克力糖浆,再盖上一层饼干层。“倒入巧克力糖浆”和“盖上饼干层”的过程在半导体制程中就相当于“

铜在半导体领域的应用

半导体技术在当今社会已成为高科技产品的核心,而在半导体制造的各个环节中,铜凭借其出色的性能特点,已成为众多工艺应用的关键材料。在半导体领域中,铜主要被用于制造互连线路。在传统的互连制造中,铜通常被用作通过化学气相淀积(CVD)或

流量控制器在半导体加工工艺化学气相沉积(CVD)的应用

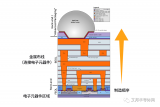

薄膜沉积是在半导体的主要衬底材料上镀一层膜。这层膜可以有各种各样的材料,比如绝缘化合物二氧化硅,半导体多晶硅、金属铜等。用来镀膜的这个设备就叫薄膜沉

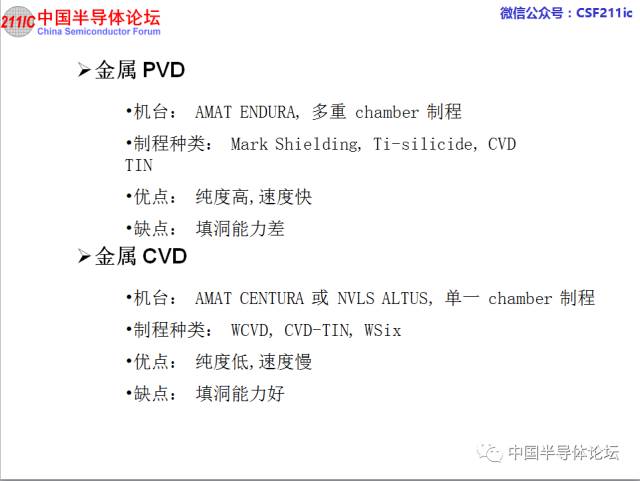

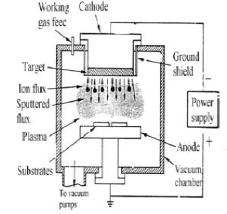

半导体知识:PVD金属沉积制程讲解

半导体知识:PVD金属沉积制程讲解

评论