CPU的内存区域是全系统声明的区域。由此,这些区域不必在逻辑块中声明。每个CPU均提供以下有各自地址范围的内存区域。

2022-08-25 09:26:33 3471

3471 鉴于KAIST的HPC根源,将DirectCXL原型放在一起的研究人员专注于使用远程直接内存访问(RDMA)协议将CXL内存池与跨系统直接内存访问进行比较。

2022-09-23 10:50:26 1845

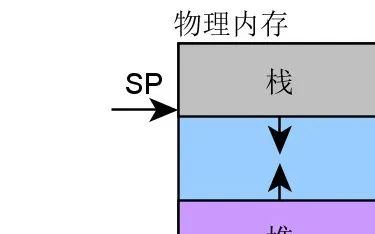

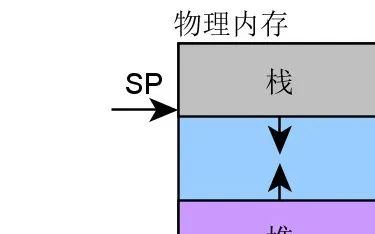

1845 CPU写物理内存的过程:CPU先给出要写入数据的物理地址对应的虚拟地址,通过MMU转化为物理地址,若cache中没有命中,则将要写入数据的物理地址放到系统总线上。

2023-03-16 09:46:48 2111

2111

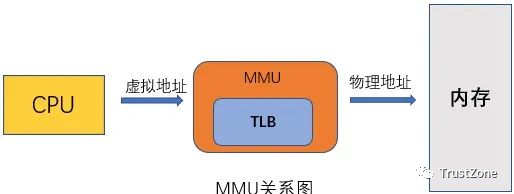

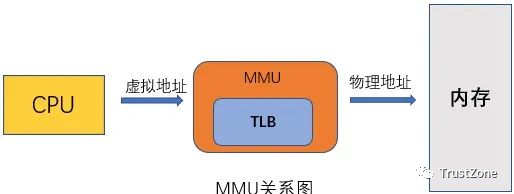

MMU(Memory Management Unit,内存管理单元)是一种硬件模块,用于在CPU和内存之间实现虚拟内存管理。

2023-08-03 10:05:00 1400

1400

本文内容包括CPU、内存和GPU知识,本期重点更新GPU和CPU部分知识。比如:GPU更新包括架构演进,最新产品A100、选型策略、架构分析、散热和规格分类等。

2023-11-13 11:47:24 2922

2922

CW32L052支持DMA(Direct Memory Access),即直接内存访问,无需CPU干预,实现高速数据传输。数据的传输可以发生在: • 外设和内存之间 :例如ADC采集数据到内存,这种

2024-02-28 16:48:51 1626

1626

`访问一个MMU的页表里没有填写映射描述符的虚拟地址,会发生什么?百度没有找到明确的解答,求前辈指导。`

2018-06-25 09:40:07

一、MMU的产生 许多年以前,当人们还在使用DOS或是更古老的操作系统的时候,计算机的内存还非常小,一般都是以K为单位进行计算,相应的,当时的程序规模也不大,所以内存容量虽然小,但还是可以容纳当时

2018-07-03 08:19:31

2.2.4 内存访问的软件顺序程序流程中指令的顺序并不能保证相对应的内存处理顺序,原因如下处理器可以重新排序一些内存获取用来提高效率,当然,这种改变不能影响指令顺序的行为处理有多个总线接口在内存

2021-08-24 07:46:25

请问内存与cpu之间的接线按照什么原理排序的,以及cpu如何访问内存,编写驱动是不是内存大小不一样驱动也不一样?

2022-11-28 07:07:05

内存交错功能可并行阅读大内存芯片,减小内存访问时间。内存交错功能最多可并行访问单CPU内存板上的 32 个内存芯片。

2019-09-18 09:01:19

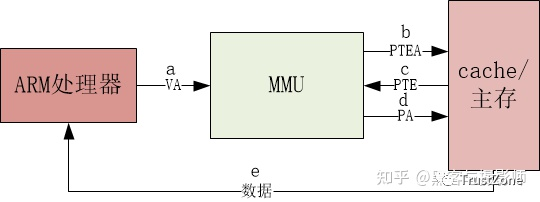

中,所以处理器引入MMU后,读取指令、数据需要访问两次内存:首先通过查询页表得到物理地址,然后访问该物理地址读取指令、数据。为了减少因为MMU导致的处理器性能下降,引入了TLB,可翻译为“地址转换

2020-11-04 10:52:25

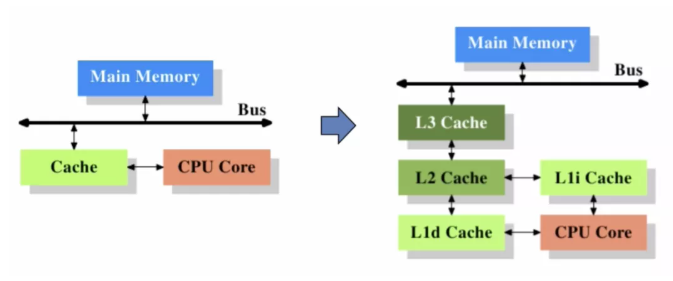

寄存器不占用地址空间,CP15是操纵MMU/Cache的唯一途径。Cache/Write Buffer的功能Cache通过预测CPU即将要访问的内存地址(一般都是顺序的),预先读取大块内存供CPU访问

2017-08-29 11:10:14

MMU-600AE是MMU-600系统级内存管理单元(SMMU)的功能安全(FUSA)变体,可将输入地址转换为输出地址。此转换基于MMU-600AE内部寄存器和转换表中提供的地址映射和存储器属性信息

2023-08-09 06:28:46

物理地址(IPA)转换为输出物理地址(PA)的阶段2转换。MMU-400使用来自请求主机的输入来识别上下文。该上下文向MMU-400传达要使用什么资源进行翻译,包括要使用哪些翻译表。

图1-1显示了示例系统中的单个MMU-400,它为直接存储器访问(DMA)控制器执行地址转换功能。

2023-08-02 09:21:57

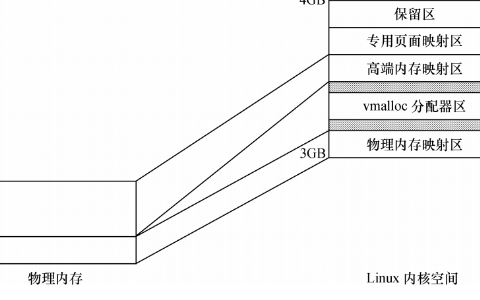

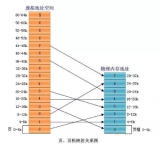

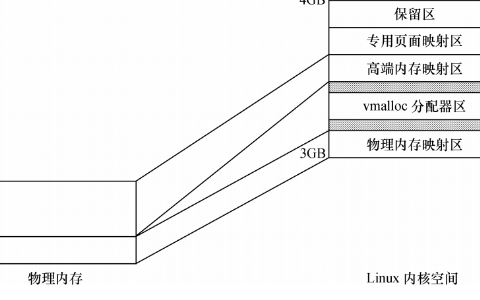

将用于内核空间,内核提供了相关的配置项来修改该比例,也就是说Kernel最多寻址1GB的虚拟地址空间。当CPU启动MMU后,CPU访问的时虚拟地址空间,然后由MMU根据页表转换成物理地址,页表是由

2022-04-24 14:20:19

的指令或者数据调入cache,这样当运行下一条指令或用到下一条数据时直接从cache中查找,如果查找不到再访问内存,以此加快CPU执行速度。icache可以直接开启,而dcache需要开启MMU之后才能

2022-05-11 17:43:27

这个功能,还有不少复杂的情况要处理。在ARM系统中,内存有两种不同且对立的属性,即共享(Shareable)和非共享(Non-shareable)。共享意味着该段内存可以被系统中不同处理器访问到,这些

2022-04-22 09:44:00

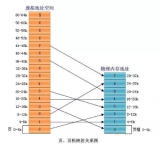

] 用来形成物理地址的对应位。MMU 把 CPU 产生的虚拟地址转换成物理地址去访问外部存储器,同时继承并检查访问权限。地址转换有四条路径。路径的选取由这个地址是被标记成节映射访问还是页映射访问确定。页

2020-10-23 15:29:49

ARM系统MMU(SMMU)体系结构为存储器管理单元(MMU)实施提供了灵活的实施框架,具有多个实施定义的选项。

该体系结构可用于系统级的MMU。

它基于转换表中保存的地址映射和内存属性信息,支持从

2023-08-12 06:25:35

MMU‑700是一个系统级内存管理单元(SMMU),用于将输入地址转换为输出地址。此转换基于MMU‑700内部寄存器和转换表中可用的地址映射和内存属性信息。

MMU‑700实现Arm®SMMU

2023-08-08 07:44:49

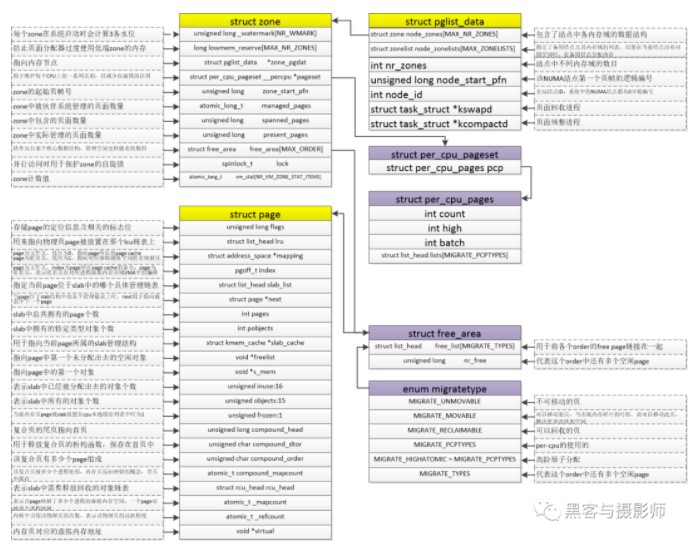

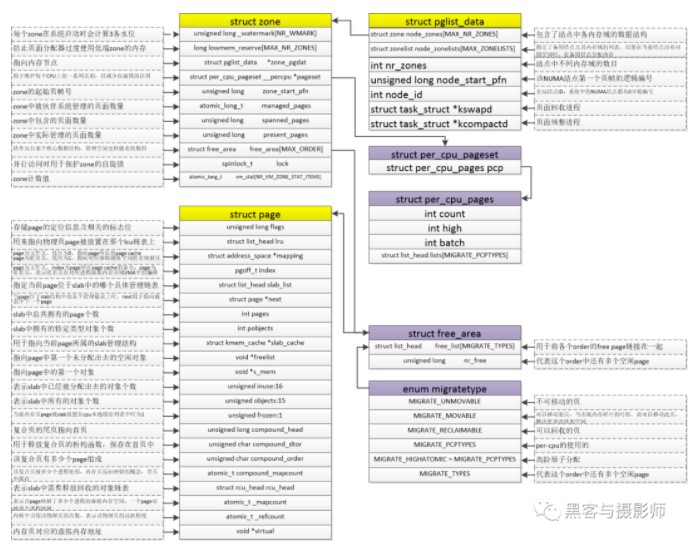

Linux内存系统---走进Linux 内存 1、内存是什么?1)内存又称主存,是 CPU 能直接寻址的存储空间,由半导体器件制成2)内存的特点是存取速率快2、内存的作用· 1)暂时存放 cpu

2020-08-26 08:05:43

? (*):这里的重叠 MMU 条目意味着,两个 MMU 条目统治/管理相同的内存区域但具有不同的访问权限。示例:- TLB1 条目 5 => EPN:0x2501 0000,页面大小:1KB,访问权限

2023-04-14 08:00:48

lookaside buffer)TLB是硬件上的一个cache,因为页表一般都很大,并且存放在内存中,所以处理器引入MMU后,读取指令、数据需要访问两次内存:首先通过查询页表得到物理地址,然后访问该物理地址读取

2020-11-03 16:23:21

大家好,这是关于DMA的非常基本的问题。1)什么是DMA(直接内存访问)和什么时候使用?2)它是如何提高CPU性能的?或如何独立工作,以节省时间和更快的性能和减少延迟?3)什么是间接的和平的模式?4

2019-01-25 10:45:34

通常MCU片内的闪存(FLASH)挂接在内存总线上,CPU可以无限制的访问FLASH内的任何区域。要实现对单颗MCU内片FLASH进行多个用户区域划分并保护,避免在片内不同用户通过CPU指令直接读取

2022-11-02 06:45:02

(Memory Management Unit)的支持。MMU通常是CPU的一部分,如果处理器没有MMU,或者有MMU但没有启用,CPU执行单元发出的内存地址将直接传到芯片引脚上,被内存芯片(物理内存)接收,这

2020-10-23 15:53:31

处理器中断处理的过程是怎样的?处理器在读内存的过程中,CPU核、cache、MMU如何协同工作?

2021-10-18 08:57:48

如何通过公网plc访问到深层工业网络?

2021-09-30 06:00:50

众所周知,MMU的页表是由软件建立在外部内存中的。实际上有两条硬件路径需要访问这个页表:1 MMU硬件进行page table walk时,它会读取查找这个页表。2 软件修改这个页表的页表项

2022-10-24 15:45:24

。这就是我们操作系统需要做的事情,填写和修改表的程序代码的编写。线性地址转物理地址是谁来做呢?1. 回答:设置好页表信息后,CPU每次访问内存都通过MMU来查表并转换出物理地址。是硬件自动操作。所谓

2018-03-24 09:31:38

操作系统需要做的事情,填写和修改表的程序代码的编写。 线性地址转物理地址是谁来做呢?1. 回答:设置好页表信息后,CPU每次访问内存都通过MMU来查表并转换出物理地址。是硬件自动操作。 所谓的内存(物理

2017-11-20 14:46:39

Cache是高性能CPU解决总线访问速度瓶颈的方法,然而它的使用却是需要权衡的,因为缓存本身的动作,如块拷贝和替换等,也是很消耗CPU时间的。MMU的重要性勿庸置疑,ARM920T(和ARM720T

2017-08-19 22:42:08

这个概念,全部都使用一一映射的方式,那内核只能访问到1GB的物理内存,但实际上,我们是需要内核在内核空间能够访问所有的4GB的内存大小的,那怎么做到呢?方法就是我们不让3G-4G的空间都使用一一映射,而是将物理地址的[0x00,fix_addr](fix_addr

2017-08-22 11:22:34

控制器中如何设计MMU--虚拟内存管理机制

2017-12-15 09:53:37

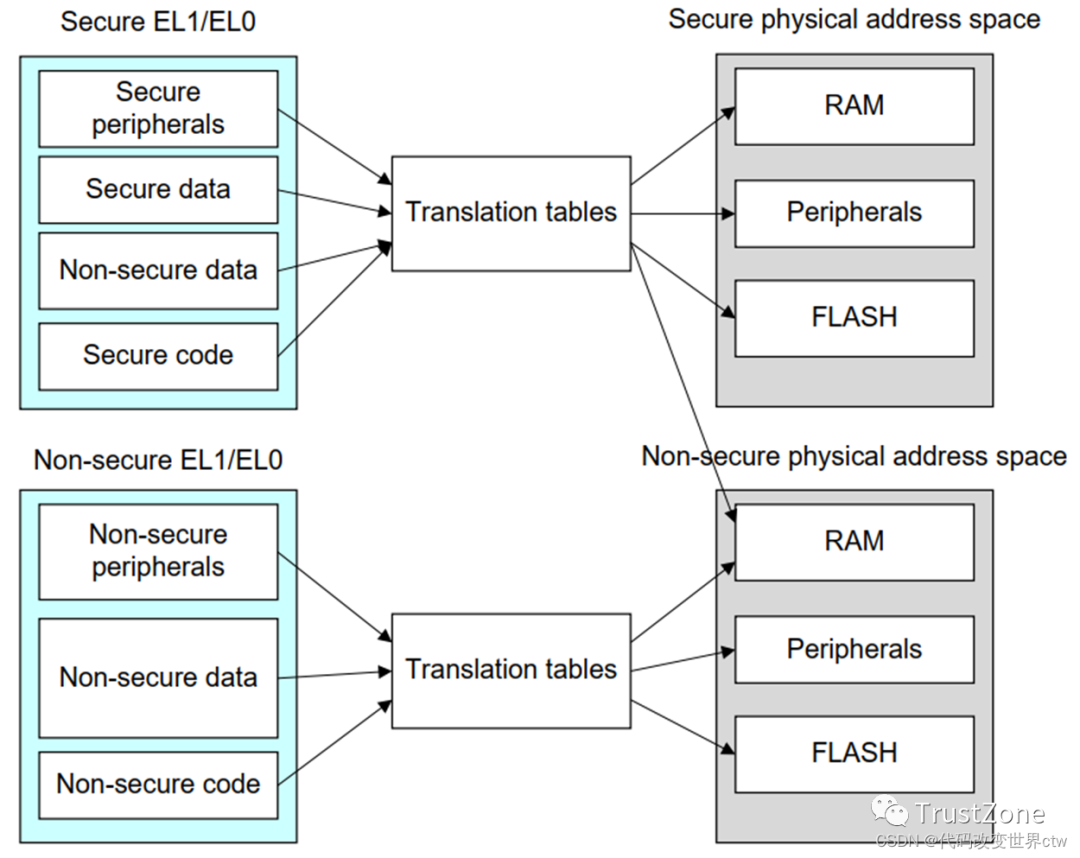

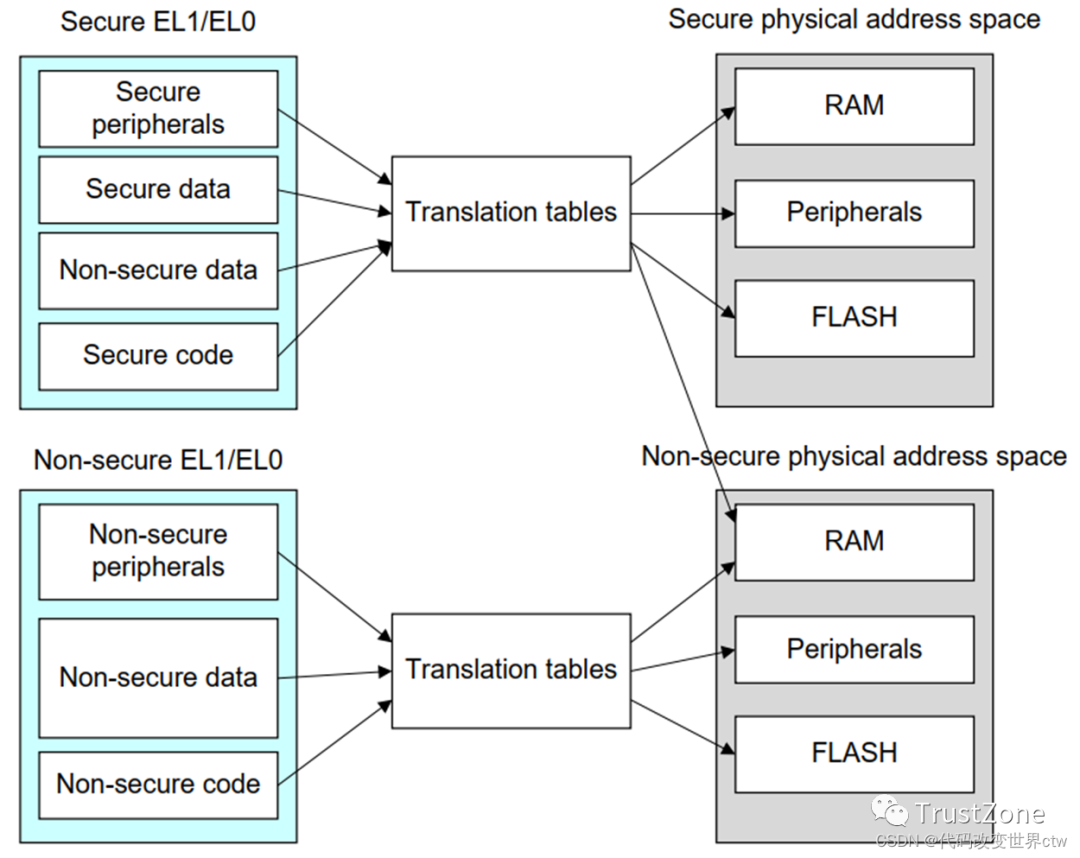

1、ARM v8-A 系列CPU的MMU隐射分析V8-A系列CPU有ELX,X为0~3等4个异常级别,又有AArch64和AArch32两种执行状态,异常级别可以决定执行状态,而对应着执行

2022-08-09 17:18:25

上对0xfa000地址的访问。因为物理地址和总线地址相同。 3)虚拟地址:现代操作系统普遍采用虚拟内存管理(VirtualMemoryManagement)机制,这需要MMU

2018-06-07 15:41:24

想问问 原子哥 ATK Esp8266 wifi模块可以访问到以太网吗?我们想要做一个接受微信平台信息的产品 用esp模块上网 可行吗?

2019-06-11 04:35:30

我一直在研究 BL2 上的 DDR 驱动程序,并注意到 *** 设置了对内存区域的访问,在研究 CW 脚本时也是如此。是否需要初始化 *** 才能访问 DDR 内存?我知道它不需要 MMU,但它与 TZ 一样吗?

2023-03-27 07:13:46

请问没有MMU的ARM芯片是否支持使用malloc()函数动态分配内存呢?求解答|

2022-10-17 15:41:33

关于cpu访问GPIO、UART、I2C等接口,与cpu访问FLASH、ROM、SDRAM的区别?cpu访问GPIO、UART等外设,是通过特殊功能的寄存器,不也是在访问内存上的某一地址吗?而cpu访问FLASH、ROM也是访问内存中对应的某一地址。请问,访问两类,有何区别?

2019-09-10 05:45:16

引入MMU后,读取指令、数据需要访问两次内存:首先通过查询页表得到物理地址,然后访问该物理地址读取指令、数据。为了减少因为MMU导致的处理器性能下降,引入了TLB,可翻译为“地址转换后援缓冲器”,也可

2020-11-19 14:57:04

ARM 内存管理单元MMU详细图解资料

本文描述基于存储器管理单元的系统结构, 包含以下内容:· 关于存储器管理单元的结构· 存储器访问的顺序

2010-03-03 16:22:37 97

97 集成的数据包缓冲区,具有智能内存管理单元 (MMU),可优化突发数据流量的处理。支持EEE、工业温度和 1588 时间戳。

2025-10-23 09:31:45

CPU所支持内存类型 内存

2009-12-24 10:54:57 1856

1856 远程访问服务器的标准内存容量 标准内存容量是指远程访问服务器随机所带的内存容量大小。不同的产品随机

2010-01-08 14:25:52 753

753 远程访问服务器的最大内存容量 最大内存容量是指远程访问服务器主板能够最大能够支持内存的容量。

2010-01-08 14:26:26 813

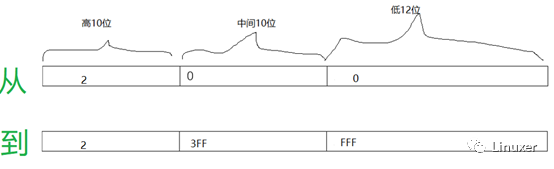

813 (11)实验十一:MMU 在理论上概括或解释MMU,这不是我能胜任的。我仅基于为了理解本实验中操作MMU的代码而对MMU做些说明,现在先简单地描述虚拟地址(VA)、变换后的虚拟地址(MVA)、物理地址(PA) 之间的关系: 启动MMU后,S3C2410的CPU核看到的、用到的只是虚拟

2009-01-01 02:29:42 17

17 C#教程之CPU内存使用率,很好的C#资料,快来学习吧。

2016-04-20 14:16:14 7

7 关于arm cpu内存的介绍

2017-02-15 23:53:38 5

5 5.4 多寄存器Load/Store内存访问指令 多寄存器Load/Store内存访问指令也叫批量加载/存储指令,它可以实现在一组寄存器和一块连续的内存单元之间传送数据。LDM用于加载多个寄存器

2017-10-18 15:56:19 1

1 4.2 内存访问指令寻址 根据内存访问指令的分类,内存访问指令的寻址方式可以分为以下几种。 ① 字及无符号字节的Load/Store指令的寻址方式。 ② 杂类Load/Store指令的寻址方式

2017-10-18 16:32:14 1

1 / Data TCM.TCM包含在存储器的地址映射空间中,可以作为快速存储器来访问。TCM使用物理地址,对TCM的写访问,受到MMU内部保护信息的控制。向TCM中的内存位置写入时,不会发生任何外部写入。 TCM用于向处理器提供低延迟内存,它没有高速缓存特有的不可预测性。

2018-01-26 12:15:00 2653

2653 CPU和内存都具有相应的速率和带宽。在配置电脑过程中,根据CPU的速率和带宽,来搭配相应速率和带宽的内存,会直接影响整机的性能。如果搭配不当往往会浪费CPU或内存的性能。下面,我们对CPU和内存搭配规律的常识,进行较深入的认识。

2018-07-09 10:33:00 34792

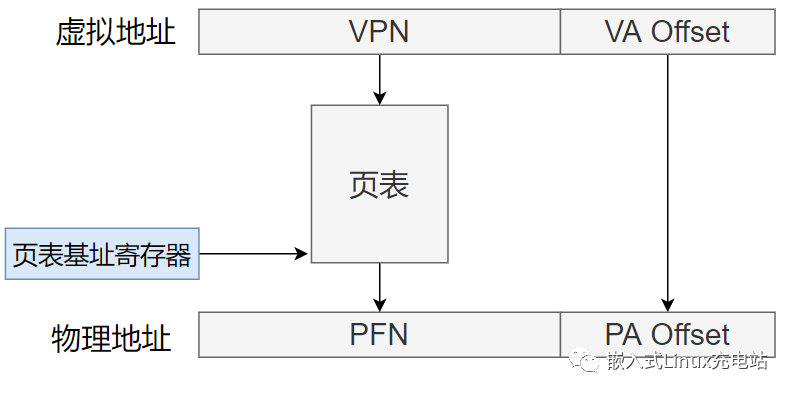

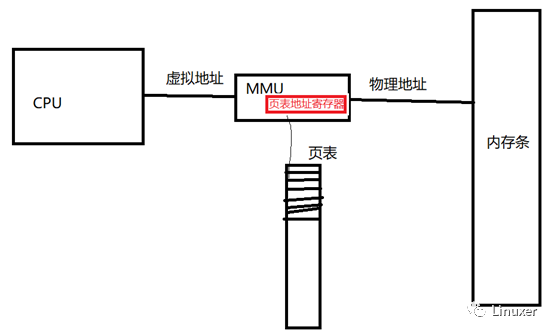

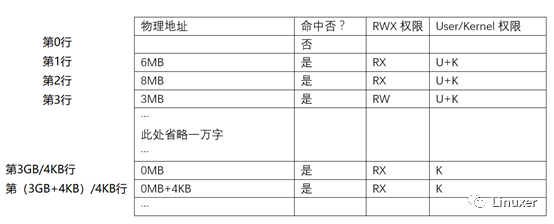

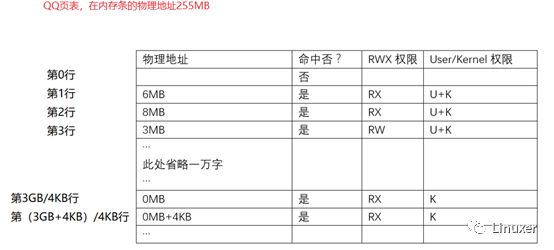

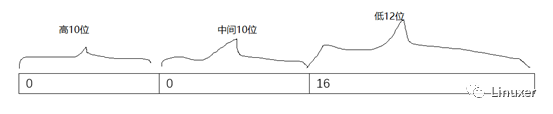

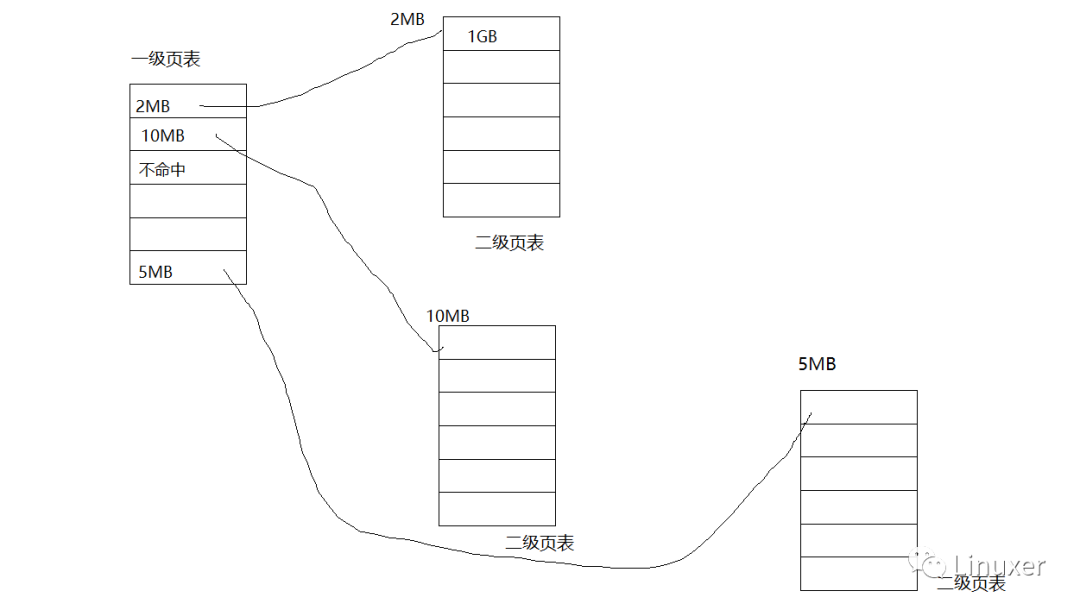

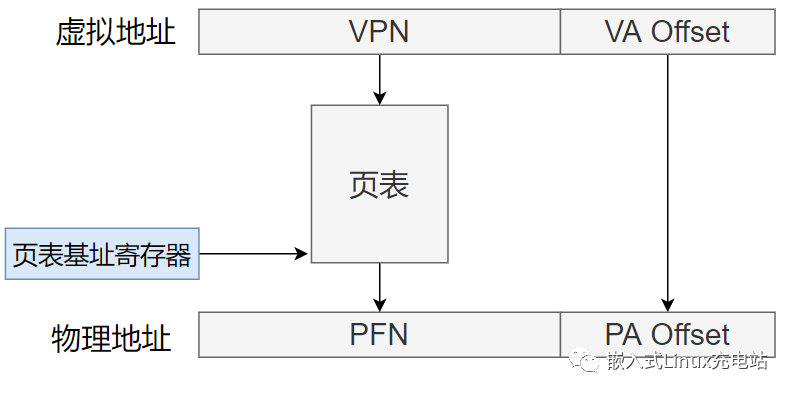

34792 对于一个有MMU的CPU而言,MMU开启后,CPU是这样寻址的:CPU任何时候,一切时候,发出的地址都是虚拟地址,这个虚拟地址发给MMU后,MMU通过页表来在页表里面查出来这个虚拟地址对应的物理地址是什么,从而去访问外面的内存条。MMU里面的页表地址寄存器,记录了页表本身的存放位置。

2018-02-02 14:08:57 11718

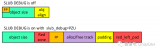

11718

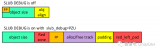

SLAB内存分配器-SLUB的DEBUG功能,如何帮忙检测内存越界(out-of-bounds)和访问已经释放的内存(use-after-free)。

2018-02-08 14:11:22 11068

11068

在没有使用虚拟存储器的机器上,虚拟地址被直接送到内存总线上,使具有相同地址的物理存储器被读写。而在使用了虚拟存储器的情况下,虚拟地址不是被直接送到内存地址总线上,而是送到内存管理单元——MMU(主角终于出现了)。

2018-03-12 09:17:00 4135

4135

对于包含 MMU 的处理器而言, Linux 系统提供了复杂的存储管理系统,使得进程所能访问的内存达到 4GB。进程的 4GB 内存空间被分为两个部分—用户空间与内核空间。

2019-05-13 11:24:14 950

950

现在是买内存的好时机,有一个问题不知道小伙伴们弄清楚了没,CPU参数、主板设置里都有内存频率,CPU是固定的,而主板经常有一堆频率可选。这就有个麻烦了,选内存的频率应该跟着CPU参数走,还是跟着主板

2020-09-09 11:41:12 9020

9020 本文从内存管理的发展历程角度层层递进,介绍 MMU 的诞生背景,工作机制。而忽略了具体处理器的具体实现细节,将 MMU 的工作原理从概念上比较清晰的梳理了一遍。 MMU 诞生之前:在传统的批处理

2020-12-17 16:13:56 14281

14281

CPU通过地址来访问内存中的单元,地址有虚拟地址和物理地址之分,如果CPU没有MMU(Memory Management Unit,内存管理单元),或者有MMU但没有启用,CPU核在取指令或访问内存

2021-03-28 11:05:03 14

14 设置访问等级和密码后,需输入密码才能访问功能和存储区。将在 CPU 的对象属性中指定各种访问级别及其关联的密码。

2021-04-12 14:36:24 5403

5403

电子发烧友网为你提供CPU是怎样访问内存的?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-23 08:40:23 11

11 一、MMU vs MPU内存是现代计算机最重要的组件之一。因此,它的内容不能被任何错误的应用所篡改。这个功能可以通过MMU(Memory Management Unit)或者MPU(Memory

2021-10-26 16:36:23 4

4 在一些桌面程序中,整个内存映射是通过虚拟内存来进行管理的,使用一种称为内存管理单元(MMU)的硬件结构来将程序的内存映射到物理RAM。在对于 RAM 紧缺的嵌入式系统中,是缺少 MMU 内存管理单元的。

2022-02-09 10:41:12 4

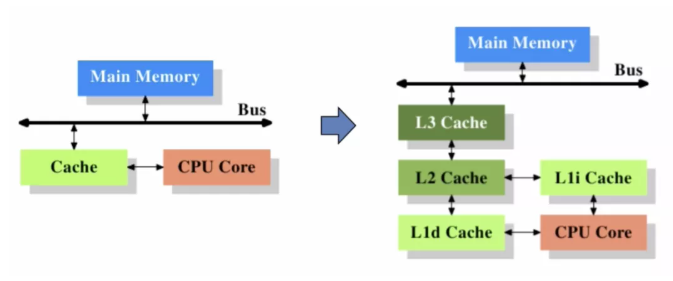

4 CPU没有存储功能,那么缓存到底是干什么的?CPU缓存是用于减少处理器访问内存所需平均时间的部件,作用类似于CPU内部的内存。

2022-03-30 10:58:36 5292

5292

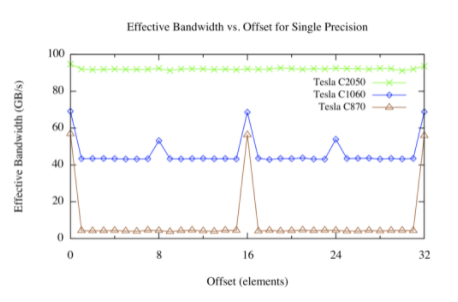

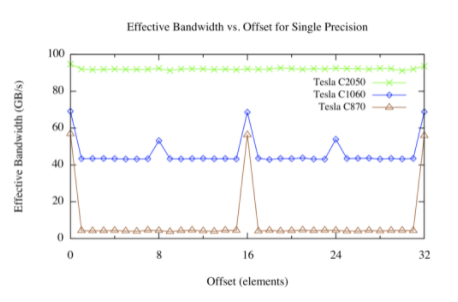

当访问多维数组时,线程通常需要索引数组的更高维,因此快速访问是不可避免的。我们可以使用一种名为 共享内存 的 CUDA 内存来处理这些情况。共享内存是一个线程块中所有线程共享的片上内存。共享内存的一

2022-04-11 10:07:41 1724

1724

工控机的CPU的运算速度比主内存的读写速度要快得多,这就使得工控机的CPU在访问内存时要花很长时间来等待内存的操作,这种空等造成了系统整体性能的下降。 为了解决这种速度上的不匹配问题,我们在CPU

2022-05-09 16:29:32 2381

2381 本文讲解Linux内核虚拟内存管理中的mmu_gather操作,看看它是如何保证刷tlb和释放物理页的顺序的,又是如何将更多的页面聚集起来统一释放的。

2022-05-20 14:37:53 2765

2765 检查,使得系统更加安全。通过虚拟内存访问物理内存,每次都需要解析页表,这大大降低了内存访问的性能,为此CPU的MMU里面加入了TLB用来缓存页表解析的结果,这样由于程序的时间局部性和空间局部性,能极大的提高内存访问的速度。虽然和直接访问物理内存相比,仍然存在着一些性能损耗,但是损耗已经

2022-06-01 16:02:40 3110

3110 一般MMU会有一种disable的模式,即不使能MMU,所有虚拟地址都直接映射到相应的物理地址,VA=PA。

2022-07-28 18:09:42 5785

5785

绝对标识符指示CPU中的内存区域。通过指定地址标识符(此处为IB)后面跟一个地址(此处为10)来指定内存区域。

2022-08-02 15:36:28 1190

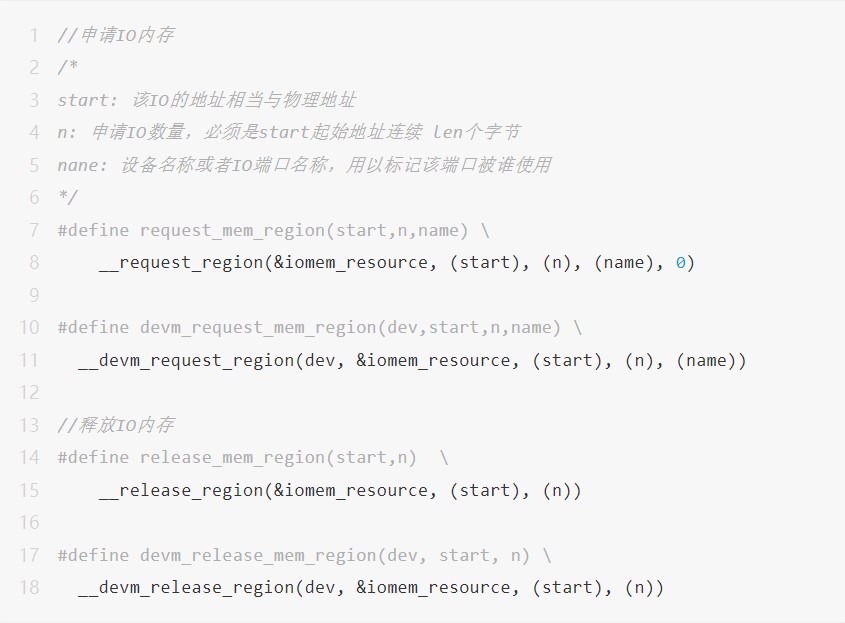

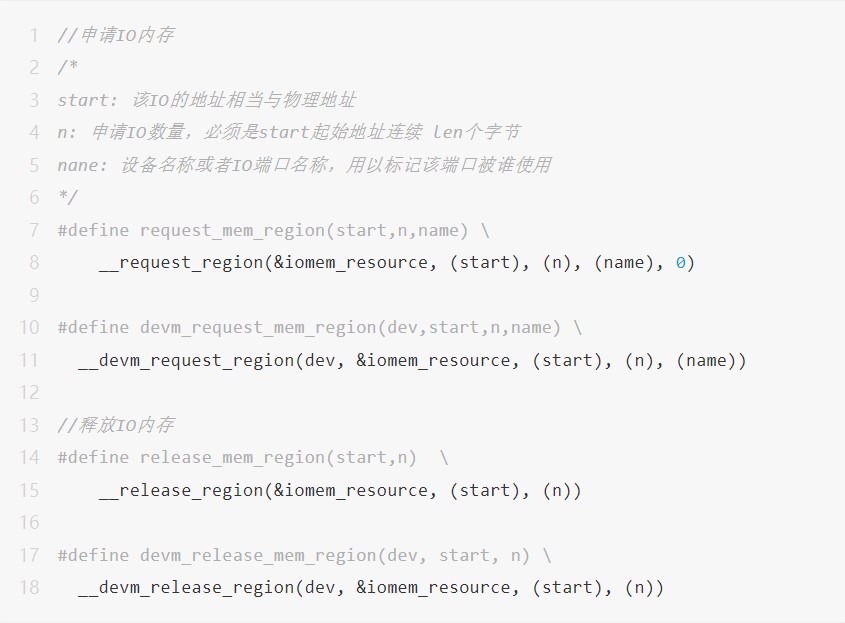

1190 在内核中访问IO内存(通常是芯片内部的各个I2C,SPI, USB等控制器的寄存器或者外部内存总线上的设备)之前,需首先使用ioremap()函数将设备所处的物理地址映射到虚拟地址上。

2022-08-04 18:10:52 2387

2387

通过上面的各个小节我们可以看到,现代的服务器里,CPU和内存条都有多个,它们之前目前主要采用的是复杂的NUMA架构进行互联,NUMA把服务器里的CPU和内存分组划分成了不同的node。

2022-08-30 17:03:19 3464

3464

设置访问等级和密码后,需输入密码才能访问功能和存储区。将在 CPU 的对象属性中指定各种访问级别及其关联的密码。

2022-09-14 16:08:27 4322

4322 CPU 提供了四个访问级别,用于限制对特定功能的访问。

2022-12-28 09:09:08 3553

3553 MMU(Memory Management Unit,内存管理单元)是一种硬件模块,用于在CPU和内存之间实现虚拟内存管理。

2023-04-23 10:48:05 1342

1342

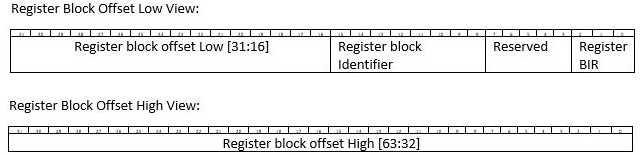

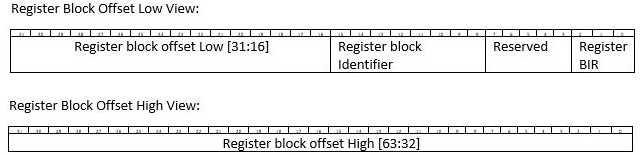

计算快速链接 (CXL) 1.1 和 CXL 2.0 规范在内存映射寄存器的放置和访问方式上有所不同。CXL 1.1 规范将内存映射寄存器放置在 RCRB(根复合寄存器块)中,而 CXL 2.0

2023-05-25 16:56:20 3450

3450

MMU(Memory Management Unit,内存管理单元)是一种硬件模块,用于在CPU和内存之间实现虚拟内存管理。

2023-08-03 10:03:42 4227

4227

MMU怎么知道这个页表在内存中的具体地址呢? 通常CPU会提供一个页表基址寄存器给操作系统使用,用于给MMU指示页表的基地址。不同处理器架构对应的寄存器也不一样: x86:CR3(Control

2023-10-08 11:52:29 2430

2430

在内存管理方面,MMU可以通过页面表(Page Table)实现虚拟内存管理。页面表是一种数据结构,记录了每个虚拟页面和其对应的物理页面之间的映射关系。

2023-10-09 11:27:33 2561

2561

虚拟内存功能和保护机制的重要角色。 MMU(Memory Management Unit)是一种硬件机制,它为CPU提供了一种虚拟内存映射的功能,可以将物理地址映射到虚拟地址上。在实际应用中,使用MMU可以实现以下几个功能: 1.虚拟内存管理 MMU可以将虚拟地址映射到物理地址上,这样程序可以

2023-10-29 16:28:35 1494

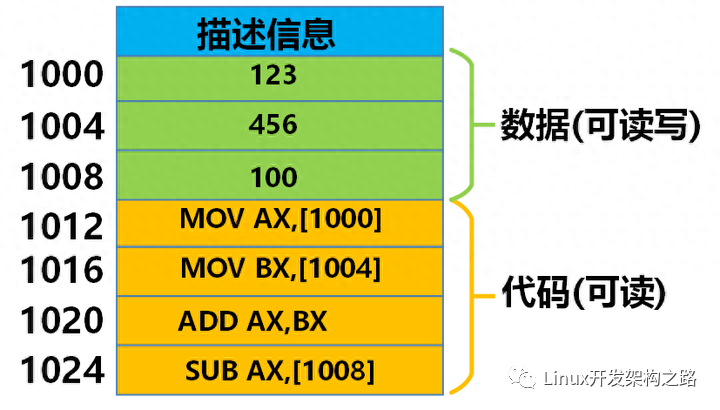

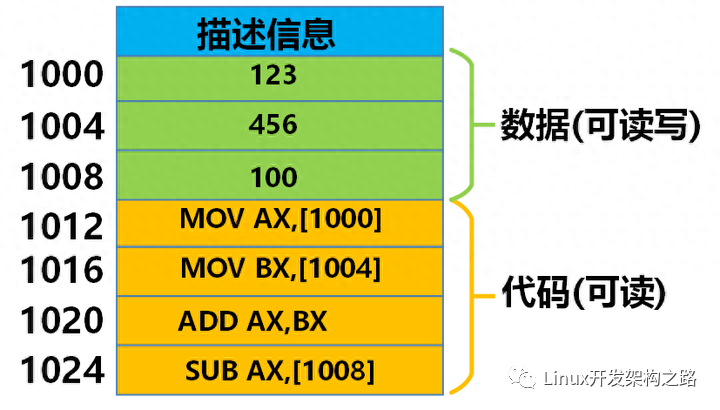

1494 程序经过编译后,变成了可执行的文件,可执行文件主要包括代码和数据两部分,代码是只读的,数据则是可读可写的。 可执行文件由操作系统加载到内存中,交由CPU去执行,现在问题来了,CPU怎么去访问代码和数

2023-11-08 17:04:37 1687

1687

(Memory Management Unit,内存管理单元)是一种硬件模块,用于在CPU和内存之间实现虚拟内存管理。 其主要功能是将虚拟地址转换为物理地址,同时提供访问权限的控制和缓存管理等功能。 放在整个大系统多核架构里面,每个处理器内置了MMU模块,MMU模块包含了TLB和TWU两个

2023-11-26 15:21:34 1205

1205

访问权限控制 TrustZone技术之所以能提高系统的安全性,是因为对外部资源和内存资源的硬件隔离。这些硬件隔离包括中断隔离、片上RAM和ROM的隔离、片外RAM和ROM的隔离、外围设备的硬件隔离

2023-11-26 15:47:57 1238

1238

1-MMU相关的基本概念 (1)虚拟地址相关基本概念 • 虚拟内存(Virtual Memory,VM):为每个进程提供了一致的、连续的、私有的内存空间,简化了内存管理。将主存看成是一个存储在磁盘

2023-11-26 16:11:43 1351

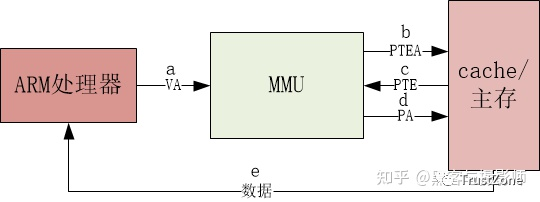

1351 页命中、缺页 (1)页命中 • a) 处理器要对虚拟地址VA进行访问。 • b) MMU的TLB没有命中,通过TWU遍历主存页表中的PTEA(PTE地址)。 • c) 主存向MMU返回PTE

2023-11-26 16:19:27 2033

2033

ug内部错误,内存访问违例怎么解决 内部错误和内存访问违例是编程中常见的问题,它们可能会导致应用程序崩溃、数据丢失或系统不稳定。在本文中,我将详细解释内部错误和内存访问违例的原因,如何解决这些

2023-12-27 16:27:13 10468

10468 CPU缓存(Cache Memory)是计算机系统中一个至关重要的组成部分,它位于CPU与内存之间,作为两者之间的临时存储器。CPU缓存的主要作用是减少CPU访问内存所需的时间,从而提高系统的整体性能。以下将详细阐述CPU缓存的定义、类型、工作原理及其作用。

2024-08-22 14:54:59 8453

8453 当你遇到主板自检时CPU和内存灯一直来回闪烁的情况,这通常意味着硬件检测过程中存在问题。这个问题可能涉及到多个方面,包括硬件故障、BIOS设置错误、兼容性问题等。 1. 硬件故障 1.1 CPU故障

2024-09-02 14:38:10 32208

32208 主板内存故障灯亮并不一定是CPU的问题,但CPU与内存之间的交互确实可能影响这一故障现象。以下是对主板内存故障灯亮可能原因的分析: 一、内存本身问题 内存条未正确安装 :内存条可能没有牢固地插入

2024-09-02 14:42:07 10358

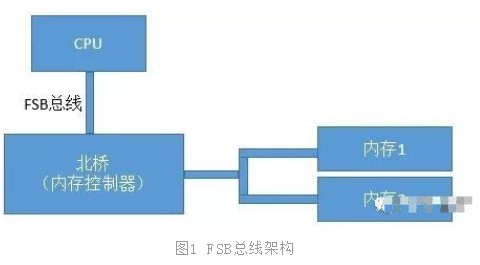

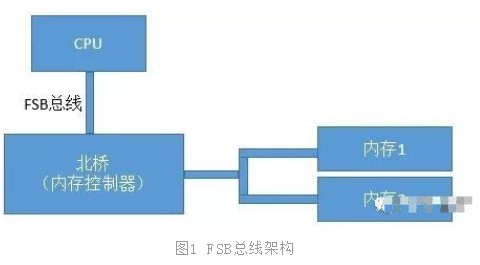

10358 数据传输的芯片,它连接了CPU、内存、以及系统总线。它的主要功能包括: CPU通信 :北桥芯片负责将CPU的数据请求转发到内存或其他系统组件。 内存控制 :它管理内存的访问,包括内存的读写操作和内存的时序控制。 系统总线管理 :北桥芯片还负

2024-10-14 10:37:01 2602

2602

电子发烧友App

电子发烧友App

评论