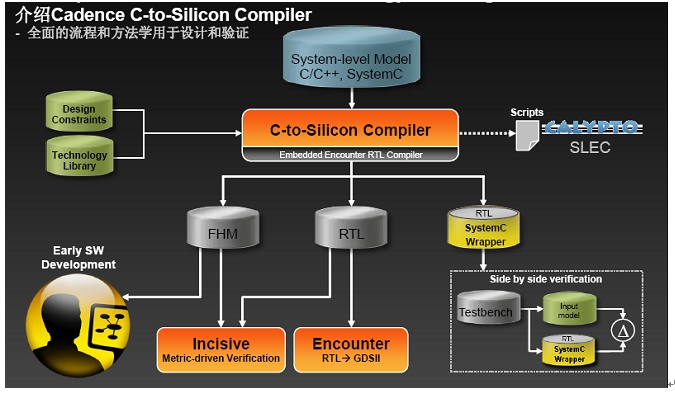

2015 Cadence新技术研讨会Cadence一致探索并研发EDA新技术,以加速设计并提高我们设计品质!2015 Cadence 新产品成员(OLB,OPE,EDM)如何助推我们的设计效率、全新

2015-05-19 10:19:07

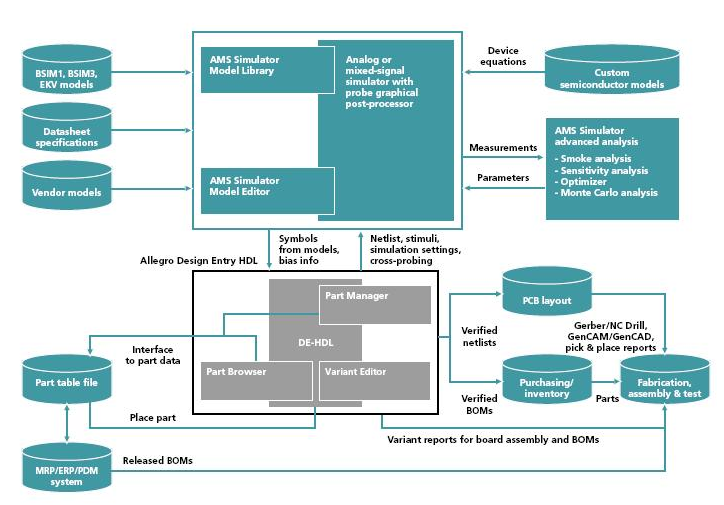

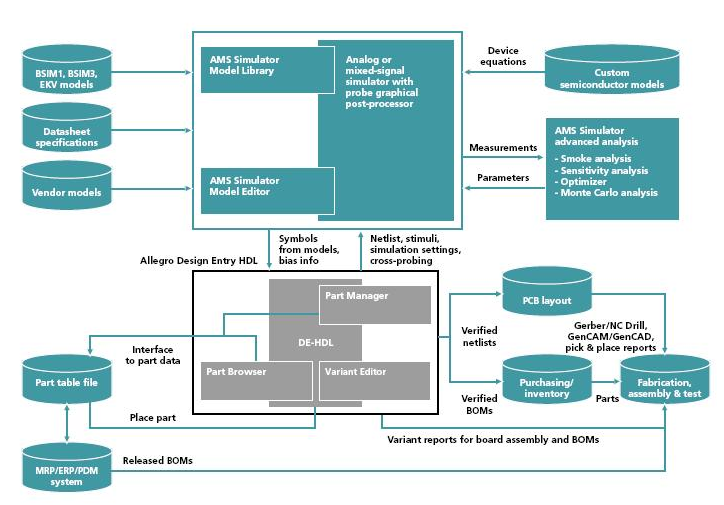

PCB设计、仿真及分析完全统一的集成环境在较大的电路设计系统上,PCB设计团队需要快速、可靠的仿真软件来实现对设计的收敛。Cadence Allegro PSpice System

2020-07-07 09:47:41

上,cadence公司提到: PSpice通过改善模拟集合和平均提高20%模拟速度,从而提高用户的生产率。通过引入多核模拟支持系统,包括大型设计和MOSFETs和BJTs等复杂模型支配的设计,取得了显著

2012-12-18 10:18:07

各位大神,请问下Cadence仿真中电容电阻一些基本元器件的IBIS模型是不是自带的?也就是仿真时会自动提取?需要找的只是一些复杂元器件的IBIS模型?

2015-01-16 21:55:50

本人第一次接触Cadence,对于SPICE也没有什么特别深刻的接触,因此,在这里希望有战友能够帮助我完成份仿真实验。主要是第一和第二个仿真实验,第一个实验的电阻与电容的线性如何设置。同时,在此求LINUX系统下的Candence 安装链接,在此谢谢大佬们!PS:求一个交流群

2016-12-16 14:25:52

正在学习用Cadence仿真LC VCO(SMIC0.18 RF CMOS库)。但是自己研究了好久也不出振荡波形,跟着 实验指导书一步一步去做也不对,各个器件的参数也是按照指导书来的,仿真控件

2021-06-24 06:13:04

Cadence仿真流程Cadence仿真流程[/hide][此贴子已经被作者于2009-8-16 13:47:51编辑过]

2009-08-16 13:47:03

Cadence_高速电路设计与仿真(第三版)

2016-05-12 16:25:25

Cadence高速电路板设计与仿真第3版,分享资料给大家.

2017-02-28 10:45:34

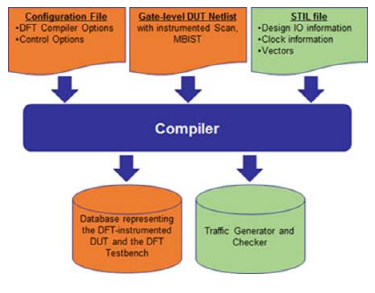

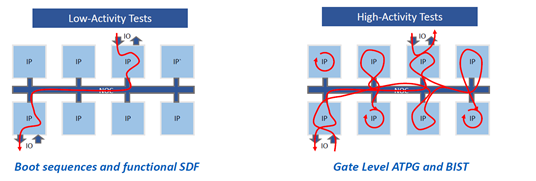

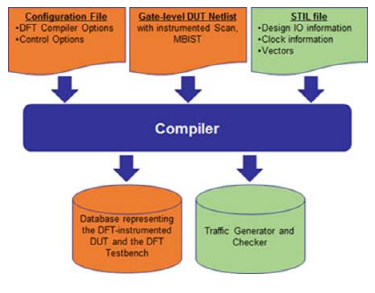

复杂电路的错误仿真更为容易,特别是在错误仿真工具能用于增量和分布模式时。 包含DFT和BIST的业务非常引人注目,今天的SoC设计在测试开发方面所花的时间可能要比实际功能电路开发更多,这样会导致丧失

2011-12-15 09:53:14

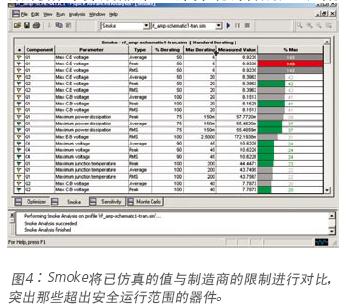

Cadence PCB设计仿真技术Cadence PCB设计仿真技术提供了一个全功能的模拟仿真器,并支持数字元件帮助解决几乎所有的设计挑战,从高频系统到低功耗IC设计,这个强大的仿真引擎可以容易地同

2008-06-12 00:57:27

cadence specctraquest仿真教程.rar

2009-09-08 00:27:17

`cadence初入门哈,求问,下面这张图可以直接跑仿真么?我意思是,,这不是编辑后的简化模块儿么,还能在cadence上直接验证逻辑功能么?`

2014-04-18 03:29:28

DAP仿真器 BURNER

2023-03-28 13:06:20

大家好,我是Richie,今天简单讲一点代码优化方法,用代码的形式设置多核并行,来大大加速数据处理速度。这种方法就像流水线作业,每一个节点都在同时运作,并将结果传送给下一个节点。我写了个小Demo来

2021-02-09 23:56:33

The following is the Job Description of this position-- DFT Engineer. If someone is interested, plz feel

2016-07-15 13:58:30

什么是数字信号处理DFT?貌似有很多DFT啊

2011-12-15 09:39:26

Cadence PCB设计仿真技术提供了一个全功能的模拟仿真器,并支持数字元件帮助解决几乎所有的设计挑战,从高频系统到低功耗IC设计,这个强大的仿真引擎可以容易地同各个Cadence PCB原理图

2019-10-10 23:01:33

请问在cadence中,怎么仿真由反相器构成的振荡器啊!!!非常感谢

2013-04-14 14:58:12

电力系统实时仿真器多基于专用的硬件设备,本文介绍了一种新的基于通用多核工业PC 的仿真器和它的仿真软件StarSim。并行计算是实现实时仿真的关键技术StarSim 通过分布式参数线路进行系统

2014-08-20 13:23:23

基于multisim多核cpu仿真,四片8051,一片进行高八位的输入,一片进行低八位的输入,一片进行高八位的输出,一片进行低八位输出的例子

2019-04-16 14:32:29

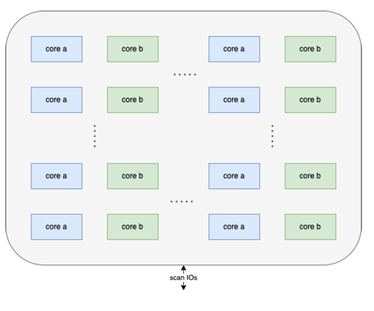

基于扫描的DFT方法扫描设计的基本原理是什么?扫描设计测试的实现过程是怎样的?基于扫描的DFT对芯片测试的影响有哪些?

2021-05-06 09:56:36

请求诸位大神,如何利用cadence仿真

2019-08-18 23:06:31

设计的全差分运放,如何在Cadence中搭建仿真电路去仿真【摆率】【 建立时间】【输入共模范围】【输出摆幅】?还请做过全差分运放的同仁,画个草图传上来,单纯的文字语言显得晦涩难懂,希望大家能指导我,谢过。PS:论坛中搜过的资料,我想能看懂的同仁绝对比我聪明。

2021-06-24 06:39:33

软件版本:Cadence 16.5使用工具:Allegro PCB PI Option XL Power Integrity使用资源:仿真目的:根...

2021-12-31 06:06:15

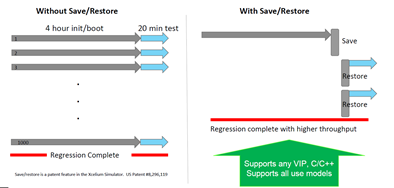

,可能就可以抵消多核带来的收益。 总之,单个服务器内,提供8~10个核做并行处理,是对Xcelium“恰恰好”的一种配置方式。 单双核任务划分 Xcelium并非可以对所有仿真程序进行加速,某些

2023-03-28 11:18:49

如何用Cadence里的spectre仿真谐振回路Q值?

2021-06-24 06:55:44

新手刚接触cadence,最近在学习于博士的视频,老师要求着重学习一下有关cadence的emc仿真分析方面的内容,但是我搜的教程大部分都是原理图,pcb版,SI仿真方面的,请问emc仿真跟SI仿真是同样的么?实在是有点迷茫,如果不是求大家推荐个emc仿真分析的书和教程呗~谢谢各位了!

2015-10-08 09:25:05

自己制作的Matlab DFT习题

2020-10-31 21:13:21

推荐的学习方法是:理解问题域;比较并掌握解决问题的不同方法;熟悉解决问题过程中遇到的各种难题;再通过运用EDA工具解决实际问题来巩固加深之前所学的知识。在了解DFT之前,先让我们简短回顾下整个数字芯片的设计流程

2016-05-25 15:32:58

DFT是什么原理?

2021-06-17 08:54:06

请问cadence 中反射仿真 看波形的时候,一共画出了四条线,分别是U15 138、U15 138i、U27 81和U27 81i,请问那个数字后边的i代表什么意思啊

2013-03-30 10:01:55

请问如何用cadence仿真RF-DC转换电路?

2019-04-18 08:43:48

高速DAP仿真器 BURNER

2023-03-28 13:06:20

Cadence 仿真流程:第一章 在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方

2008-07-12 08:56:05 0

0 cadence仿真教程:第一章 在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方式得到结果: Allegro 的PCB 画板界面,通过处理可以直接得到结

2008-07-12 09:04:58 0

0 Cadence 软件是我们公司统一使用的原理图设计、PCB 设计、高速仿真的EDA 工具。进行仿真工作需要有很多方面的知识,须对高速设计的理论有较全面的认识,并对具体的单板原理

2008-08-05 14:25:21 0

0 时序计算和Cadence 仿真结果的运用中兴通讯康讯研究所 EDA 设计部 余昌盛 刘忠亮摘要:本文通过对源同步时序公式的推导,结合对SPECCTRAQuest 时序仿真方法的分析,推导出了使

2009-12-21 09:05:39 172

172 随着片上多核处理器(CMP1)时代的到来,如何利用多核加速串行程序成为迫切需要解决的问题。本文综述了该领域的主要研究工作,介绍了我们目前在该领域的研究情况,总结了该

2010-01-15 11:07:22 17

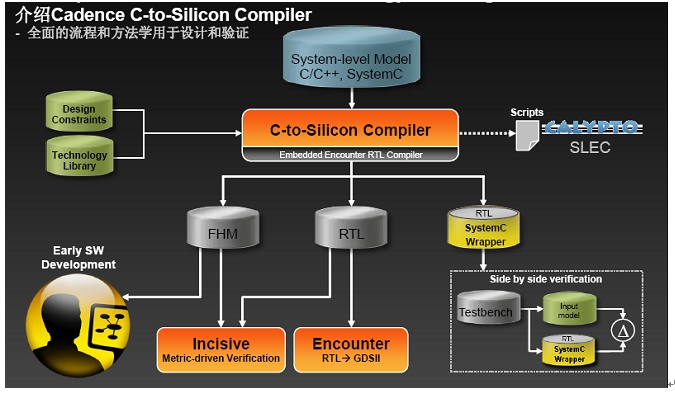

17 Cadence CDNLive:搭建沟通平台,加速设计创新

“工程师是最终决策的源泉。通过设计自动化,让决策者做出的每一个决定不但高效正确,而且充满意义和乐

2008-09-04 10:56:30 750

750

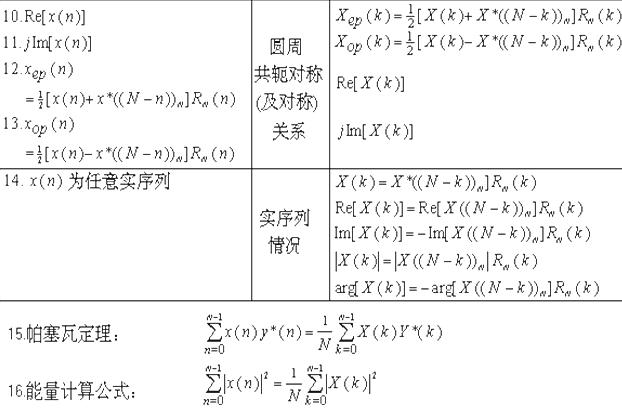

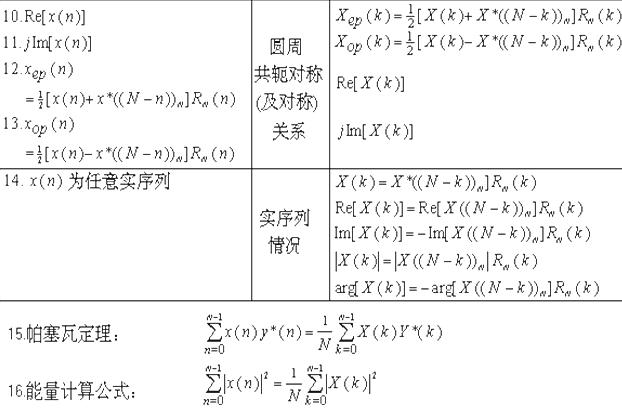

DFT性质一览表

2009-07-25 11:41:03 3998

3998

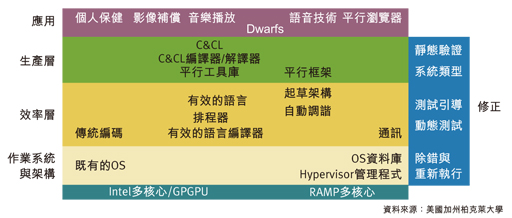

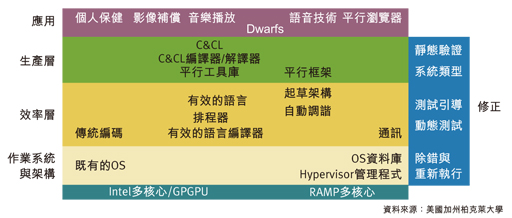

专家观点:并行软件须加速追赶多核处理器发展脚步

为了持续提升性能而又不至于因过热导致故障,微处理器正朝向多核心方向发展。但主流软件至今却尚未能找到使

2009-08-07 07:40:31 334

334

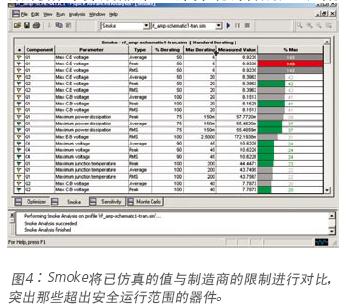

Cadence PCB设计仿真技术

Cadence PCB设计仿真技术提供了一个全功能的模拟仿真器,并支持数字元件帮助解决几乎所有的设计挑战,从高频系统到低功耗I

2010-04-29 08:41:58 4341

4341

DFT:数字电路(fpga/asic)设计入门之可测试设计与可测性分析,离散傅里叶变换,(DFT)Direct Fouriet Transformer

可测试性技术(Design For Testability-

2010-06-07 11:00:48 29875

29875 提出了一种基于simPlescaL比和Systemc的异构异步多核 仿真器 ,不同运行频率的内核之间采用共享存储区实现通信及数据共享。实验结果表明该仿真器能够在时钟周期级正确模拟异构多核处

2011-07-22 15:24:25 18

18 均衡技术是在接收端消除无线多径衰落信道引起的码间干扰的重要手段。介绍了一种利用单点DFT运算进行均衡的算法,讨论了在对该算法进行定点仿真中遇到的几个问题,最后给出了浮

2011-09-16 14:36:28 0

0 通过Cadence软件建立DDRⅡ信号拓扑结构、仿真信号的串扰、码间干扰、过冲等与信号质量相关的参数,从仿真波形中可以测量出与信号时序相关的参数,从而计算出信号的时序裕量,并为DDRⅡ

2012-02-13 15:16:22 52

52 根据源同步的一些基本问题,在Cadence仿真环境下,对源同步时序进行仿真,仿真结果表明,设计能满足噪声容限和过冲,仿真后的可知数据线和时间的延时约为0.3ns,满足源同步系统设

2012-05-29 15:26:26 0

0 本内容介绍了DFT可测试性设计的相关知识,并列举了3中常见的可测性技术供大家学习

2012-05-30 16:42:27 7082

7082 Cadence 软件是我们公司统一使用的原理图设计、PCB 设计、高速仿真、自动布线的EDA 工具。本篇 Cadence 使用手册是一本基于Allegro SPB V15.2 版本的Cadence 软件的基础使用手册,包括原理图设

2013-09-06 16:12:51 0

0 详细介绍Cadence的仿真流程

有需要的朋友下来看看

2015-12-08 14:49:11 0

0 cadence_specctraquest仿真教程_

2016-02-22 16:04:37 0

0 利用Cadence工具进行板级电路信号完整性仿真

2016-02-22 16:21:13 52

52 Cadence 原理图仿真Pspice工具的使用教程,非常好用。

2016-05-17 11:09:40 0

0 利用Cadence Allegro进行PCB级的信号完整性仿真

2017-01-12 12:18:20 0

0 第3章--离散傅里叶变换(DFT)

2016-12-28 14:23:30 0

0 基于SystemC构建多核DSP软件仿真平台_韦祎

2017-01-03 17:41:32 3

3 CADENCE射频SiP方法学套件加速无线应用设计

2017-01-14 12:50:17 25

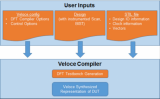

25 2017年3月1日,上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日发布业界首款已通过产品流片的第三代并行仿真平台Xcelium™ 。基于多核并行运算技术,Xcelium

2017-03-01 15:57:05 3341

3341 中国上海,2017年6月19日 – 楷登电子(美国Cadence公司,NASDAQ: CDNS)今日正式发布全新VirtualBridge™适配器。较传统RTL仿真,基于虚拟仿真技术的VirtualBridge™适配器可以加速硅前验证阶段的软件初启。

2017-06-19 16:04:06 4116

4116 出的结果进行阈值去噪处理,并根据循环前缀内、外噪声方差的均值在DFT插值的过程中设置相应门限,然后对循环前缀内的噪声再次处理,以进一步减小噪声的影响。仿真实验结果表明,在复杂度基本不变的前提下,该算法能够较好地减小加性高

2017-11-25 11:50:29 1

1 可测试性设计 (DFT) 在市场上所有的电子设计自动化 (EDA) 工具中是最不被重视的,纵然在设计阶段提高芯片的可测试性将会大幅缩减高昂的测试成本,也是如此。最近的分析数据表明,在制造完成后测试

2017-11-28 11:28:38 0

0 DFT 是一种在设计阶段将可测试性置入集成电路 (IC) 的方法,可以降低测试成本并提高制造良率,多年来以不同方式得到广泛应用。Ad-hoc 和结构化这两种方法能够有效地检测出电路中所有的故障,减少

2017-12-10 11:51:58 1

1 Ad-hoc DFT 包括一套提倡“良好”设计规范的规则,旨在简化和加速测试流程。例如,提供置位和复位信号,使得所有触发器均可初始化;避免引起振荡的异步逻辑反馈;逻辑门设计应注意避免扇入数过大(扇入

2018-04-12 14:29:00 2689

2689

光计算更为节能,可以加速深度学习的训练和推理。Nature Photonics发表的论文,证明了光子电路的强大。据报道百度投资了光学AI芯片初创公司Lightelligence,加速人工智能的工作负载。

2018-02-05 10:46:48 756

756 Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面

2018-02-07 17:11:21 26525

26525

DFT。但由于上市时间方面的压力,芯片在流片前只进行了极少的DFT验证,因此在芯片制造的过程中甚至在其返回到实验室之后,必须继续进行DFT验证。因此,我们需要的是一个硬件加速流程,从而可大幅缩短执行完整验证作业所需的仿真周期。

2018-03-01 11:13:33 1

1 寒武纪云端智能芯片产品MLU100中集成了Cadence Memory interface IP和I/O interface IP,并应用了Cadence Palladium Z1企业级硬件仿真加速平台。

2018-05-08 16:53:28 9829

9829 了解如何使用Vivado中的Cadence IES Simulator在MicroBlaze IPI设计中运行仿真。

我们将演示如何编译仿真库,为IP或整个项目生成仿真脚本,然后运行仿真。

2018-11-23 06:23:00 6174

6174 Cadence PCB设计仿真技术提供了一个全功能的模拟仿真器,并支持数字元件帮助解决几乎所有的设计挑战。

2019-08-29 08:53:29 2064

2064

DFT 可以降低通过问题器件的风险,如果最终在实际应用中才发现器件有缺陷,所产生的成本将远远高于在制造阶段发现的成本。它还能避免剔除无缺陷器件,从而提高良率。插入 DFT 亦能缩短与测试开发相关的时间,并减少测试装配好的芯片所需的时间。

2019-09-16 14:31:51 1648

1648

全新Helium Virtual和Hybrid Studio是Cadence验证全流程的组成部分,该流程包括Palladium Z2硬件仿真加速平台、Protium X2原型验证平台、Xcelium仿真平台、JasperGold® 形式化验证平台以及vManager™ 验证管理平台。

2021-09-23 14:30:30 1775

1775 https://blog.csdn.net/wu20093346/article/details/38025197软件版本:Cadence 16.5使用工具:Allegro PCB PI

2022-01-11 10:39:16 8

8 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,SK hynix Inc. 已部署 Cadence® Spectre® FX Simulator 仿真器,用于对其面向 PC 和移动应用的 DDR4 和 DDR5 DRAM 进行基于 FastSPICE 的功能验证。

2022-04-08 14:49:00 1565

1565 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Xcelium Apps,该系列技术基于 Cadence® Xcelium™ Logic Simulator 内核原生实现,可为汽车电子、移动设备和超算系统等特定领域设计团队带来最强的验证性能提升。

2022-06-30 10:27:52 1858

1858 在本篇白皮书中,我们介绍了一个典型设计的 DFT 组件,并提出了多种可大幅改善 DFT 项目进度的智能 DFT 方法。我们展示了如何将结构化 DFT 和即插即用原则用于 DFT 基础结构,来支持与其他设计开发工作相似的并行 DFT 开发和集成。

2022-11-30 10:15:00 575

575 SoC 设计的复杂性呈指数级增长且上市时间不断缩短,因此仿真器的性能至关重要。Cadence Xcelium 是高性能仿真器的领导者,我们不懈地专注于提高仿真器的核心性能,并不断开发新的性能优化

2023-01-11 13:47:10 460

460 DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。

2023-03-06 14:47:07 1371

1371 DFT是确保芯片在制造过程中具有可测试性的一种技术。DFT友好的ECO是指在进行ECO时, 不会破坏芯片的DFT功能或降低DFT覆盖率的设计方法。DFT不友好的ECO会对芯片的测试和调试带来很大的困难,可能导致芯片测试效率降低甚至无法测试。

2023-05-05 15:06:37 1262

1262

在刚刚闭幕不久的 CadenceLIVE China 2023 中国用户大会中 , Cadence 全球副总裁、多物理场仿真事业部总经理顾鑫先生 为与会来宾带来题为 《加速多物理场系统仿真》 的精彩

2023-09-04 17:10:05 477

477

fft和dft的区别联系 快速傅里叶变换(FFT)和离散傅里叶变换(DFT)是信号处理和数学计算领域中最常见的技术之一。它们都是用于将离散信号从时域转换到频域的方法,而在此转换过程中,它们都利用

2023-09-07 16:43:53 3139

3139 在刚刚闭幕不久的CadenceLIVEChina2023中国用户大会中,Cadence全球副总裁、多物理场仿真事业部总经理顾鑫先生为与会来宾带来题为《加速多物理场系统仿真》的精彩演讲,分享公司

2023-09-09 08:14:50 943

943

双方的共同客户可获取 Cadence 的全流程系统级设计验证和实现解决方案以及接口 IP,依托 Neoverse CSS 加速开发基于 Arm 的定制 SoC 中国上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

Cadence仿真步骤

2022-12-30 09:19:47 13

13 Cadence混合信号仿真教程

2022-12-30 09:19:49 7

7 Cadence高速电路板设计与仿真(原理图与PCB设计)

2022-12-30 09:19:51 82

82 Cadence高速电路板设计与仿真(第2版)

2022-12-30 09:19:52 2

2 Cadence高速电路板设计与仿真(第3版)

2022-12-30 09:19:52 2

2 CADENCE高速电路板设计与仿真(第4版)

2022-12-30 09:19:53 56

56 Cadence高速电路板设计与仿真

2022-12-30 09:19:53 19

19 如何加速HBM仿真迭代优化?

2023-11-29 16:13:18 189

189

DFT全称为Design for Test,可测性设计。就是说我们设计好一个芯片后,在仿真时可能99%的用例都通过了,怎么保证流片出来的实际芯片也能正常工作呢?

2023-12-06 15:02:43 405

405 多物理场系统设计和分析的先进工具。该平台率先在业界提供了硬件/软件(HW/SW)加速的数字孪生解决方案,旨在提高性能和能效比,加速高保真计算流体力学(CFD)仿真。

2024-02-03 11:31:11 553

553 近日,楷登电子(Cadence)宣布与BETA CAE Systems International AG达成收购协议。BETA CAE作为全球领先的多领域工程仿真解决方案供应商,其卓越的系统分析平台将助力Cadence加速推进智能系统设计战略。

2024-03-08 13:44:38 146

146

电子发烧友App

电子发烧友App

评论