在微波应用的初期,二次世界大战期间,阻抗的选择完全依赖于使用的需要,没有一个标准值。随着技术的进步,需要给出阻抗标准,以便在经济性和方便性上取得平衡。

2022-04-01 14:43:37 4661

4661 相信大家在接触高速PCB设计的时候都会了解到阻抗的一个概念,那么我们在高速PCB设计是为什么需要控阻抗呢,哪些信号需要控阻抗以及不控阻抗对我们的电路有什么影响呢?

2022-10-18 09:09:22 2947

2947 PCB设计比较棘手的问题之一,就是PCB阻抗无法连续的问题。那么遇到问题不要慌张,对于新手该如何应对这个问题,跟着小编一起借鉴一下。 RF信号线如果走直角,拐角处的有效线宽会增大,阻抗不连续

2020-10-30 08:49:37

传输过程中的质量且实现最佳的信号传输效果。 PCB上常用50Ω阻抗主要有以下6个原因: 1. 信号传输的一致性:50Ω阻抗可以匹配常用高速信号传输线材料的特性阻抗,并且可以保证信号在整个传输线上具有

2023-04-14 16:41:14

,不久以后,在象Hewlett-Packard这样在业界占统治地位的公司的影响下,欧洲人也被迫改变了,所以50欧姆最终成为业界的一个标准沿袭下来,也就变成约定俗成了,而和各种线缆连接的PCB,为了阻抗的匹配,最终也是按照50欧姆阻抗标准来要求了。

2019-06-04 07:51:57

,所以折中采用50Ω阻抗是当时最优的选择。三、50Ω容易进行阻抗匹配PCB设计中,经常需要进行阻抗匹配,以减少信号反射和干扰。设计PCB走线时,一般我们会对自己要进行设计的项目进行叠层,根据厚度、基材

2023-04-11 10:32:34

不要超过21MIL(厚的PP介质加工困难,一般会增加一个芯板导致实际叠层数量的增加从而额外增加加工成本)。4、PCB外层(Top、Bottom层)一般选用0.5OZ厚度铜箔、内层一般选用1OZ厚度铜箔

2017-03-01 10:02:08

PCB布线时,阻抗50欧姆,是自己设计好,还是直接给PCB厂做?

2021-05-27 16:17:07

确保PCB成品能达到设计者要求的阻抗值。 6、在高速PCB设计时,设计者应该从那些方面去考虑EMC、EMI的规则呢?一般EMI/EMC设计时需要同时考虑辐射(radiated)与传导(conducted)两个方面. 前者归属于频率较高的部分(>30MHz)后者则是较低频的部分(

2018-08-07 21:55:35

PCB设计中为什么特性阻抗线只有50欧姆和100欧姆两个值?并且那些走线需要特性阻抗控制?特性阻抗线有那些特殊要求

2011-11-28 23:06:00

大家都知道阻抗要连续,但是,正如罗永浩所说“人生总有几次踩到大便的时候”,PCB设计也总有阻抗不能连续的时候。怎么办? 特性阻抗:又称“特征阻抗”,它不是直流电阻,属于长线传输中的概念。在高频

2018-11-27 09:56:09

PCB设计中叠层算阻抗时需注意哪些事项?

2019-05-16 11:06:01

阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号,PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号

2019-02-14 14:50:45

阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度成反比。在嵌入式系统中,一般频率大于20M的信号且PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2014-07-04 14:00:27

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于 20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2018-11-15 20:07:35

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于 20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2019-01-02 10:30:00

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于 20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2022-05-16 16:15:03

大,一般来说,要保证:R>3W。如图右所示。 【3】大焊盘 当50欧细微带线上有大焊盘时,大焊盘相当于分布电容,破坏了微带线的特性阻抗连续性。可以同时采取两种方法改善:首先将微带线介质

2018-09-20 10:34:51

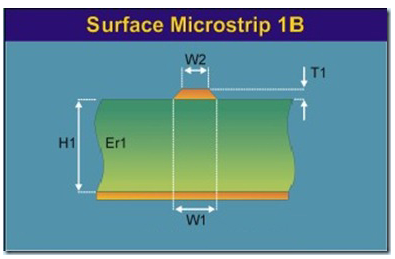

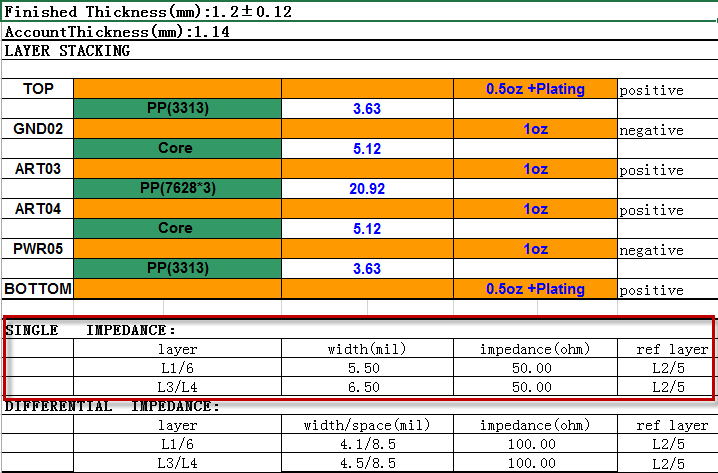

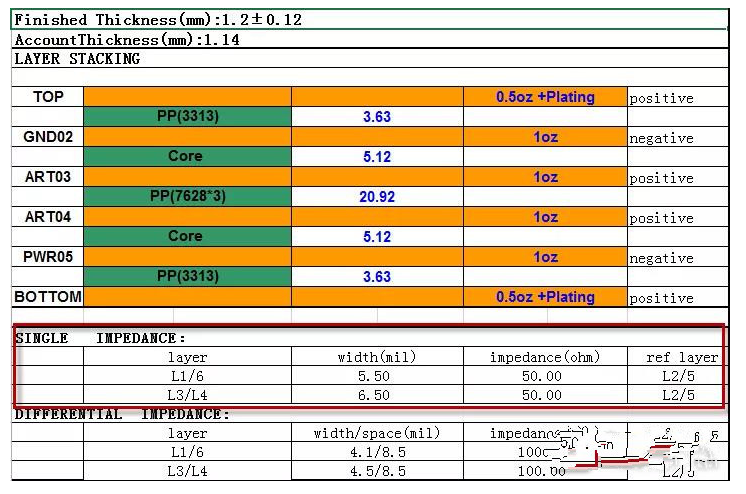

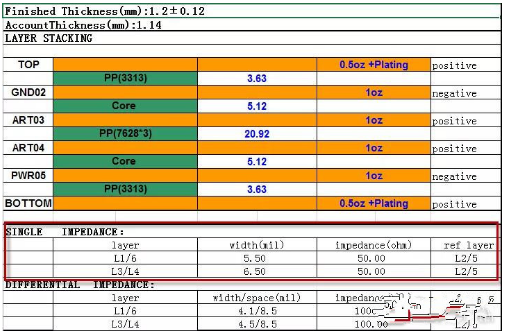

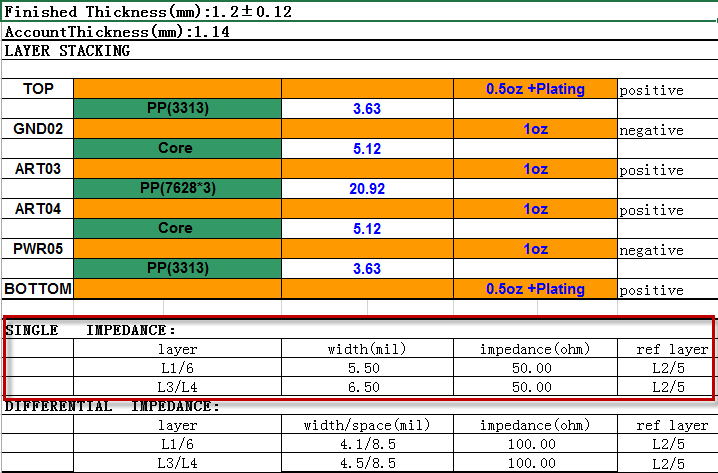

`做PCB设计过程中,在走线之前,一般我们会对自己要进行设计的项目进行叠层,根据厚度、基材、层数等信息进行计算阻抗,计算完后一般可得到如下图示内容。图1 叠层信息图示从上图可以看出,设计上面的单端

2019-12-10 11:34:27

PCB上,尽量减少和缩短各元器件之间的引线和连接。 3、在高频下工作的电路,要考虑元器件之间的分布参数。一般电路应尽可能使元器件并行排列,这样不但美观,而且装旱容易,易于批量生产。 PCB设计具体

2018-09-17 17:36:11

PCB上,尽量减少和缩短各元器件之间的引线和连接。 3、在高频下工作的电路,要考虑元器件之间的分布参数。一般电路应尽可能使元器件并行排列,这样不但美观,而且装旱容易,易于批量生产。 PCB设计具体

2018-09-17 17:38:21

块PCB上,但一般都分成射频电路区和数字电路区,分别布局布线。之间用接地过孔带和屏蔽盒屏蔽。 关于输入、输出端接的方式与规则 问:现代高速PCB设计中,为了保证信号的完整性,常常需要对器件的输入或

2012-07-21 14:42:35

本帖最后由 kinsingm 于 2013-9-1 09:49 编辑

PCB设计的一般原则

2013-09-01 09:46:24

PCB设计的一般原则是什么?

2021-04-26 06:36:11

PCB设计中是使用贴片磁珠还是使用贴片电感主要取决于应用场景。如:在谐振电路中需要使用贴片电感;在消除不需要的EMI噪声时,使用贴片磁珠则是最佳的选择。1、磁珠的单位是欧姆,而不是亨特,这一点要

2018-04-12 10:22:46

中,首先必须先了解需要控制什么样的阻抗。 业界默认的阻抗有单线50Ω、差分线100Ω,还有一些比较特殊的阻抗控制。 USB2.0差分阻抗控制90Ω,而USB3.0为3对差分线,接收和发送都是控制

2023-04-12 15:12:13

如何理解PCB设计中传输线阻抗匹配问题,以及传输线阻抗不匹配所引起的问题?求解,谢谢

2016-04-13 17:13:56

欧姆阻抗。 3、表面处理 PCB 板表面处理一般分为几种,为了更好的了解自己的PCB设计各项问题,现进行简单介绍: 1)喷锡,喷锡是电路板行内最常见的表面处理工艺,它具有良好的可焊接性,可用

2023-04-18 14:36:06

工程师们在布局上花费的时间和精力也很多,预布局—前仿真—再布局—优化,这些过程大概占整个项目设计时间的50%,甚至更多。 下面就总结一个大致的布局步骤及规则,仅供参考。 实际电路设计中还要考虑很多其他

2019-09-12 14:47:17

一般AD芯片数字口的输出阻抗是多少,比如高电平输出下输出阻抗值和低电平输出下的输出阻抗值,是集中在20几欧姆么。芯片手册上也没有提供相关的信息。

2023-12-19 07:10:38

AD14软件在哪里设计50欧姆阻抗布线?

2021-05-28 09:37:52

线圈的阻抗转换到源短均为50 X 4= 200欧姆,两个转化后的组织经过并联后即为100欧姆啊? 麻烦帮我拨正一下思路.

2018-11-01 09:23:55

TI的工程师们,你们好,我最近画了一般CC3100的PCB,参照的是CC3100 BoosterPack画得PCB,天线用的是同样的陶瓷天线,我现在有个疑问,因为陶瓷天线两端都是接的GND,所以在我这PCB中,接地的那段GND线(蓝色标准的部分),需要做50欧姆的阻抗匹配么?

2018-06-24 04:59:21

我之前设计过X86架构的板子,上面涉及RGB信号的阻抗都是在chipset端按照37.5欧姆,经过75Ω的对地电阻之后走线按照50Ω。但是对于ARM系统,设计参考书上没有提到这点,是不是都按照50

2014-11-23 17:24:33

cadence pcb设计各层阻抗都是怎么定的呢?为什么每层显示的阻抗都不一样?

2016-01-25 22:55:40

了吧!”“什么??一米长“阻抗”为50欧姆的微波电缆要500rmb??你在逗我吗?”……没错,射频单盘中的信号走线大多是“特性阻抗”为50欧姆的微带线;一根一米长,可以传输最高频率为20GHZ信号的50

2019-05-18 10:07:18

设计PCB布线设计是整个PCB设计中工作量最大的工序,直接影响着PCB板的性能好坏。在PCB的设计过程中,布线一般有三种境界:首先是布通,这是PCB设计的最基本的入门要求;其次是电气性能的满足,这是衡量一

2017-02-22 14:49:02

20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于 20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据和地址总线信号等

2018-11-19 13:39:51

欧姆作为同轴电缆最优值。这证明了在50欧姆附近,L是最小的。最后,从电气性能的角度看,50欧姆的优势也是综合考虑之后的折中。单纯从PCB走线的性能来说,阻抗低比较好,对一个给定线宽的传输线,和平面距离

2019-08-07 09:59:20

证明了在50欧姆附近,L是最小的。最后,从电气性能的角度看,50欧姆的优势也是综合考虑之后的折中。单纯从PCB走线的性能来说,阻抗低比较好,对一个给定线宽的传输线,和平面距离越近,相应的EMI会减小,串扰

2019-05-30 08:13:09

匹配不良的后果 由于高频讯号的“特性阻抗”(Z0)原词甚长,故一般均简称之为“阻抗”。读者千万要小心,此与低频AC交流电(60Hz)其电线(并非传输线)中,所出现的阻抗值(Z)并不完全相同。数位系统当

2019-05-31 06:45:06

(厚的PP介质加工困难,一般会增加一个芯板导致实际叠层数量的增加从而额外增加加工成本)4、PCB外层(Top、Bottom层)一般选用0.5OZ厚度铜箔、内层一般选用1OZ厚度铜箔说明:一般根据电流

2017-01-16 11:40:35

RF 射频PCB走线为什么要50Ω阻抗,还有为什么要设禁止铺铜,哪些地方要设禁止铺铜???

2013-10-17 00:28:03

多层PCB电路板布局布线的一般原则设计人员在电路板布线过程中需要遵循的一般原则如下: (1)元器件印制走线的间距的设置原则。不同网络之间的间距约束是由电气绝缘、制作工艺和元件 )元器件印制

2018-09-13 16:09:36

RF 信号线如果走直角,拐角处的有效线宽会增大,阻抗不连续,引起信号反射。为了减小不连续性,要对拐角进行处理,有两种方法:切角和圆角。圆弧角的半径应足够大,一般来说,要保证:R>3W。如图

2022-07-02 16:47:33

RF 信号线如果走直角,拐角处的有效线宽会增大,阻抗不连续,引起信号反射。为了减小不连续性,要对拐角进行处理,有两种方法:切角和圆角。圆弧角的半径应足够大,一般来说,要保证:R>3W。如图右所示

2020-11-04 10:54:32

RF 信号线如果走直角,拐角处的有效线宽会增大,阻抗不连续,引起信号反射。为了减小不连续性,要对拐角进行处理,有两种方法:切角和圆角。圆弧角的半径应足够大,一般来说,要保证:R>3W。如图右所示

2022-05-05 11:33:38

(stripline/double stripline),与参考层(电源层或地层)的距离,走线宽度,PCB材质等均会影响走线的特性阻抗值。也就是说要在布线后才能确定阻抗值。一般仿真软件会因线路模型或所

2012-03-03 12:41:55

Hi,大神们,阻抗匹配到50欧姆,是R+jX中的R还是X,还是两个都是的?

2016-11-02 17:24:25

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2019-05-31 08:06:08

电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2011-10-18 14:18:47

连续,引起信号反射。为了减小不连续性,要对拐角进行处理,有两种方法:切角和圆角。圆弧角的半径应足够大,一般来说,要保证:R>3W。如图右所示。03、大焊盘当50欧细微带线上有大焊盘时,大焊盘相当于

2021-02-19 07:00:00

对于晶体管放大电路,比如常用的共射放大电路,一般基极会有两个分压电阻,用来控制给基极一个合适的电平,保证晶体管的基极能导通,这两个分压电阻的阻值一般选用的都是K欧姆级别的阻值,原因是什么? 理论依据是?谢谢!

2020-06-08 17:23:20

模数混合电路电源和接地PCB设计的一般原则如下:● PCB 分区为独立的模拟电路和数字电路部分,采用适当的元器件布局。● 跨分区放置的ADC或者DAC。● 不要对“地平面”进行分割, 在PCB的模拟

2021-12-31 06:41:37

在一般的非高速PCB设计中,我们都是认为电信号在导线上的传播是不需要时间的,就是一根理想的导线,这种情况在低速的情况下是成立的,但是在高速的情况下,我们就不能简单的认为其是一根理想的导线了,电信号

2019-05-30 06:59:24

电路中的200欧姆的作用是什么,是怎么计算出来的?电路中的阻抗匹配该怎么理解,一般在什么电路中会应用到?

2019-01-30 11:06:33

电阻的选定一般是要符合阻抗匹配的。电阻的主要作用是阻抗匹配,所以要清楚输出级的输出阻抗、输入级的输入阻抗,然后用一个电阻或电阻网络去匹配。当然,现在的集成电路阻抗匹配范围很宽,很容易匹配。在高频

2019-07-18 21:05:08

设计电路时一般选多少0欧姆电容才合适?

2021-10-11 09:33:22

。这种情况,你应该用50欧姆,它的线宽更加宽,更易于制造。同轴电缆的阻抗又是怎么样的呢?在RF领域,和PCB中考虑的问题不一样,但是RF工业中同轴电缆也有类似的阻抗范围。根据IEC的出版物(1967年

2016-10-31 16:24:02

阻抗与PCB导线所在的板层、PCB所用的材质(介电常数)、走线宽度、导线与平面的距离等因素有关,与走线长度无关。特征阻抗可以使用软件计算。高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆,这是

2014-12-01 10:38:55

最近在设计pcb的时候,用到了MCX-KWE(50欧姆)天线接口,但有人说要阻抗匹配。大家有谁知道为什么要阻抗匹配吗?如果不阻抗匹配会有什么结果?如果需要阻抗匹配该如何匹配?

2019-06-10 04:36:33

阻抗公差一般为多少?

2019-09-24 02:00:03

打算做一个SIM900A的模块玩玩,原子的我买了,东西做的很不错,就体积感觉有点大,我要做个小的。PCB天线的地方布线需要50欧姆阻抗匹配,怎样能确保做到50欧姆啊,和PCB生产厂家的工艺有很大

2019-03-31 23:59:22

为什么很多PCB传输线的阻抗都是50欧姆?最近搞电路分析,在很多地方看到PCB上的传输线特性阻抗都举例为50欧姆,并且也在很多地方发现该特性阻抗为50欧姆,想问个为什么?为什么不是其他的阻值,30欧姆,100欧姆等等。

2018-11-27 09:33:58

什么样的信号线需要50欧姆阻抗,90欧姆阻抗,100欧姆阻抗,什么信号是单端的??什么样的信号是共面的???什么信号需要包地处理的???

2019-03-19 00:32:53

电压跟随,一般选用什么运放?主要看运放的哪些参数。

2019-05-29 22:05:18

本帖最后由 一只耳朵怪 于 2018-6-6 15:54 编辑

Hi,在参考设计中都只提到不平衡端的阻抗按照50欧姆做PCB微带线,但是平衡端的阻抗设计没有提到,查看

2018-06-06 13:10:24

阻抗匹配阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。在高速PCB设计中,阻抗的匹配与否关系到信号的质量优劣。

2019-05-31 08:12:33

。对于多层一般密度的PCB 设计来说,选用0.25mm/0.51mm/0.91mm(钻孔/ 焊盘/ POWER 隔离区)的过孔较好;对于一些高密度的PCB 也可以使用0.20mm/0.46mm

2016-12-20 15:51:03

在高速pcb设计中,经常听到要求阻抗匹配。而设计中导致阻抗不匹配的原因有哪些呢?一般又对应着怎么的解决方案?欢迎大家来讨论

2014-10-24 13:50:36

挑战。

在高速PCB设计中,阻抗匹配显得尤为重要,为减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。

一般而言,单端信号线的阻抗取决于它的线宽以及与参考平面之间

2023-05-26 11:30:36

PCB设计的磁珠选用技巧,感兴趣的小伙伴们可以瞧一瞧。

2016-10-26 15:55:29 0

0 射频行业里,经常会听到一些说法,这根电缆的特性阻抗是50欧姆,这条微带线的特性阻抗是50欧姆等等。此时很多初学者或者行业外的人就范嘀咕了:

2018-05-05 09:43:00 17215

17215

做pcb设计过程中,在走线之前,一般我们会对自己要进行设计的项目进行叠层,根据厚度、基材、层数等信息进行计算阻抗,计算完后一般可得到如下内容。

2019-03-16 09:04:03 8234

8234

PCB迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB阻抗的范围是 25 至120 欧姆。

2019-08-08 15:23:43 3818

3818

从电气性能的角度看,50欧姆的优势也是综合考虑之后的折中。

2019-10-12 08:36:37 4283

4283

阻抗:在具有电阻、电感和的电路里,对电路中的电流所起的阻碍作用叫做阻抗。

2019-08-28 10:24:12 2728

2728 PCB设计为何一般控制50欧姆阻抗?

2020-01-15 16:17:41 9751

9751 射频行业里,经常会听到一些说法,这根电缆的特性阻抗是50欧姆,这条微带线的特性阻抗是50欧姆等等。此时很多初学者或者行业外的人就范嘀咕了: “什么??导线的“阻抗”有50欧姆?那这根导线的质量也太差了吧!” “什么??一米长“阻抗”为50欧姆的微波电缆要500rmb??你在逗我吗?”

2020-11-23 10:30:00 8

8 高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆。一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为85-100欧姆。

2023-02-17 17:57:54 930

930 在PCB设计中,阻抗通常是指传输线的特性阻抗,这是电磁波在导线中传输时的特性阻抗,与导线的几何形状、介质材料和导线周围环境等因素有关。 对于一般的高速数字信号传输和RF电路,50Ω是一个常用的阻抗

2023-04-06 09:20:03 735

735 在PCB设计中,阻抗通常是指传输线的特性阻抗,这是电磁波在导线中传输时的特性阻抗,与导线的几何形状、介质材料和导线周围环境等因素有关。对于一般的高速数字信号传输和RF电路,50Ω是一个常用的阻抗

2023-04-10 15:21:23 595

595

做PCB设计过程中,在走线之前,一般我们会对自己要进行设计的项目进行叠层,根据厚度、基材、层数等信息进行计算阻抗,计算完后一般可得到如下图示内容。

2023-07-02 14:18:51 664

664

做PCB设计过程中,在走线之前,一般我们会对自己要进行设计的项目进行叠层,根据厚度、基材、层数等信息进行计算阻抗,计算完后一般可得到如下图示内容。 从上图可以看出,设计上面的单端网络一般都是50欧姆

2023-07-03 08:39:40 1138

1138

射频为什么50欧姆 射频阻抗为什么是50欧姆 射频技术在现代通信领域中扮演着极为重要的角色。在射频电路中,50欧姆阻抗是最常见的一种标准阻抗。这个标准阻抗的产生有其历史原因,同时,这个阻抗也有很多

2023-09-02 10:21:05 1668

1668 一站式PCBA智造厂家今天为大家讲讲PCB设计阻抗不连续怎么办?PCB设计阻抗不连续问题的解决方法。大家都知道PCB设计阻抗要连续。但是PCB设计也总有阻抗不能连续的时候。怎么办?下面深圳PCBA

2023-09-22 09:32:05 634

634

pcb设计一般流程步骤

2023-12-13 17:30:30 1333

1333 中,我将详细介绍如何在PCB设计中实现50欧姆匹配。 首先,要了解50欧姆匹配的原理和意义。50欧姆匹配是基于传输线理论的。传输线是一种能将信号从一个点传输到另一个点的电气线路。在传输线理论中,传输线被视为具有特定阻抗的无限长线路。 50欧姆匹配的重要性在于它能够将信号

2023-12-15 14:33:43 1426

1426 在微波应用的初期,二次世界大战期间,阻抗的选择完全依赖于使用的需要,没有一个标准值。随着技术的进步,需要给出阻抗标准,以便在经济性和方便性上取得平衡。

2023-12-29 16:19:19 96

96

一站式PCBA智造厂家今天为大家讲讲如何解决pcb设计阻抗不连续的问题?解决PCB设计中的阻抗不连续的方法。当涉及到PCB(Printed Circuit Board)设计时,阻抗一直是一个非常重要

2024-03-21 09:32:59 89

89

电子发烧友App

电子发烧友App

评论