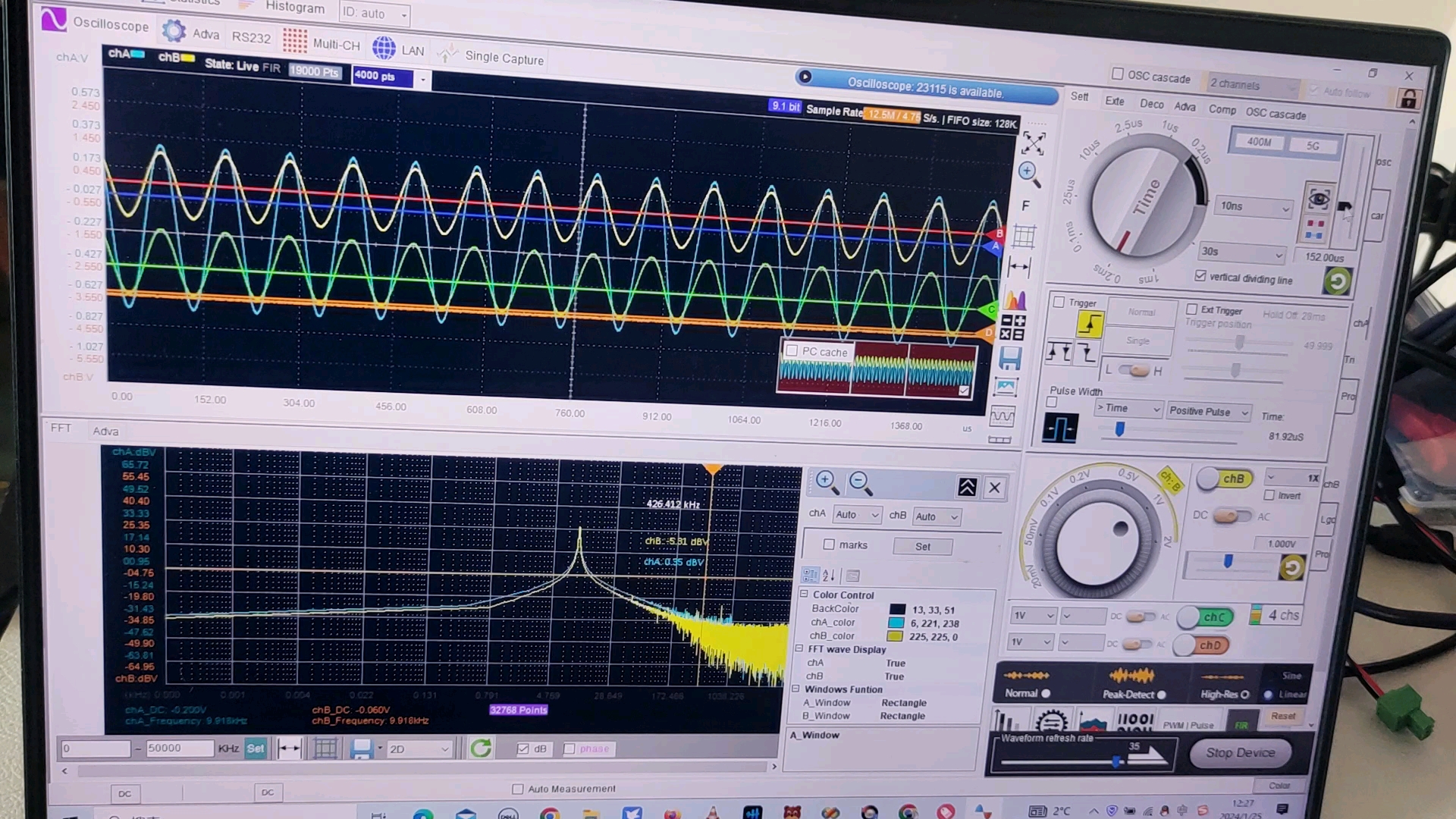

摘要:介绍了基于单片机系统的精密时钟发生电路对高频信号(1MHz~80MHz)进行等效采样的方法,设计并实现一个模拟带宽为1Hz~80MHz的简易数字示波器。

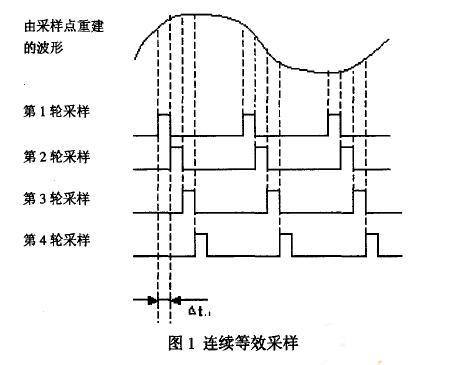

在数字示波器技术中,常用的采样方法有两种:实时采样和等效采样。实时采样通常是等时间间隔的,它的最高采样频率是奈奎斯特极限频率。等效采样(Equivalent Sampling)是指对多个信号周期连续样来复现一个信号波形,采样系统能以扩展的方式复现频率大大超过奈奎斯特极限频率的信号波形。

1 总体设计

由于所设计的示波器输入频率范围较宽, 本系统采用了等效和实时两种采样方式。若输入频率小于1.25MHz,选用实时采样;反之,选用等效采样。根据输入频率确定时钟芯片的输出及分频数。当输入频率高于1kHz时,利用可编程频率合成芯片SY89429V产生基准时钟;当输入频率小于1kHz时,由单片机提供40kHz的基准时钟。然后根据输入频率的大小对基准时钟使用不同的分频数,从而产生采样时钟。

本系统采用了等效和实时两种采样方式。若输入频率小于1.25MHz,选用实时采样;反之,选用等效采样。根据输入频率确定时钟芯片的输出及分频数。当输入频率高于1kHz时,利用可编程频率合成芯片SY89429V产生基准时钟;当输入频率小于1kHz时,由单片机提供40kHz的基准时钟。然后根据输入频率的大小对基准时钟使用不同的分频数,从而产生采样时钟。

2 硬件设计

2.1总体设计

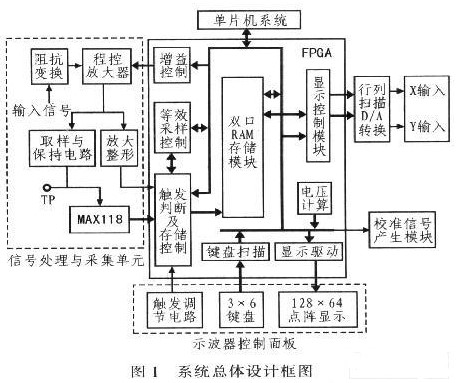

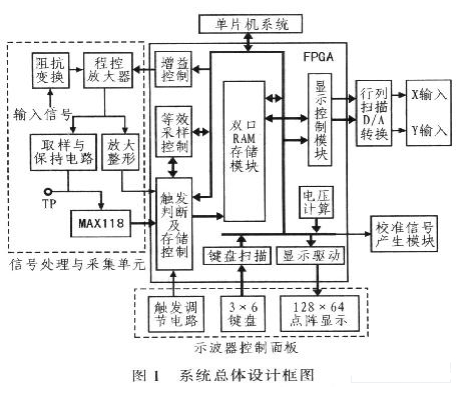

本系统在硬件上可分为五部分:控制器、测频及键盘控制、波形采样、程控时钟和液晶模块。系统功能如图1所示。

(1)控制器

控制器部分任务较重,通过两片89C52(MCU1和MCU2)来完成。其中,MCU1负责采样、数据处理以及程序时钟和液晶的控制工作;MCU2完成测频、DAC输出和键盘接口处理功能。两单片机通过串口通信。

(2)测频模块

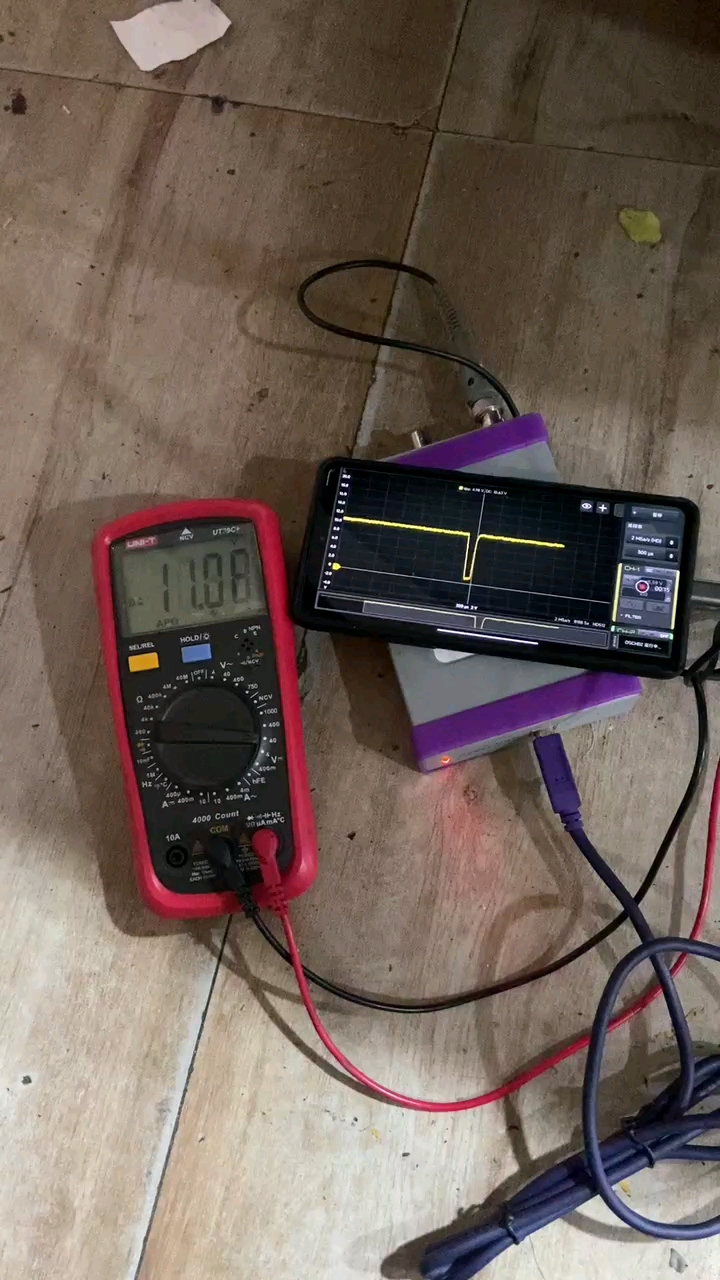

本系统输入信号的频率范围较宽(1Hz~80MHz),隔度范围较大(0.1V~2.2V),整形电路采用高速比较器TL3016实现,其参考电压由MCU1对输入信号采样获得。整形后的信号经程控分频器送至MCU2测频,精度可达四位有效数字。

(3)波形采样模块

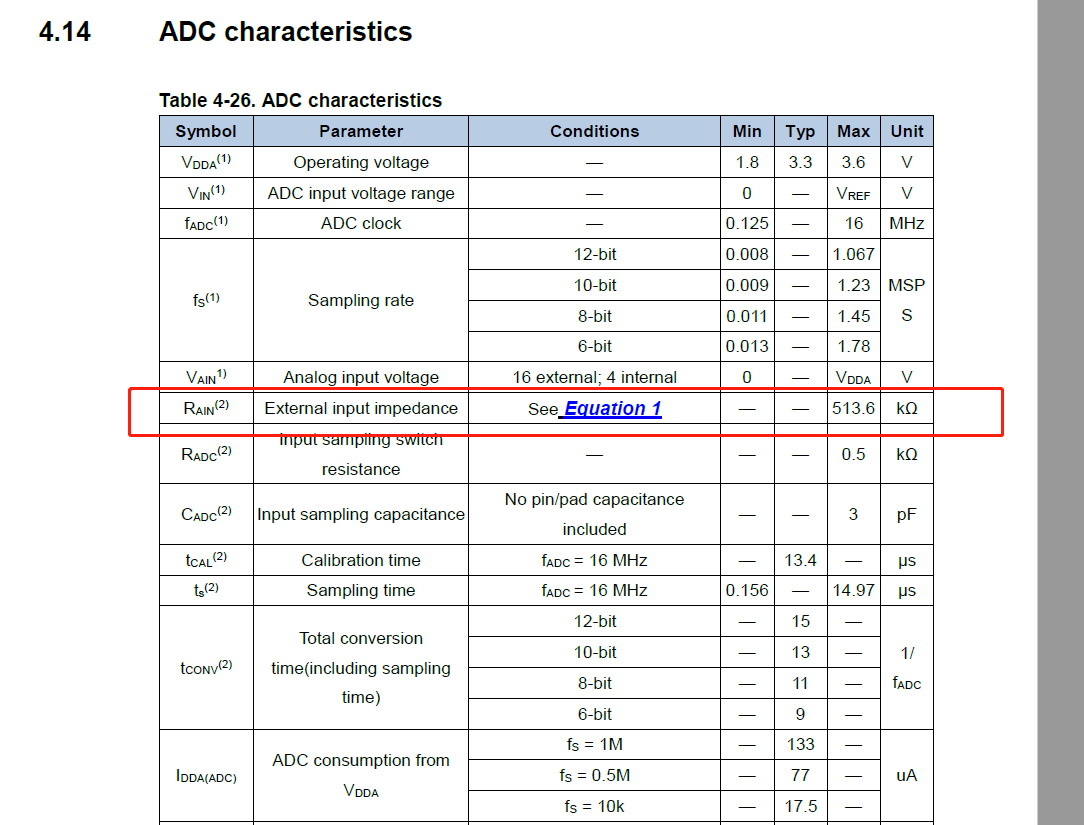

该模块由40MSPS的模数转换器TLC5540、静态存储器CY7C128A-20和可编程逻辑器件ispLSI1016E-80组成。

在程控时钟和程控分频器的控制下,CLPD产生存储器地址,将高速ADC的采样数据以程控频率写入静态RAM。写满256个点后,将静态RAM的控制权通过数据选择器转交给MCU1,由MCU1进行数据处理,并送液晶显示。

(4)程控时钟电路

程控时钟电路是本系统实现等效采样的关键,其核心是可编程频率合成芯片SY89429V。SY89429V的输出时钟范围是25MHz~400MHz,步进值0.125MHz~1MHz。它内部采用高频锁相环结构,对干扰很敏感,在硬件上采取了一定的抗干扰措施保证其稳定工作。

(5)液晶显示

液晶部分由点阵液晶显示器EDM160160、液晶控制器SED1335、SRAMHM62256、负压发生器和背光交流驱动电路发生器组成。

2.2 等效采样的实现

等效采样是本系统的关键和创新点。主要采用以芯片SY89429V为核心的精密时钟发生电路,控制高速ADC对高频信号进行循环间歇式采样。

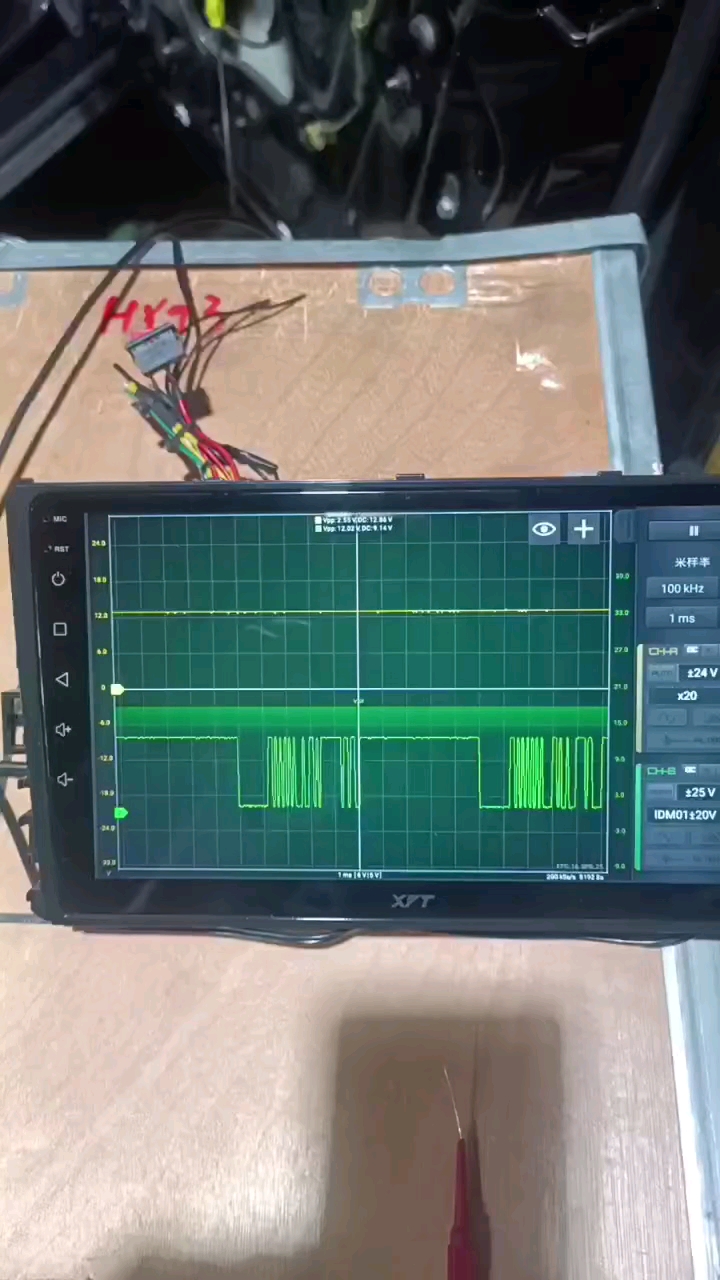

实现等效采样的系统框图如图2所示。

等效采样的输入频率是1.25MHz~80MHz。为了使复现的波形尽量精确,系统设计在1.25MHz~40MHz信号范围内每周期采一样一个点,在40MHz~80MHz信号范围内每个周期采一个点来复现波形。即采样频率范围要在1MHz~40MHz之间,并有可控的小步进值。

SY89429V的输出频率为25MHz~400MHz,需要外加分频电路将低低频部分扩展。同时,本系统选用的ADC为TLC5540,其转换速率是5MSPS~40MSPS,低端采样率会受到限制,可以采用控制RAM写入速度的方式来控制采样速率。综合考虑,采用CPLD器件,将SY89429V芯片TEST输出的FOUT频率经过程控二分频器,一方面提供给ADC作为CLK工作频率,另一方面再经过程控二五十进制分频器控制RAM写入速度,作为低端信号的采样频率。

3 软件设计

3.1 总体软件流程

总体软件流程如图3所示。MCU1接收MCU2的测频结果,并将幅值信息传递给MCU2,由MCU1根据输入频率确定采样方式,并控制精密时钟发生电路为ADC提供采样时钟。一次采样完成后,由MCU1处理采样数据并送LCD显示。

3.2 实时采样的实现

实时采样中,为了使采样得到的波形尽量精确,系统将1.25MHz以下的信号分为三个频率范围,在每个频率范围内由程控时钟电器产生某一固定的基准时钟,结合相应的分频数进行采样。具体设置如睛:输入频率为1Hz~1kHz,由单片机提供40kHz采样时钟;输入频率为1kHz~1MHz,由芯片SY89429V提供40MHz采样时钟;输入频率为1MHz~1.25MHz,由芯片SY89429V提供50MHz采样时钟。

3.3 等效采样的实现

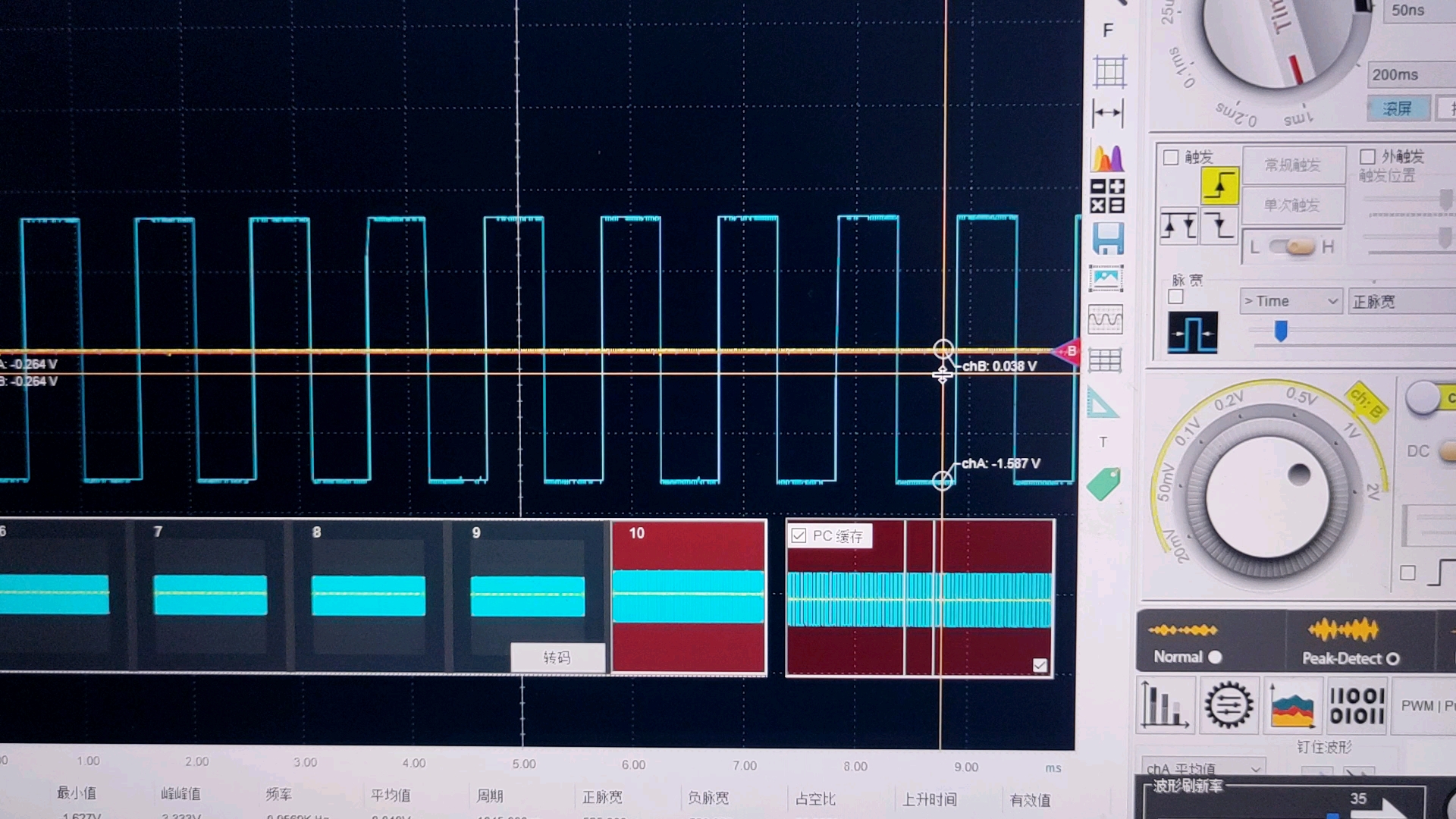

由于可编程频率合成芯片SY89429V在本系统所使用的25MHz~50MHz频率范围内,步进值始终为0.125MHz。为便于数据处理,软件设计过程中可以将所有的实际频率转换成以0.125MHz为单位的代值,即除以0.125MHz。

系统中所采用的模数转换器TLC5540的转换速率为5MHz~40MHz,当输入频率小于40MHz时,采用每个信号周期采一点的方法;当输入频率超过40MHz时,采用两个信号周期一点的方法。

下面以输入频率在1.25MHz~40MHz之间的情况为例,输入频率大于40MHz的情况可以类推得到。

将输入频率fin转换后的代值(以后简称代值)记为dfin,根据输入频率设定芯片SY89429V的频率字SY(只取整数,用于控制输出信号的频率),经过n分频后产生采样频率。根据等效采样的原理,采样频率与输入频率相近(对于输入频率为40MHz~80MHz的情况,采样频率与输入频率的二分频接近),二者频率代值的差值记做da,则SY可以表示为:

SY=(dfin-da) ×n (1)

这时复现一个波形所需的采样点数为:

d=(dfin-da)/da (2)

本系统选用的液晶为160×160点阵,将x轴上40个点所表示的时间定义为一格时基,记作A,则液晶屏幕上显示的周期个数为:

N=160×da/(dfin-da) (3)

由此,时基可以表示为:

A=N/(4×fin)=40×da/[fin×(dfin-da)] (4)

一个波形的采样点数也可以用时基和输入频率来表示:

d=40/(A×fin) (5)

笔者利用本文介绍的算法,实现了等效采样,能够地1MHz~80MHz的周期信号进行波形复现,效果令人满意。这种简易示波器在人机界面上为用户提供手动和自动两种工作模式,性价比高,有广阔的市场空间。

- 波器设计(5501)

相关推荐

51单片机差分采样

单片机AD采样周期

单片机ADC的采样频率和采样速率是不是同一个概念?采样频率、速率要远远大于被采样的信号频率和速率?

单片机是如何采样ADC值的?

单片机是如何对电流进行采样的

【AC620 FPGA试用申请】等效随机采样的数字存储式示波器

【Longan Nano申请】基于高速单片机的示波器设计

制做一个数字采样示波器

基于51单片机的简易数字示波器制作

学习单片机的采样流程

怎么在proteus中用示波器仿真单片机的输出波形?

怎样去测试STM32单片机ADC采样速率问题

用单片机做PID控制时采样时间的选择

基于单片机的等效采样示波器的设计

42

42【PADAUK】应广单片机 PMS150C系列 代烧录

应广单片机 PFS154系列 代烧录

【PADAUK】应广单片机 PMS134系列 商业级 烧录

【PADAUK】 应广PMS152E系列 应广单片机

【PADAUK】 应广PGS152单片机EEPROM芯片

【PADAUK】应广单片机 PFC151系列

8位FLASH单片机HR7P169BFGSD

8位FLASH单片机HR7P169BFGSF

九齐MCU单片机 NY8B072A SOP20 NY

NY8B062M型号单片机,台湾九齐AD单片机,技术支持

NY8A050D单片机,AD单片机,九齐代理

基于EDA技术的等效采样的设计实现

19

19基于单片机和FPGA的简易数字存储示波器设计

1159

1159

示波器的采样率和存储深度

7129

7129基于FPGA的等效采样存储示波器设计

126

126基于AT89S52单片机的简易数字示波器设计

9678

9678

基于单片机和FPGA的数字示波器的设计

277

277采样示波器原理结构

947

947

利用单片机和FPGA器件实现等效和实时采样方式的数字示波器设计

2265

2265

采用EDA技术的等效采样方案介绍

6715

6715

如何使用51单片机进行简易示波器的设计

14

14采用实时采样和等效采样相结合实现数字示波器的设计

2001

2001

实时示波器与采样示波器区别

10285

10285STC12C4052ADSTC单片机ADC采样C程序

51

51单片机如何采样电流

74

74单片机采样学习记录

1

1基于FPGA的等效时间采样原理的实现

537

537

示波器设置采样次数

624

624什么是示波器的实时采样率?什么是示波器的等效时间采样?

920

920示波器采样时间怎么设置 示波器的采样率有什么意义?

2206

2206单片机采样电压问题 单片机的供电电压过低对单片机AD采样有影响吗

1581

1581单片机如何直接采样互感器

429

429示波器实时采样与等效采样有何区别

319

319示波器测单片机输出波形怎么测

620

620采样示波器和实时示波器的区别

423

423等效时间采样示波器与实时示波器的对比,有什么不同?

321

321 电子发烧友App

电子发烧友App

评论