下面介绍五种降低离线反向电源功耗的方法,意识到电源设计人员面临的最大的一个挑战就是最小化轻负载和无负载时的功率损耗

2012-03-12 16:57:35 1438

1438

现在“零功耗”的含义是指在大多数应用中CPLD具有许多 节省功耗的特点,以及可以用于充分减少器件功耗需求的核心逻辑。

2011-11-21 15:48:54 1623

1623 功耗过高已经成为半导体制程尺寸进一步微缩的主要障碍,并且严重威胁到所有电子领域的一切进展,以下讨论五种可用于降低未来IC功耗的技术。这些技术目前已经在开发中,可望共同解决未来十年内将会面临的功耗

2014-05-19 10:38:21 2329

2329 概念: Power/Ground Gating是集成电路中通过关掉那些不使用的模块的电源或者地来降低电路漏电功耗的低功耗设计方法。该方法能降低电路在空闲状态下的静态功耗,还能测试Iddq。 理论

2020-09-16 16:04:15 10567

10567

什么是移动定位技术?什么是室内定位技术?

2021-05-19 06:21:31

降低FPGA功耗的设计技术 Design Techniques to Reduce Power Consumption Each generation of FPGAs gets

2009-12-18 16:49:59

设计技巧为什么能够节省功耗?降低FPGA功耗的设计技巧有哪些?

2021-04-30 06:04:19

降低一个MCU的主频就能降低运行的功耗吗

2023-10-11 08:15:48

一、前言低功耗是MCU的一项非常重要的指标,比如某些可穿戴的设备,其携带的电量有限,如果整个电路消耗的电量特别大的话,就会经常出现电量不足的情况,影响用户体验。二、降低MCU功耗平时我们在做产品

2022-02-11 07:12:23

串联电阻大概是线圈电阻的两倍。继电器闭合可靠性稍微有所降低。但功耗仅有原来不串电阻的1/3,继电器线圈发热减少许多,延长使用寿命

2019-01-08 16:11:58

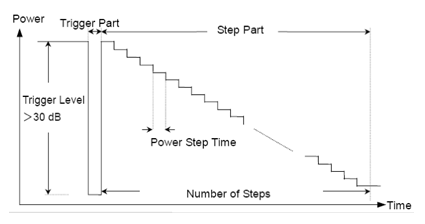

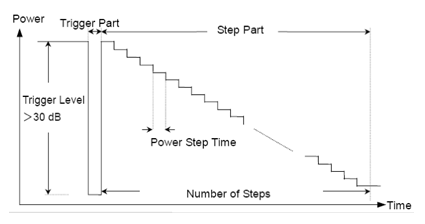

动态功耗,当然也会增加时序收敛的复杂度。但是,在电路中降低了25倍,这的确是非常重要的方法。图2.极低功耗技术,例如,子时钟电源选通,近/亚阈值工作等,实现了拉低曲线的新方法。这就带来了怎样降低寄存器

2014-09-02 14:55:03

CC2530芯片 ZED 和ZC,在组网正常的情况下,ZED可以进入低功耗模式,电流在uA级别。当关闭ZC后,ZED会持续的进行网络发现,无法进入低功耗模式。电流达28mA;求教,如何降低ZC发现网络的频次以降低功耗?或者有其他什么方法来降低功耗?

2016-04-07 14:19:54

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

FPGA中组合逻辑门占用资源过多怎么降低呢?有什么方法吗?

2023-04-23 14:31:17

技术亚阈值漏电流是静态功耗产生的主要原因之一,降低亚阈值漏电流将有效地降低芯片的静态功耗。亚阈值漏电流的解析模型如下公式所示:Vt为阈值电压,n为亚阈值摆幅系数,W为晶体管的宽度,L为长度,μ为电子

2020-04-28 08:00:00

逻辑门开关活动时的功率消耗,在这段时间内,电路的输入输出电容完成充电和放电,形成瞬间的轨到地的直通通路。与静态功耗相比,通常有许多方法可降低动态功耗。采用正确的结构对于设计是非常重要的,最新的FPGA

2015-02-09 14:58:01

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。如何减小动态和静态功耗?如何使功耗最小化?

2019-08-27 07:28:24

。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择

2019-07-05 07:19:19

自动降耗将是对设计流程早期以及逻辑综合过程中功耗减少的补充。 功耗是一个“机会均等”问题:从早期设计取舍到自动物理功耗优化,所有降低功耗的技术都彼此相互补充,并且需要作为每个现代设计流程中的一部分加以

2017-10-08 22:06:50

综合过程中功耗减少的补充。 值得注意的是,功耗是一个"机会均等"问题,从早期设计取舍到自动物理功耗优化,所有降低功耗的技术都彼此相互补充,并且需要作为每个现代设计流程中的一部分加以

2017-06-29 16:46:52

MOS降低发热功耗除了并联 还有其他的方法不?电流是不能变的。并联虽然内阻可以减小,不过好像会影响同步的开关速度。不同步开关的话MOS可能就烧了

2020-11-23 11:57:47

有什么方法可以进一步降低待机模式的功耗

2023-10-12 07:23:28

本人用了一块vs1053作为解码芯片,这个芯片在待机的时候电流为2.3ma左右,有没方法降低功耗,数据手册上也没怎么写,要是能降到1ma以内就好了。

2016-08-10 19:40:43

随着移动通信技术的飞速发展和移动通信网络技术的广泛应用,移动视频监控技术(mobile video supervision,MVS)也随之得到发展。相比于有线视频监控技术,MVS具有更高的应用灵活性,适合移动监控和远程监控,部署方便。因此,MVS系统在防暴、军事、气象、环保等领域的需求越来越迫切。

2019-08-09 06:52:35

你好,在无需使用BLE通信的应用程序中,降低电力消耗的有效途径是什么?在我的应用程序中不存在节电选项。CYW20706是主要的主机,所以我不能使用深度睡眠模式。应用程序使用周期性计时器(几十毫秒

2018-12-05 14:21:55

论低功耗蓝牙技术在智能移动设备中的应用。

2021-05-11 07:04:58

预测的下一状态条件列举状态机,并选择常态之间转换位较少的状态值。这样,您就能够尽可能减少状态机网络的转换量(频率)。确定常态转换和选择适当的状态值,是降低功耗且对设计影响较小的一种简单方法。编码形式越简单

2012-01-11 11:59:44

。 时钟门控的主要挑战是找到使用它的最佳位置,并在正确的周期创建时钟门控的开关逻辑。时钟门控是一种成熟的降低功耗技术,已经使用了很多年。Power Compiler等综合工具可以在时钟路径适当的位置

2022-04-12 09:34:51

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。本文将讨论减小动态和静态功耗的各种方法,并且给出一些例子说明如何使功耗最小化。

2019-07-12 06:38:08

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

一些方法,例如睡眠模式和低功耗设置,但我不确定是否有任何其他方法或技巧可以进一步降低功耗。有人有经验可以分享吗?我需要知道如何在保持通信稳定的同时最大限度地降低功耗。

2024-03-01 07:38:34

ZED 和ZC,在组网正常的情况下,ZED可以进入低功耗模式,电流在uA级别。CC2530芯片当关闭ZC后,ZED会持续的进行网络发现,无法进入低功耗模式。电流达28mA;求教TI工程师,如何降低ZC发现网络的频次以降低功耗?或者有其他什么方法来降低功耗?

2020-08-07 07:03:22

低功耗mcu的选择方法如何降低mcu的功耗

2021-02-24 06:11:07

电子产品的低功耗问题经常让产品设计者头痛而又不得不面对。以单片机(MCU)为核心的系统,其功耗主要由单片机功耗和单片机外围电路功耗组成。要降低单片机系统的功耗,需要从硬件和软件两方面入手。

2021-02-19 07:23:26

如何降低可重构系统的整体功耗?有什么方法能使可重构系统的性能和功耗需求之间达到平衡?

2021-04-08 07:09:23

降低蜂窝手机功耗并且延长其电池寿命是每一位手机设计工程师的目标。设计工程师正在不断将MP3播放器、照相机以及全运动视频等功能加入到现代手机中,从而需要不断地将功耗降到最低。

2019-08-23 08:26:40

引言针对中心机房功耗越来越大的问题,某些电信运营商制定了采购设备功耗每年降低20%的目标。半导体是功耗问题的关键所在,其解决方法是重新设计芯片实施和交付方案,而最新一代FPGA可以说是主要的推动力

2019-07-31 07:13:26

如何才能实现降低FPGA设计的功耗?

2021-04-29 06:47:38

随着车载电子设备越来越多,功耗问题变得日趋严重。例如,如果音频功率放大器的静态电流达到200ma,则采用12v电源时静态功耗就高达2.4w。有没有一种方法能开机但不需要扬声器发出声音的时候,关闭放大器来降低功耗?

2023-11-29 08:14:15

节省功耗的特性的实现和各种最少功耗数据存储技术的实现。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。 IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式

2020-05-13 08:00:00

高低电平翻转跳变沿期间,电流很大,存在较大功耗,所以,降低硬件电路功耗主要是降低电路动态功耗。 (3)采用多CPU系统 尽管现在已有各种可在不过多加重功耗负担的前提下提高性能的技术,但用一个芯片

2020-07-08 15:52:10

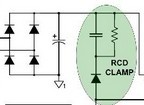

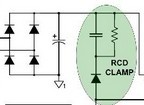

大功率开关电源降低功耗的技术方法

2019-03-15 08:54:20

速度和面积等指标的优化密切相关,需要折中考虑。下面讨论常用的低功耗设计技术。 2.1 动态电压调节 由式(1)可知,动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此

2016-06-29 11:28:15

可以做哪些措施来降低功耗

2023-10-23 07:51:09

从当前嵌入式消费电子产品来看,媒体处理与无线通信、3D游戏逐渐融合,其强大的功能带来了芯片处理能力的增加,在复杂的移动应用环境中,功耗正在大幅度增加。比如手机,用户往往希望待机时间、听音乐时间,以及看MPEG4时间能更长。在这样的背景下,如何降低入式芯片的功耗已迫在眉睫。

2019-08-28 08:27:58

从当前嵌入式消费电子产品来看,媒体处理与无线通信、3D游戏逐渐融合,其强大的功能带来了芯片处理能力的增加,在复杂的移动应用环境中,功耗正在大幅度增加。比如手机,用户往往希望待机时间、听音乐时间,以及看MPEG4时间能更长。在这样的背景下,如何降低嵌入式芯片的功耗已迫在眉睫。

2019-09-18 06:22:27

自己做了一个电路板,因为功耗除了点问题,怎么降低电路板功耗呢

2019-08-07 22:21:34

从事便携式或手持产品设计的工程师都明白对于如今的设计,最大限度地降低功耗是必不可少的要求。但是,只有经验丰富的工程师理解尽可能地延长系统的电池寿命的那些微妙但又重要的细节。本文中我们的重点是,如何使用超低功耗的复杂可编程逻辑器件(CPLD)?如何在嵌入式设计中降低CPLD的功耗?

2019-08-01 08:19:42

怎样来降低 MSP430 的功耗,请大家来讨论下

2014-12-30 18:45:06

降低功耗的最重要的途径是使用MSP430的时钟系统来最大限度地提高MSP430处于低功耗模式的时间。怎样降低msp430的功耗?

2014-11-09 23:10:18

随着移动电话向着具有丰富媒体功能的无线平台发展,对功率预算的控制是开发的重点。降低存储器的功耗可以显著延长移动电话的电池寿命。为了降低存储器的功耗,业界使用了两种不同的基于DRAM的存储器架构:本地

2009-10-08 15:53:49

~1Gb/s的数据率以及支持OFDMA调制、支持MIMO天线技术,乃至支持VoWLAN的组网,因此,在射频信号链设计的过程中,如何降低射频功率放大器的功耗及提升效率成为了半导体行业的竞争焦点之一。目前行业发展呈现三条技术路线,本文就这三条技术路线进行简要的比较。

2019-07-05 06:29:06

降低功耗不光能够大大的节约电能还能简化电源部分的设计,甚至可以用于手持设备上面使用,这些都已经越来越成为未来产品的设计方向。

2021-02-26 07:27:17

时可以使用多线程下载方式,缩短了下载的时间,减少了WiFi开启时间,及CPU的数据处理时间,相比单线程的低性能下载还是可以节省不少的功耗。Android应用软件采用不同的逻辑代码编写,能否降低功耗

2018-09-19 18:11:19

液晶显示(LCD)技术的基本原理是什么?液晶显示(LCD)噪声产生的原因是什么?有什么方法可以降低LCD的噪声?

2021-05-31 06:08:04

电源门控可以降低泄漏功耗吗?有哪几种情况采用PG能显著减小泄漏功耗呢?

2022-02-11 06:34:36

方法 通过分析功耗产生的原因,可以判断降低功耗受到很多约束,需要在各个要素之间反复衡量。数字IC低功耗的设计应该从顶层到底层各个阶段进行优化,如工艺级低功耗技术、电路级低功耗技术、RTL级(寄存器

2020-07-07 11:40:06

行为逻辑层次低功耗设计前言:随着集成电路制造技术的快速发展,未来单一硅片上集成的晶体管数将超过lO亿以上。这使得功耗问题变得越来越突出,将成为影响电路性能的关键问题。关键词:低功耗设计SOC逻辑

2013-05-16 20:00:33

什么是TICKLESS?怎么能实现功耗的降低呢?TICKLESS是如何去实现功耗降低的呢?

2022-02-24 08:02:02

stm32进入低功耗模式,必须用中断来唤醒,现在就是不用这种模式,如何通过程序来降低功耗啊

2019-05-06 18:43:22

如何利用FPGA设计技术降低功耗?

2021-04-13 06:16:21

随着车载电子设备越来越多,功耗问题变得日趋严重。例如,如果音频功率放大器的静态电流达到200ma,则采用12v电源时静态功耗就高达2.4w。有没有一种方法能开机但不需要扬声器发出声音的时候,关闭放大器来降低功耗?

2018-08-06 08:23:20

降低显示功耗来延长移动电池寿命

2021-04-02 07:29:21

在嵌入式设计中降低CPLD的功耗

本文中我们将重点放在这些经验丰富的专家是如何使用超低功耗的复杂可编程逻辑器件(CPLD),并从他们的嵌入式设计中的I/O子系

2010-04-12 10:04:02 27

27 利用先进的校准测试方法降低移动设备的成本

如今消费者利用10年前连听都没有听说过的各种方式使用移动设备已是很平常的事情了。无论是在他们喜爱

2009-04-05 12:57:58 690

690

降低蓝牙装置的功耗的方法

在2004年11月,Bluetooth SIG修订了 2.0+ Enhanced Data Rate (EDR)规格,结合一种革命性的技术,创造出更有效率

2010-03-05 14:34:48 1031

1031

的主要原因,但并非唯一因素,而且通过晶体管来降低功耗作用是有限的。通过更全面的系统级方法能够更有效地降低功耗。只有全面兼顾芯片工艺技术,充分发挥功率感知型 (power-aware tool)工具的作用

2017-11-24 18:37:33 1368

1368 们已经开发出一系列的创新技术,以用于减轻目前所面临的问题,并可望对振兴未来的芯片产业有所助益。 以下讨论五种可用于降低未来IC功耗的技术。这些技术目前已经在开发中,可望共同解决未来十年内将会面临的功耗问题。 拥抱协

2017-11-30 11:32:01 503

503

概率功耗估算方法和条件概率功耗估算方法估算的功耗作为优化的成本函数时,由于方法本身的局限性或忽略了电路节点特点会降低估算结果的准确度,从而影响功耗优化结果。针对上述问题,提出一种新的电路功耗估算方法

2018-03-12 16:24:05 0

0 我们首先来了解在嵌入式设计中如何降低CPLD的功耗、电路板的面积和元器件成本。下一步,我们将看到在待机模式下如何尽量降低CPLD的功耗,不仅要仔细地选择器件,而且还要选择一个合适的总线驻留方案。器件工作期间,我们对节省功耗的探讨将包括选择逻辑门、智能I/O设计和精密的电源电压管理技术。

2018-12-04 09:09:00 2142

2142

设计人员总是在寻找减少不需要的功耗组件的方法,无论是通过以低功耗技术的方式设计设计,还是采用可以降低功耗的工艺。但是,其中一些解决方案的代价是性能,可靠性,芯片面积或其中的几个。最终,人们必须在功率,性能和成本之间达成妥协。下面的文章旨在讨论其中的一些技巧。这些技术分为建筑技术和基于过程的技术。

2019-08-09 14:32:55 14246

14246

传统上,降低软件无线电(SDR)硬件的功耗一直是我们工作的重点,但是,显而易见软件也有重要影响,因此,需要一种降低 SDR功耗的整体设计方法。一种能发挥SDR功能的测试床能帮我们解决这个问题。由于像美国联合战术无线电系统(JTRS)这样的计划,软件定义的无线电(SDR)早已被证实。

2020-10-20 10:42:00 0

0 ,导致人工成本过高。 因此,如何降低LoRa节点的功耗,是本领域常见的技术追求。 本文介绍数据速率DR和LoRa节点功耗的关系,从而介绍一种显著降低LoRa节点功耗的方法。 想了解更完整的LoRa节点低功耗策略,可以参见文章LoRa终端低功耗策略。 如果想

2020-10-26 15:21:36 1786

1786 clock) 是通过在时钟路径上增加逻辑门对时钟进行控制,使电路的部分逻辑在不需要工作时停止时钟树的翻转,而并不影响原本的逻辑状态。在ASIC和FPGA设计中都存在门控时钟的概念(前者应用更广)。 典型的门控时钟逻辑如下图所示: 二、门控时钟降低功耗

2021-09-23 16:44:47 12192

12192

1、如何降低功耗?

(1) 优化方向:

组合逻辑+时序逻辑+存储

(2) 组合逻辑:

(a)通过算法优化的方式减少门电路

(b)模块复用、资源共享

(3) 时序逻辑:

(a)尽量减少无用

2022-02-11 15:30:36 2

2 很明显。对于消费级芯片(如手机CPU,IoT芯片等),由于往往应用在小型移动设备中,低功耗设计就显得尤为重要。

2022-08-17 11:04:42 5816

5816 逻辑系统设计技术降低开关 CMOS 功耗

2022-11-15 20:05:46 0

0 如何降低设备功耗,降低采集设备功耗的几种方法 工程监测传感器 以下是降低数采设备功耗的一些方法: 优化硬件设计:通过选择低功耗的芯片、使用更高效的转换器、减少功率损耗等方式来优化硬件设计,从而降低功耗

2023-10-11 09:29:00 511

511

电子发烧友App

电子发烧友App

评论