采用Actel的Flash FPGA如ProASIC3; 3.对成本要求高和加密要求适中:可以采用从系统级来实现加密功能,如普通FPGA+带加密功能MCU(FPGA的数据通过加密功能MCU配置

2019-07-09 09:11:44

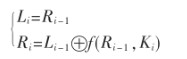

,是要被加密或解密的数据,DES采用16轮运算,每轮产生一个轮密钥参与到运算中,密钥与明文运算时采用按位异或的方法(不仅仅是与密钥异或),但每一位存放的数据只有0或1,因此,DES的密钥空间仅仅只有2^56。2、3DES加密算法由于密钥太短,DES被破解的可能性太大,于是产生了3DES算法,即3重DES

2021-07-22 09:13:59

传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,运算速度较慢,安全性也较差。而硬件加密是通过专用加密芯片、FPGA芯片或独立的处理芯片等实现密码运算。相对于软件加密,硬件加密具有加密速度快、占用计算机资源少、安全性高等优点。

2019-08-05 08:03:25

有人知道怎样使用FPGA的ID号实现子模块的加密?

2012-04-18 10:40:34

FPGA系统设计原则和技巧之:FPGA系统设计的3种常用IP模块.pdf(1012.86 KB)

2019-04-24 13:33:04

的数目之外,就是采用可编程逻辑器件,主要是FPGA芯片来实现。本课程以DSP设计在FPGA芯片上的开发为主线,遵照由浅入深的基本步骤和思路进行详细讲解,每一个知识点都给出了基于ISE(HDL语言

2009-07-21 09:22:42

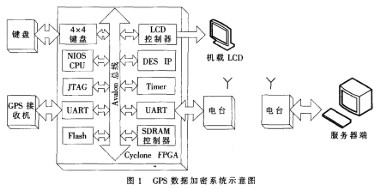

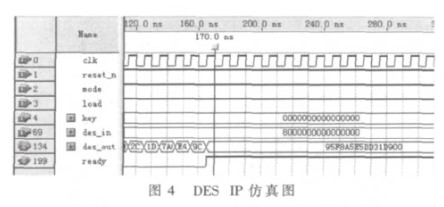

针对GPS测量系统数据传输过程中的安全问题,采用FPGA技术设计了GPS数据加密系统。系统移植MD5算法到NIOS中对系统口令加密,并设计DES IP对GPS数据加密。实验表明,该设计可有效防止GPS数据被非法窃取,具有安全性强、速度快、操作简便等特点。

2019-08-22 06:03:00

通过ARM处理器建立操作系统实现任务调度。尽管采用DSP和ARM芯片可使系统的运算能力和管理事务的能力得到很大增强,但是构成完整的数据采集系统通常还需要外部逻辑控制器件,尤其不能将数据采集和刺激信号源

2019-05-16 07:00:09

1. 为什么要使用FPGA实现在全控型电力电子开关器件出现以后,为了改善交流电动机变压变频调速系统的性能,科技工作者在20世纪80年代开发出了应用脉宽调制(PWM)技术的变压变频器,由于它的优良

2022-01-20 09:34:26

的控制核心。但利用中低端FPGA还没有可以达到100MHz以上的时钟数据恢复电路。由于上面的原因,许多利用FPGA实现的高速通信系统中必须使用额外的专用时钟数据恢复IC,这样不仅增加了成本,而且裸露

2009-10-24 08:38:08

用户逻辑的功能。PCI开发板演示软件可以显示数据传输速率,也可用于调试,配置PCI Core。基于IP模块的PCI设计为用户在FPGA目标器件上实现PCI接口提供了一种有效的途径,设计工程师可以将主要精力

2019-05-08 07:00:46

操作系统中的实现有很大不同。首先,由于嵌入式处理器的时钟频率低,地址、数据总线窄,导致嵌入式系统对一个通用IP包的处理要花费更多的处理机时间,从而影响其他任务的执行,因此需要对庞大的复杂的TCP/IP

2019-04-28 09:57:18

的数据包,该ARP请求就是因为要发送这个包而发送的。这种方法在假设上层会重发被覆盖的数据时采用。每隔十秒钟,表就会刷新一次,旧的记录被丢弃,在嵌入式TCP/IP协议栈中,记录的有效时间为1秒。 2.2.2

2019-04-23 07:00:10

。由于系统核心网络的全IP化,并引入了控制与业务、传送与接入分离的中交换设计思想,在IP上实现A接口协议与在传统电路交换上实现A接口有所不同,主要是需要设计信令与业务分离的A接口协议栈以及信令流、业务

2019-05-17 07:00:09

(Intellectual Property)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短

2019-07-29 08:33:45

XC2S200型FPGA器件实现。采用Spansion公司的NOR Flash存储器来存放配置文件,其型号为S29GL512N,容量为512 Mb。系统总体框图如图3所示。上位机软件包括Flash烧写

2019-05-30 05:00:05

只需要三分之一的器件面积。采用竞争技术和工具尝试实现PCIe内核的用户会发现,使用Altera硬核IP结合Qsys系统集成工具,在设计和调试时间上平均能够节省6个星期的时间。Altera还在FPGA中

2015-02-09 15:02:06

加密卡,内部集成DES、AES、SHA、RSA、ECC等算法,手机开发商,可以调用加密SD卡中的加密算法,对手机的语音通讯以及短信进行加密,对存储在手机中的电话本或者短信进行加密,实现真正的加密手机

2014-02-28 09:50:30

1、M487芯片CRYPTO模块中对称加密AES功能测试本次测评主要测试新唐M487芯片CRYPTO模块中对称加密AES功能及其性能,性能方面会使用硬件加速和纯软件实现直接的效率差异。M487中

2022-04-22 17:52:48

,它的局限性也逐渐暴露出来.在很多计算机信息安全系统中,硬件加密手段被应用到设备中来提高密码运算速度和系统的安全性. 给出了一种RC4加密算法的FPGA实现方案,相比用软件实现,该方案速度更快,安全性更高

2012-08-11 11:48:18

USB_OTG_IP核中AMBA接口的设计与FPGA实现

2012-08-06 11:40:55

”。 目录结构如下 将“DES加密算法C语言.txt”除main函数外所有程序复制至DES_DLL.cpp中。将需要被调用的函数前面添加DES_DLL_APIDES_DLL_API int

2013-08-26 00:14:10

处理器的数目之外,就是采用可编程逻辑器件,主要是FPGA芯片来实现。本课程以DSP设计在FPGA芯片上的开发为主线,遵照由浅入深的基本步骤和思路进行详细讲解,每一个知识点都给出了基于ISE(HDL语言

2009-07-21 09:20:11

法,是美国联邦***采用的一种区块加密标准。这个标准用来替代原先的DES,已经被多方分析且广为全世界所使用。经过五年的甄选流程,高级加密标准由美国国家标准与技术研究院 (NIST)于2001年11月26

2012-06-12 23:12:59

软硬件功能开发,SDAccel则是一款基于OpenCL开发框架的设计工具。由此可见FPGA/SoC供应商已经花费大量的精力来优化器件并且完善开发工具,使它们更易于应用到嵌入式系统设计中,同时我们的学习

2018-07-31 09:59:45

,以太网承担着系统的数据通讯模块,主要实现系统的数据传输。2 以太网接口设计 以太网模块设计主要完成以太网控制器IP核用户端接口协议与多核系统网路通讯协议的转换。以太网接口硬件结构设计如图2所示,以太网

2019-06-03 05:00:02

SPI4-P2接口形式可直接采用Altera公司的IP Core实现。Altera的主流FPGA均实现了硬件DPA功能,以Stratix II器件为例,在使能DPA的情况下使用SPI4-P2 IP Core可实现

2012-11-09 18:43:41

传感器信息融合在同一个坐标系中,因此需要研究机载环境中高清视频处理技术,研究在较大尺寸的显示器上显示处理高清视频信号。 高清视频处理模块位于显示分系统中,加速显示高清视频信号,实现高清视频的缩放和叠加

2018-11-07 10:42:22

FPGA实现的二阶FLL和三阶PLL相结合的载波跟踪方法。硬件实现采用Altera Cyclone II FPGA中的EP2C70。对该模块的Verilog硬件描述语言编程方法也进行了详细说明。实验测试

2009-09-19 09:38:40

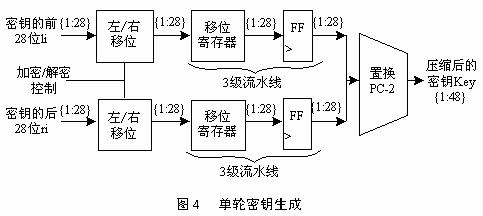

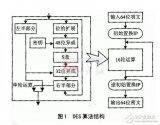

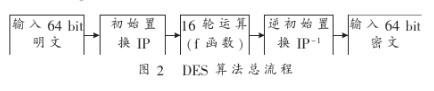

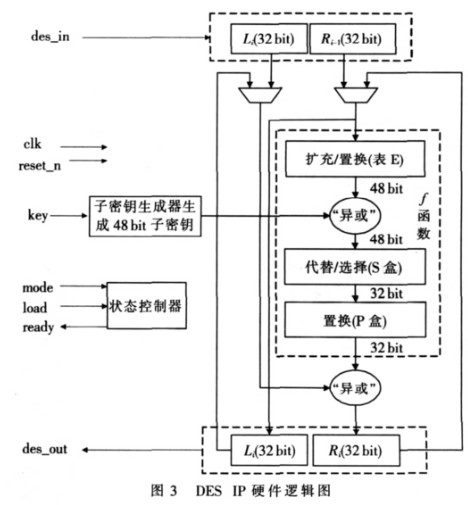

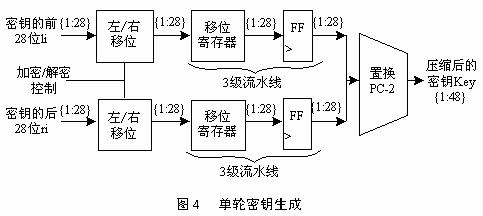

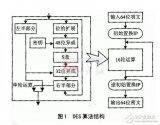

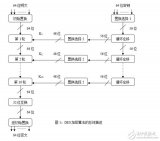

布局和布线。下面从S盒硬件宏的实现和DES加密核的实现来介绍基于FPGA的DES加密模块实现。2.1 S盒硬件宏的实现S盒的设计是DES算法关键部分,S盒设计的优劣将影响整个算法性能。在采用FPGA

2018-10-18 16:29:45

。为了实现高速、连续采样的数据采集系统,本文介绍了一种基于 FPGA +AD7609的数据采集系统的构成及技术实现。采用 FPGA 作为主模块,AD7609为数据采集模块,并设计了硬件实现电路。实验测试

2018-08-09 14:28:00

时间。针对上述研究现状和分布式采集场景分析,本文介绍了一种基于FPGA和TOE架构,实现TCP/IP协议数据传输的多路采集与切换系统。该系统涉及并行数据采集、多路通道切换、TCP/IP协议通信等模块

2021-07-12 08:30:00

的数据发送和接收功能的实现。图 9 W5500功能实测结果图3 结语本系统实现了基于FPGA的,采用嵌入式以太网W5500芯片以硬件形式实现的TCP/IP协议栈,提高了CPU的处理效率,并且使得通信速率在很大程度上得到了提高,为以太网数据传输系统的设计提供了一种有效的方式。

2018-08-07 10:10:25

基于FPGA的16位数据路径的AESIP核提出一种基于FPGA 的16位数据路径的高级加密标准AES IP核设计方案。该方案采用有限状态机实现,支持密钥扩展、加密和解密。密钥扩展采用非并行密钥扩展

2012-08-11 11:53:10

此提供了新的解决方案。IP核(IP Core)是具有特定电路功能的硬件描述语言程序,可较方便地进行修改和定制,以提高设计效率[3]。本文研究了基于FPGA的数据采集控制器IP 核的设计方案和实现方法,该IP核既可以应用在独立IC芯片上,还可作为合成系统的子模块直接调用,实现IP核的复用。

2019-07-09 07:23:09

基于FPGA的机载显示系统该如何去设计?如何对机载显示系统进行优化?

2021-06-01 06:04:12

椭圆曲线加密是一种目前已知的所有公钥密码体制中能够提供最高比特强度的一种公钥体制。在FPGA实现椭圆曲线加密系统时,基于GF(2)的多项式有限域中的乘法、求逆运算是其中的两大难点。

2019-10-10 07:36:43

可以利用板上PROTOTYPE区实现用户逻辑的功能。PCI开发板演示软件可以显示数据传输速率,也可用于调试,配置PCI Core。 基于IP模块的PCI设计为用户在FPGA目标器件上实现PCI接口

2019-04-17 07:00:06

。本文采用RFC815中的重组算法实现的基于FPGA的IP碎片重组模块能够提供对OC-48接口流量的支持,具有硬件开销小,可扩展性好的特点,并提供了一种针对IP碎片攻击的预警机制,能够抵抗常见的IP

2008-10-07 11:01:03

的挑战。本文采用RFC815中的重组算法实现的基于FPGA的IP碎片重组模块能够提供对OC-48接口流量的支持,具有硬件开销小,可扩展性好的特点,并提供了一种针对IP碎片攻击的预警机制,能够抵抗常见

2008-10-07 11:00:19

图像跟踪系统。一方面,采用双DSP体系结构实现系统任务的并行划分使本系统具备极高的运算处理速度;另一方面,现场可编程逻辑器件FPGA的引入使系统的灵活性也得到极大的提高。而将两者结合可使本系统充分体现新一代机载实时图像跟踪系统更快速、更精确、更灵活的特点。

2019-07-02 06:57:27

解码器设计中采用专用的控制模块来控制加密和解密操作;同时,在RAM模块中自主设计了具有并行读写功能的子模块,以进一步提高算法的数据加密速度;整个系统在DE2实验平台中经过反复实验测试和试运行,结果表明该算

2010-04-24 09:15:41

多FPGA系统中自定义高速串行数据接口设计为方便多FPGA系统中主从FPGA之间的命令与数据传输,节省连接的引脚数量,设计了一种基于FPGA的自定义高速串行数据传输模块。对主从串行模块进行了详尽

2012-08-11 11:49:57

本文针对传统实时操作系统内核占用系统资源、影响系统实时性的问题,提出了用单独的硬件电路实现实时操作系统中的系统调用和任务调度器的方案。重点给出了采用FPGA实现μC/OS-Ⅱ任务管理模块的过程。仿真结果表明,任务管理的硬件实现保持了系统调用的正确性,同时减少了系统调用的执行时间、降低了处理器系统开销。

2021-04-26 06:14:59

在不对原有应用系统作大的改动的情况下,3-DES算法有了很大的生存空间,被大量用来替换已不安全的DES算法。那么该如何采用FPGA进行3-DES算法的高速设计呢?

2021-04-08 06:02:07

(IntellectualProperty)核。IP核由相应领域的专业人员设计,并经反复验证。IP核的拥有者可通过出售IP获取利润。利用IP核,设计者只需做很少设计就可实现所需系统。基于IP核的模块化设计可缩短设计周期,提高设计质量。现场

2019-09-03 07:44:22

DES算法的简单原理是什么?如何去实现DES加密算法?

2021-04-26 07:14:21

我国三金工程尤其是金卡工程的启动,DES算法在POS、ATM、磁卡及智能卡(IC卡)中被广泛应用,以此来实现关键数据的保密。如信用卡持卡人的PIN的加密传输、IC卡与POS间的双向认证、金融交易中

2009-04-07 09:25:29

在现代电子系统的设计中,高速 FPGA运行时需将其配置数据加载到内部SRAM 中,改变SDRAM 里面的数据,从而使FPGA实现不同的功能,即所谓的可重构技术[1]。但是由于其采用的是基于SRAM

2019-08-05 06:43:09

为了克服传统DES加密算法流水线的FPGA实现的子密钥需先后串级计算,密钥不能动态刷新的缺点,提出一种新的加密算法,提高DES FPGA实现系统的处理速度,增加系统的密钥动态刷新功能,提高系统的可重用性。

2021-04-30 06:29:47

接口和总线管理。实现真正的模块化设计。本文用一个具体的FPGA设计例子来展现NoC在FPGA内部逻辑互连中发挥的重要作用。本设计主要是实现三重数据加密解密算法(3DES)。该算法是DES加密算法的一种

2020-05-12 08:00:00

将生成加密的bit文件直接下载到FPGA可否实现子模块加密?将ID验证与子模块一起综合成ngc文件,再给工程用,ngc能否被破解?

2012-04-18 10:45:22

请问GPS9808的功能与特点是什么?GPS9808应用于汽车智能防盗系统中的实现方法 有人知道吗?

2021-03-05 08:02:46

时间采样实现2.1 系统硬件实现框图系统的总体框图如图2,FPGA 控制的等效采样时钟连接到ADC 器件的时钟部分,ADC 器件在时钟的控制下对宽带模拟信号进行采样,采集到的数据传送到FPGA 中

2020-10-21 16:43:20

了网关接口设备中核心器件,即NGN网关接口芯片的设计方法以及在Xilinx的Spartan3 XCS1000中的实现。方案介绍在本方案中,网关接口设备的主要功能是由网关接口板IP_GATEWAY所实现

2019-04-23 07:00:08

800Mbps准循环LDPC码编码器的FPGA实现CCSDS星载图像压缩模块的FPGA设计与实现FPGA和Nios_软核的语音识别系统的研究RC4加密算法的FPGA设计与实现多FPGA系统中自定义

2012-02-02 17:26:14

des加密算法代码

/* d3des.h - * * Headers and defines for d3des.c * Graven

2008-01-16 10:12:52 33

33 为了满足工程上实时加密和密钥安全管理的需要,越来越多的加密算法开始采用可编程逻辑器件实现。数据加密标准DES 及其变形3-DES,是当前应用最为广泛的加密算法。在算法中,S

2009-05-18 13:22:46 13

13 通过对分组密码DES 算法IP 变换、IP 逆变换、S-盒换位表的分析,找出了他们的换位规则,根据这种规则提出了一种对DES 算法软件实现的改进方法。关键词:DES,IP 变换,IP-1

2009-05-30 10:19:59 7

7 设计并实现了一种以单片机为主要控制器件、基于GSP 模块的新型智能电动汽车底盘的导航系统。GPS定位系统主要采用技术非常成熟的GPS模块进行与单片机的接口通信完成,使用更方

2009-08-31 15:51:40 44

44 本文设计并实现了机载SAR 监控系统,在系统设计中采用89C52 作为处理器,并结合FPGA 对几个关键技术进行了分析。介绍了系统结构,总体方案

2009-09-15 10:28:01 15

15 针对数据加密算法的硬件设计,主要讨论了一个基于PCI 总线的数据加密系统的设计与实现过程。首先对系统体系结构以及在FPGA 芯片内部对PCI 接口模块的实现进行了分析,然

2009-09-17 12:00:31 29

29 针对数据加密算法的硬件设计,主要讨论了一个基于PCI 总线的数据加密系统的设计与实现过程。首先对系统体系结构以及在FPGA 芯片内部对PCI 接口模块的实现进行了分析,

2009-12-25 15:51:52 14

14 用硬件实现数据加密已成为信息安全的主流方向。本文提出了一种基于FPGA 的低成本的AES IP核的实现方案。该方案轮内部系统资源共用,减少了系统资源的占用。输入密钥与输入数据

2010-01-06 15:11:03 10

10 针对Data Encryption Standard(DES, 数据加密标准)算法所存在的不足和混沌序列的特点,提出了一种新的基于蔡氏电路和DES 的图像加密算法。该算法将蔡氏电路所生成的混沌序列与DES 算

2010-01-07 16:02:04 12

12 介绍了3DES 数据加密算法(DDA)的原理,针对利用FPGA 硬件实现3DES 算法,给出了一种可进化IP 核的具体设计思想,采用可重构电路节省器件内部资源,并采用有限状态机设计技

2010-01-16 15:42:04 14

14 介绍了基于单片机、FPGA的网络数据加密实现。整个系统由单片机,FPGA和E1通信接口组成。流密码加密算法采用A5/1和W7算法。采用VHDL硬件语言实现FPGA功能。该硬件加密系统具有较好

2010-12-24 16:26:54 27

27 摘要:介绍3-DES算法的概要;以Xilinx公司SPARTANII结构的XC2S100为例,阐述用FPGA高速实现3-DES算法的设计要点及关键部分的设计。引 言

2006-03-13 19:36:42 652

652

利用汇编语言实现DES加密算法

DES算法是一种数据加密算法。自从1977年公布以来,一直是国际上的商用保密通信和计算机通信的最常用的加密标准。DES算法的实现一般用高级

2009-04-07 09:24:51 1130

1130 摘要:介绍3-DES算法的概要;以Xilinx公司SPARTANII结构的XC2S100为例,阐述用FPGA高速实现3-DES算法的设计要点及关键部分的设计。

关键词:3-DES

2009-06-20 14:22:00 1317

1317

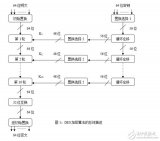

摘要: 介绍了3DES加密算法的原理并详尽描述了该算法的FPGA设计实现。采用了状态机和流水线技术,使得在面积和速度上达到最佳优化;添加了输入和输出接口的设

2009-06-20 15:22:28 1062

1062

基于FPGA的DES、3DES硬件加密技术

传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,运算速度较慢,安全性也较差。

2009-07-26 22:35:43 1347

1347

一种密钥可配置的DES加密算法的FPGA

摘 要: 在传统的DES加密算法的基础上,提出一种对密钥实行动态管理的硬件设计方案,给出了其FPGA实现方法。通过对DES加密

2009-09-19 09:14:05 949

949

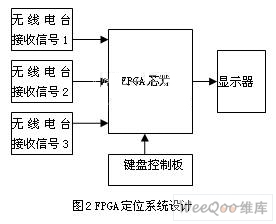

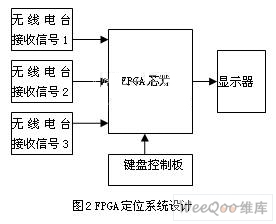

GPS定位替代系统的FPGA实现

概述:本文在分析目前使用的GPS定位系统的基础上,探讨了一种替代系统,系统通过接收不同城市广播电台的发出的报时信号,算出这些地

2010-04-17 17:40:35 1024

1024

DES 算法具有对称性, 既可以用于加密又可以用于解密。对称性带来的一个很大的好处在于硬件实现, DES 的加密和解密可以用完全相同的硬件来实现。DES 算法的明文分组是64 位, 输出密文

2011-08-26 10:48:38 21088

21088 为防止在数据通信中传输信息被他人接收、截获,结合分组密码的成功代表DES 加密算法和流密码学的基本理论以及DES 加密算法的应用误区,设计了一种基于DES 算法的变形DES ,即IDESA( Impr

2011-09-23 17:53:06 0

0 一种密钥可配置的DES加密算法的FPGA实现

2016-05-11 11:30:19 11

11 介绍了AES加密标准的Rijndael实现方法,设计了一种适合应用于嵌入式系统32位数据界面时序紧凑的AES加密IP核。该IP核能以较低的资源消耗实现在低端FPGA上速度为256Mb/s的AES加密,且可将数据位宽扩展为64位或128位等,满足多种数据位宽应用的要求。

2017-09-07 19:14:58 13

13 摘要: 介绍了3DES加密算法的原理并详尽描述了该算法的FPGA设计实现。采用了状态机和流水线技术,使得在面积和速度上达到最佳优化;添加了输入和输出接口的设计以增强该算法应用的灵活性。各模块均用硬件

2017-11-06 11:10:09 4

4 DES算法的入口参数有三个:Key、Data、Mode。其中Key为7个字节共56位,是DES算法的工作密钥;Data为8个字节64位,是要被加密或被解密的数据;Mode为DES的工作方式,有两种:加密或解密。

2017-12-09 09:10:44 17432

17432

3DES,也称为3DESede或TripleDES,是三重数据加密,且可以逆推的一种算法方案。975年美国IBM公司成功研究并发布了DES加密算法,但DES密码长度容易被暴力破解,通过对DES算法进行改进,针对每个数据块进行三次DES加密,也就是3DES加密算法。

2017-12-09 09:43:56 29741

29741

DES算法为密码体制中的对称密码体制,又被称为美国数据加密标准,是1972年美国IBM公司研制的对称密码体制加密算法。 明文按64位进行分组,密钥长64位,密钥事实上是56位参与DES运算

2017-12-10 11:06:46 68699

68699

摘要:DES算法为密码体制中的对称密码体制,又被称为美国数据加密标准,是1972年美国IBM公司研制的对称密码体制加密算法。明文按64位进行分组,密钥长64位,密钥事实上是56位参与DES运算。它将64位输入经过一系列变换得到64位的输出。下面我们来看看c语言实现des加密算法详细过程。

2017-12-10 11:28:57 34524

34524

(LFSR)的混合加密算法并通过FPGA实现,FPGA根据用户输入的密码组合,通过线性反馈移位寄存器产生一串密钥,然后通过USB将这串密钥发送至计算机中。上位机软件实现与下位机的USB通讯、用DES算法对任意文件进行加密和解密的功能。结果表明,该方案对任

2017-12-12 14:43:55 0

0 。DES(Data Encryption standard)加密算法在成为加密标准到今天,经历了长期的考验。实践证明DES算法的安全性是能够满足大部分的安全要求的。

2018-06-06 10:00:00 17

17 介绍了3DES 数据加密算法(DDA)的原理,针对利用FPGA 硬件实现3DES 算法,给出了一种可进化IP 核的具体设计思想,采用可重构电路节省器件内部资源,并采用有限状态机设计技术从而实现数据

2020-01-16 10:58:00 17

17 选用M+12 Timing 0ncore Receiver GPS模块、CvcloneⅡ系列EP2C8现场可编程逻辑门阵列(FPGA)、10MHz高精度恒温晶振等设计硬件电路,实现GPs时钟

2021-02-03 16:25:59 21

21 基于FPGA和DSP的机载图形显示系统

2021-06-08 10:48:08 36

36 【导读】本文介绍了 DES 加密原理和作用,和 golang 中 DES 加密解密机制的相应实现。 概念理解 DES是以64比特的明文为一个单位来进行加密,并生成64比特的密文。由于它每次只能处理

2021-08-23 10:06:39 6241

6241 DES全称为Data Encryption Standard,即数据加密标准,是一种使用密钥加密的块算法。DES加密算法出自IBM的研究,1977年被美国联邦政府的国家标准局确定为联邦资料处理标准(FIPS)

2023-03-07 11:39:41 3834

3834 可有力保障通信、工业、航空航天、国防、核及其他系统的安全性。英国政府的国家网络安全中心(NCSC)根据严格的器件级弹性要求,对采用单芯片加密设计流程的PolarFire FPGA器件进行了审查。

2023-09-05 11:49:53 905

905 电子发烧友网站提供《采用FPGA驱动GPS模块和电子罗盘模块的解决方法.pdf》资料免费下载

2023-10-26 09:02:36 1

1

电子发烧友App

电子发烧友App

评论