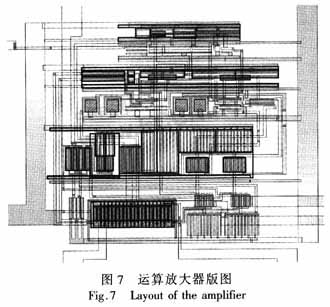

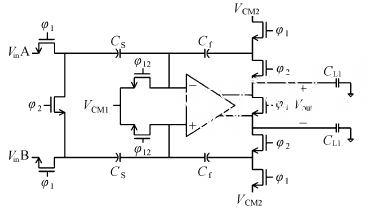

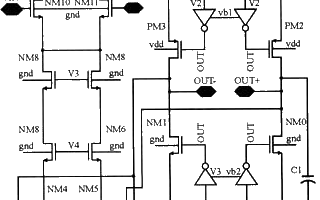

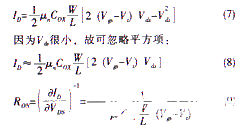

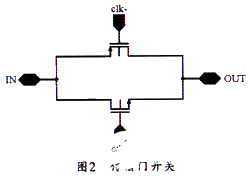

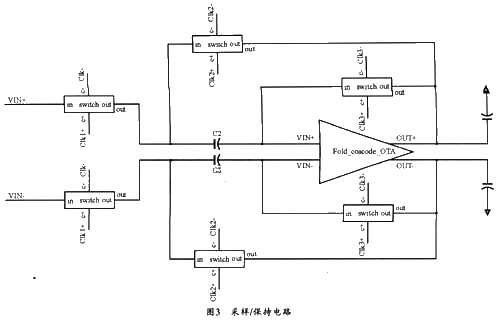

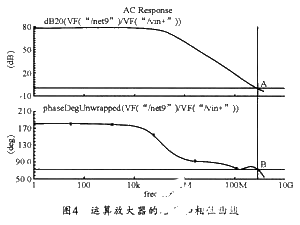

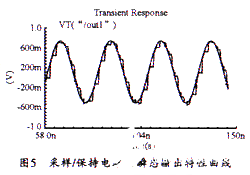

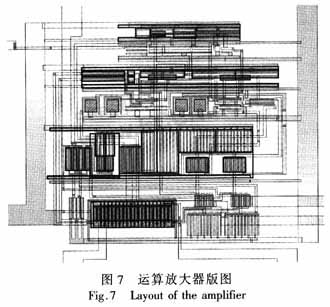

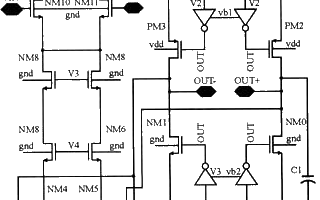

本文在0.35微米N阱工艺的基础上,设计了单电源供电的全差分斩波运放电路,同时,为了减小残余电压的失调, 采用了T/H(跟踪-保持)解调技术,该电路在斩波频率150KHz工作时,输入等效噪声达到

2012-02-03 11:22:58 9905

9905

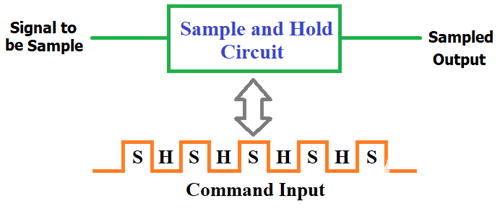

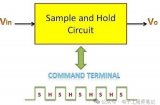

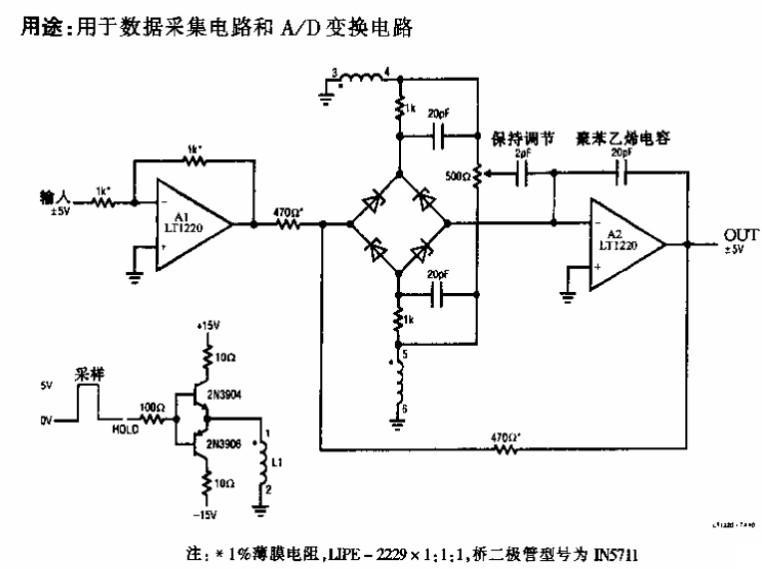

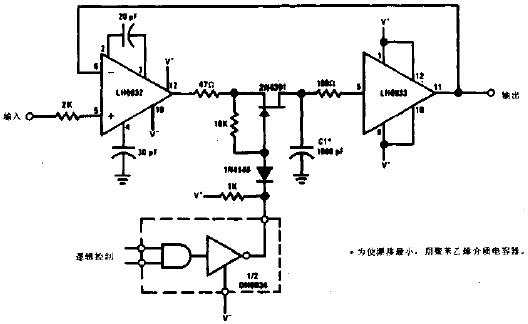

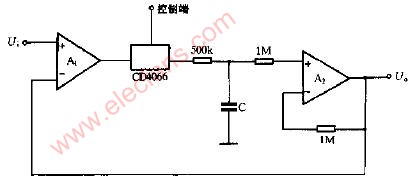

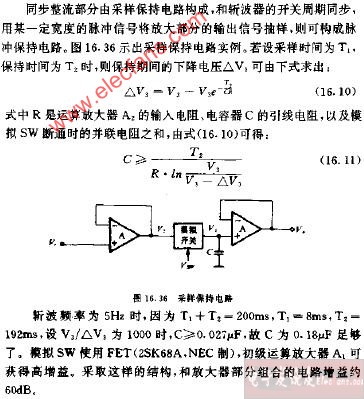

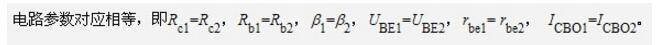

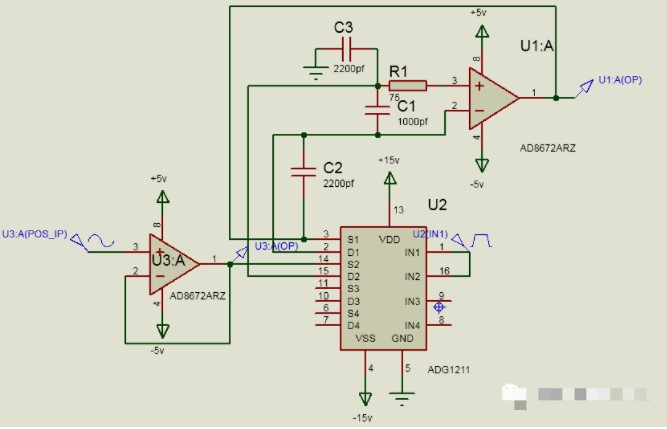

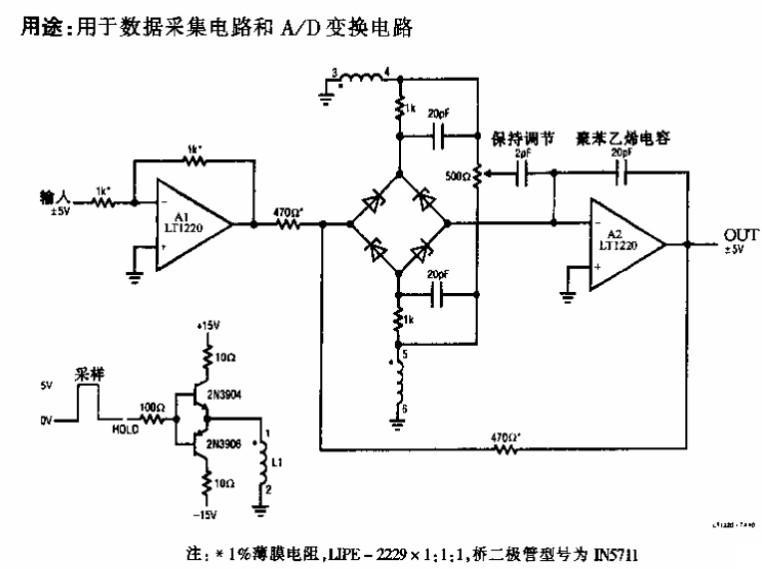

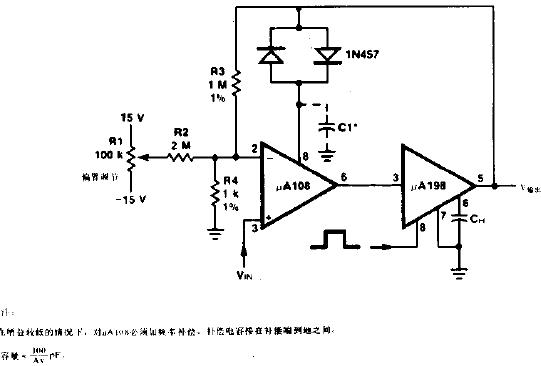

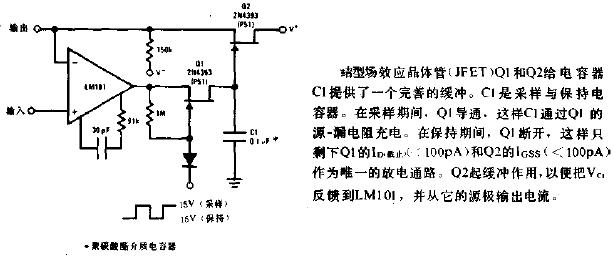

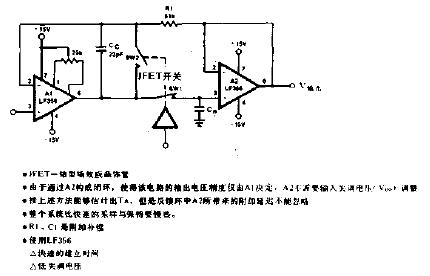

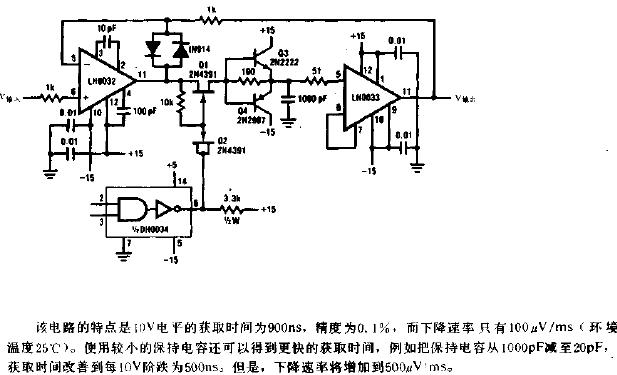

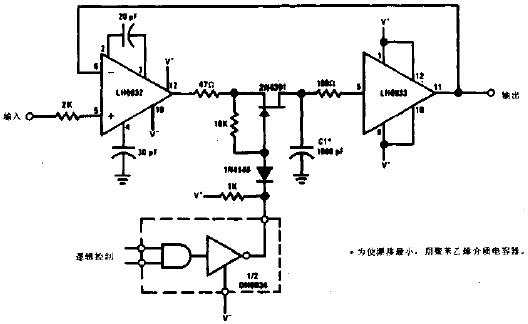

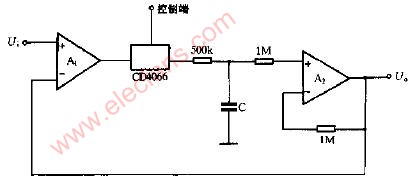

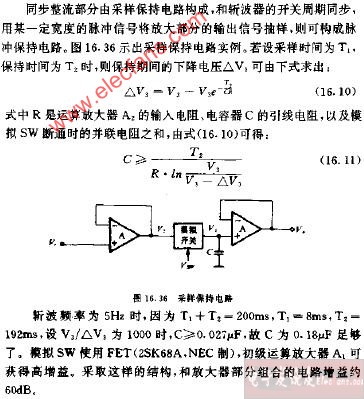

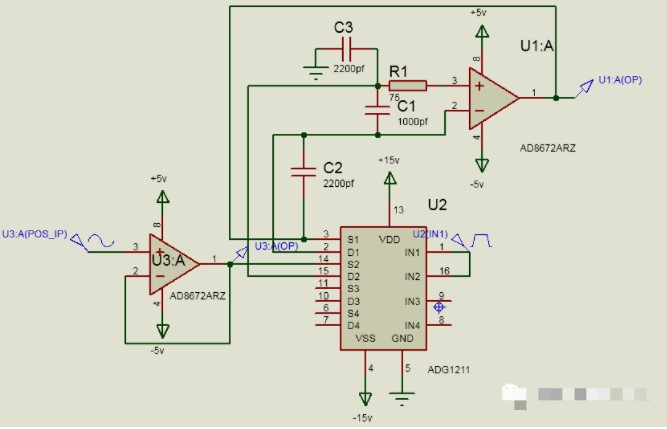

本文主要介绍了采样保持电路图大全(五款采样保持电路设计原理图详解),采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。采样保持电路即为实现这种功能的电路。

2018-02-23 09:59:44 106431

106431

主要是关于:采样保持名词解释、采样保持电路工作原理、采样保持电路功能、采样保持电路作用以及采样保持电路设计。

2022-10-20 09:37:34 8545

8545 采样保持电路从模拟输入信号中获取样本并保持特定时间段,然后输出输入信号的采样部分。该电路仅对几微秒的输入信号进行采样。

2022-11-08 17:29:18 10770

10770

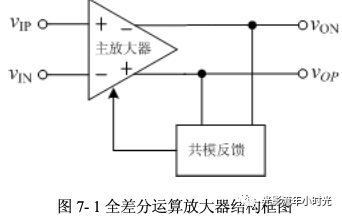

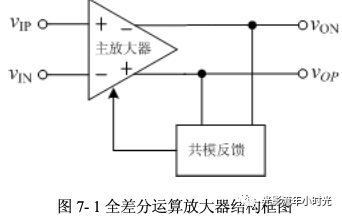

全差分运算放大器就是一种具有差分输入,差分输出结构的运算放大器。

2023-09-25 17:34:56 16365

16365

采样和保持电路是一种电子电路,它创建作为输入的电压样本,然后将这些样本保持一定的时间。采样保持电路对输入信号产生采样的时间称为采样时间。

2024-04-12 10:03:23 4811

4811

AD9254-150EBZ,用于AD9254的评估板是单芯片,1.8V单电源,14位,150 MSPS模数转换器(ADC),具有高性能采样保持放大器(SHA)和 - 芯片电压参考。宽带宽,真正的差分

2020-07-22 11:46:37

求51单片机差分采样电路(采集电流互感器输出的交流信号)。我直接将电流互感器的采样电阻两端接到单片机的两个I/O口,才样很不准,那位高手有跟好的电路麻烦推荐下

2014-06-16 11:03:59

DC745A,演示电路采用LTC2433-1,16位高性能DS模数转换器。 LTC2433-1具有0.12 LSB线性度,0.16 LSB满量程精度,5mV失调和1.45mV RMS噪声。输入

2020-03-11 09:40:46

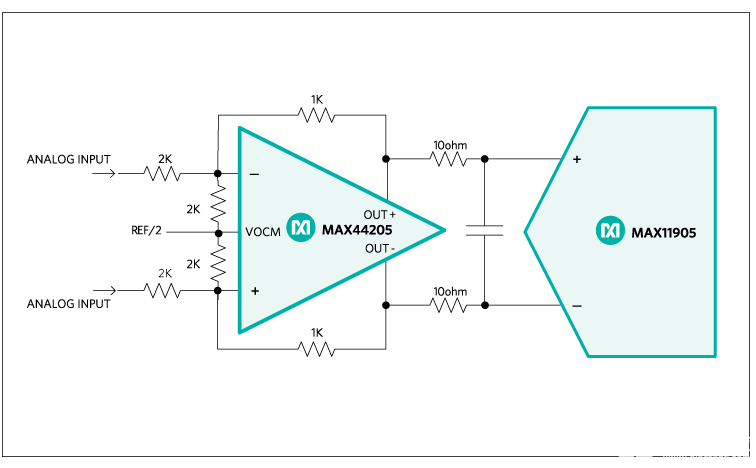

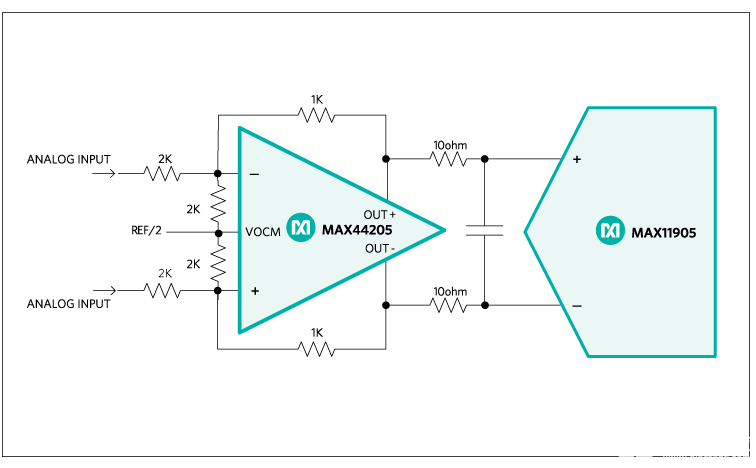

本应用笔记介绍了输入端相同值电阻的不同容差如何改变全差分ADC的THD性能。电阻器的成本随着容差的每个较低增量而显着变化 概观该MAX11905是一个20位全差分SAR模拟数字转换器(ADC),在

2018-12-17 22:13:40

HMC661LC4B是一款SiGe单芯片、全差分、单列、采样保持(T/H)放大器,面向宽带信号采样系统提供前所未有的带宽和动态范围性能。此款放大器在18 GHz的带宽范围内提供精密的信号采样,在DC至超过5 GHz的输入频率范围内具有9/10位线性度、1.05 mV噪声和

2019-07-16 03:33:37

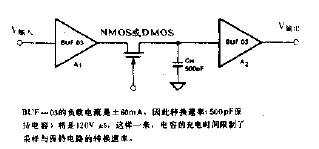

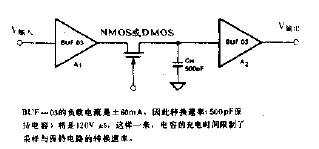

以减小开关漏电流的影响;在高速场合也可用晶体管、场效应管来作为开关。然而,一般目前常采用性能优越的集成式采样/保持器。随着大规模集成电路技术的发展,目前已生产出多种集成采样/保持器,如可用于一般要求

2018-01-08 14:23:45

检测电路,以适应于不同电机及不同控制方式的要求;同时由于采用了高性能的MCU,更多类型的通信接口可被灵活应用,如:URAT、CAN、RJ45等。

2019-07-09 08:24:02

DC586A,LTC2431CMS演示板,MS10封装的20位差分ADC,演示电路采用20位高性能模数转换器LTC2431。 LTC2431具有3ppm线性度,10ppm满量程精度,1ppm偏移和0.56ppm噪声

2020-03-12 10:39:25

采样保持放大器经常用于信号处理系统中,AD781是Analog Devices公司生产的快速采样保持放大器,它具有采样时间短、下降速度慢、保持误差小、功耗低、功能齐备、体积小等优点,十分适用于高速

2023-11-23 07:05:20

AD9233-105EBZ,用于评估AD9233的评估板,12位,105 MSPS,1.8V模数转换器,具有高性能采样保持放大器(SHA)和片内基准电压源。该产品采用多级差分流水线架构,具有输出纠错

2019-11-11 07:16:29

DC1384A-A,演示电路采用带有SPI接口的16位高性能差分模数转换器LTC2452。输入是双极性的,具有Ref-to Ref +范围。该调制器的专有采样技术将平均输入电流降低至比典型Δ-ΣADC低50nA的数量级。 LTC2452采用8引脚,3x2mm DFN封装,具有易于使用的SPI接口

2020-05-05 14:02:15

OTDR信号采集采用两级THS4541全差分可以吗,是否有参考设计?

2024-07-30 08:13:50

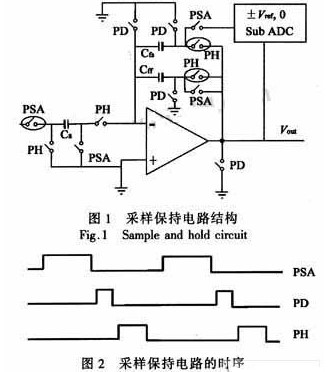

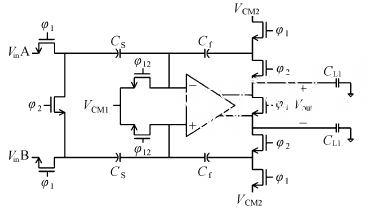

稳定时间短等优点。适用于高速的流水线ADC.同时采用了下极板采样技术和全差分结构。全差分结构可以消除电路的共模失调误差,抑制衬底噪声。下极板采样技术的应用则可以几乎完全抑制了在采样时刻由于开关的电荷

2018-10-08 15:47:53

提问:我们可以使用仪表放大器生成差分输出信号吗?随着对精度要求的不断提高,全差分信号链组件因出色的性能脱颖而出。这类组件的一个主要优点是可通过信号路由拾取噪声抑制。由于输出会拾取这种噪声,输出经常

2021-10-15 06:30:00

全差分仪表放大器具有其他单端输出放大器所没有的优势,它具有很强的共模噪声源抗干扰性,可减少二次谐波失真并提高信噪比,还可提供一种与现代差分输入ADC连接的简单方式。低功耗全差分仪表放大器电路怎么设计?

2021-04-06 08:11:07

输出+2.5V,经过OPA350驱动后VREFP=2.5V,VREFN=0V,这样VREF=2.5V。我现在想用signal和REF做差分,接到1258的差分通道1,1258以差分方式采样,运放采用纯差

2025-01-23 08:38:51

AD9246-105EBZ,AD9246评估板是单片,1.8V单电源,14位,105 MSPS模数转换器,具有高性能采样保持放大器(SHA)和片内基准电压源。该产品采用多级差分流水线架构,具有输出纠错逻辑,可在105 MSPS数据速率下提供14位精度,并确保在整个工作温度范围内无失码

2020-07-20 10:16:13

如何使用全差分放大器实现单端至差分转换?如何使用有源匹配电路改善宽带全差分放大器的噪声性能?

2021-04-13 06:40:17

的线性性能;采用全差分结构、底极板采样来消除电荷注入和时钟馈通。该采样保持电路能够直接应用于高速高精度模/数转换器等各种高速模拟系统中。

2021-04-20 06:45:33

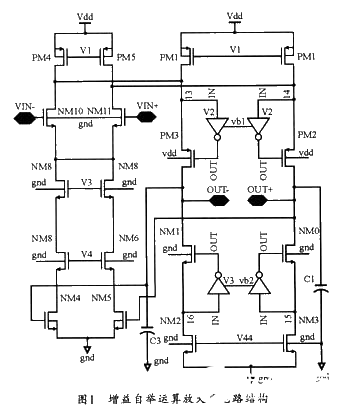

为了解决传统S/H电路失真大和静态工作点不稳定的问题,采用0.25 μm BiCMOS工艺,设计了一款高速率、高精度的10位全差分BiCMOS S/H电路。文中改进型自举开关电路和双通道开关电容共模反馈电路(CMFB)设计具有创新性。

2021-04-21 06:24:21

利用差动放大器实现低损失、高性能全波整流器的电路是什么样的?

2019-08-02 07:00:51

本文介绍了一种基于SiGe BiCMOS、开环全差分结构的SH。采样速率可以达到800 Msps,采样精度可以达到8 bit,能够适应无线通信领域的要求。

2021-04-14 06:36:13

请问各位关于全差分SARADC下极板采样的逻辑控制,有没有相关了文章介绍的比较详细啊,求推荐,感激不尽!

2021-06-25 07:25:37

本文介绍了一种基于SiGe BiCMOS、开环全差分结构的SH。采样速率可以达到800 Msps,采样精度可以达到8 bit,能够适应无线通信领域的要求。

2021-04-08 06:07:31

外行不懂模电,请教个问题!感谢大家如果采用输出为0-5A的电流互感器,下图差分电路中,采样电阻R应该选用多大阻值的?

2022-09-22 16:25:27

采样保持电路的结构分为哪几种?如何去设计运算放大器?描述自举开关是如何实现的?怎样对运算放大器进行仿真验证?

2021-04-20 06:59:17

在阅读数据手册时,他给出的输入电路要求为必须采用差分输入,但是现在我的前级输出单端的,所以能不能直接将AD的差分输入负极接地,正极接输入形成一个单端输入这样的结构。

2024-11-15 07:36:25

请问ADS6422这个差分输入的采样保持电路中的Ron有什么用呢?采样频率对采样保持得到的电压及其精度有什么影响呢?

2024-11-25 07:57:55

差分信号适合于需要大信噪比、高抗扰度和较低二次谐波失真的电路,例如高性能ADC驱动和高保真度音频信号处理等应用。《模拟对话》曾刊载过一篇相关文章——“多功能、低功耗、精密单端差分转换器”1,其中

2019-04-14 08:30:01

采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。采样保持电路即为实现这种功能的电路

2011-07-28 10:21:06

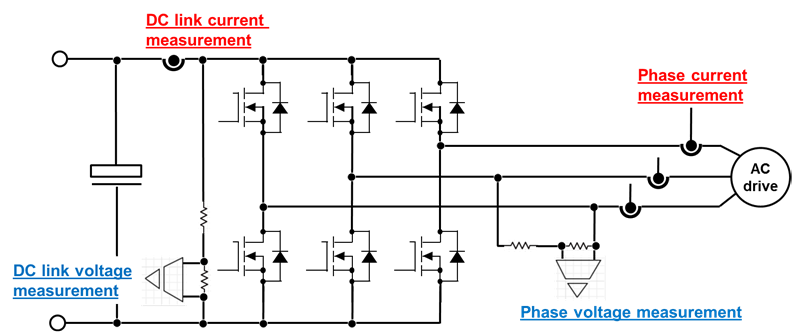

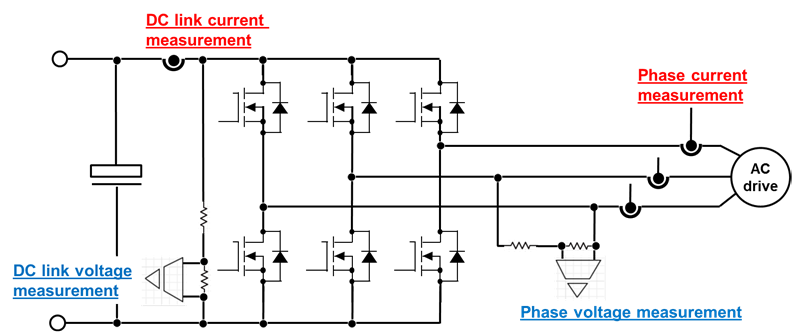

传感器与电流互感器, 分流电阻器加隔离运放的方案在线性度、带宽和漂移等性能更好。在电机驱动器中,通常会在功率板用隔离采样运放来对相电流,母线电流和母线电压等进行采样,如下图1: 图1 电机驱动器电压电流采样 下图所示,是使用隔离运放来进行相电流采样的常见结构和内部原理图。图2…

2022-11-07 07:19:42

引言影响接收机速度、性能的一个重要电路单元AD转换部分就显得愈发重要。影响接收机速度、性能的一个重要电路单元AD转换部分是非常重要的,而AD转换前端的采样保持电路又直接关系到AD芯片的转换

2021-07-27 06:12:53

介绍采用AD7672和采样保持放大器获得200MHz的采样率:

2009-06-11 14:37:50 30

30 DS1843是一款采样/保持电路,对于电路板空间受限的快速信号采集非常有用。该器件带有差分、高速切换电容输入采样级、失调调零电路和输出缓冲器。DS1843优化用于光纤线路传输(OLT

2009-11-16 17:54:52 131

131 介绍了一种利用双采样技术的高性能采样/保持电路结构,电路应用于10bits50MS/s 流水线ADC 设计中。电路结构主要包含了增益自举运算放大电路和栅压自举开关电路。增自举运算放大

2009-12-26 16:39:10 28

28 对采样保持电路的原理、工作方式、电路的参数以及保持电容器电容量大小的选定进行了分析。关键词:采样;保持;电容

Abstract:This paper analyses the principle of~mapling a

2010-04-13 08:54:05 64

64 简要讨论了电荷泵中的非线性问题及常用的一些结构,提出了一种改进的基于负反馈的全差分电荷泵结构。它由充电/ 放电模块,共模反馈电路以及偏置电路组成。负反馈结构使得输入

2010-04-23 08:41:13 15

15 在常规高速采样保持电路(SHC)中采样速率主要受到保持电容器被充电到输入电平期间的采集时间的限制。本文描述一种新的电路结构,其采样速率仅仅由保持时间决定。就时钟馈通而

2010-04-28 09:57:45 63

63 一种新型高速采样保持电路摘要 : 本文提出了一种新型的基于运算放大器的开关电容采样保持电路结构。采用速度补偿解决了高速高分辨采样保持电

2010-05-24 15:44:21 49

49 一种100MHz采样频率CMOS采样/保持电路

摘要: 设计了一种高速采样保持电路。该电路采用套筒级联增益自举运算放大器,可在达到高增益高带宽的同时最大程度地减

2010-05-24 15:52:26 39

39 全差分驱动器释放高速ADC性能潜力

智能化集成

设计应用

结论

2010-09-15 16:06:15 13

13 采样保持电路

2009-01-02 01:06:50 1821

1821

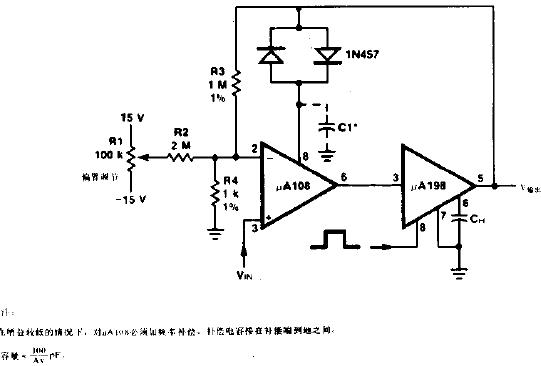

×1000采样与保持电路图

2009-04-09 09:23:26 1058

1058

采样与保持电路图

2009-04-09 09:23:54 1758

1758

低漂移采样与保持电路图

2009-04-09 09:24:27 906

906

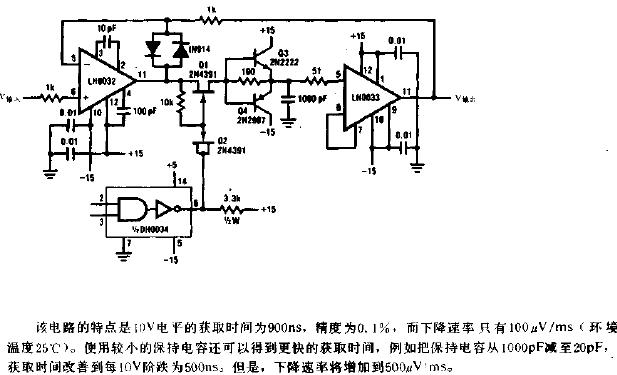

高精度采样与保持电路图

2009-04-09 09:25:48 1736

1736

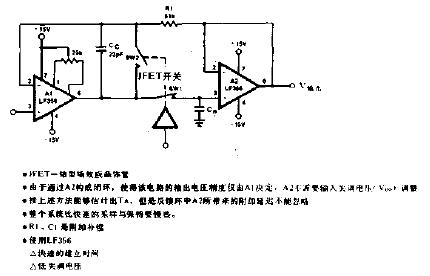

高速采样与保持电路图1

2009-04-09 09:26:15 846

846

高速采样与保持电路图2

2009-04-09 09:26:58 851

851

高速采样与保持电路图3

2009-04-09 09:27:24 767

767

采样保持电路(S/H)原理

A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。为此,在ADC前加入采样保持电路,如图8-30所示。采样保持电路有两种

2009-04-12 12:01:35 26483

26483

采样信号保持电路图

2009-05-08 14:28:55 1211

1211

采样保持电路图

2009-07-08 11:40:58 1122

1122

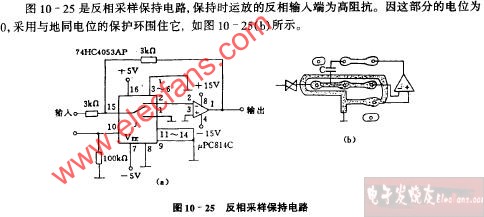

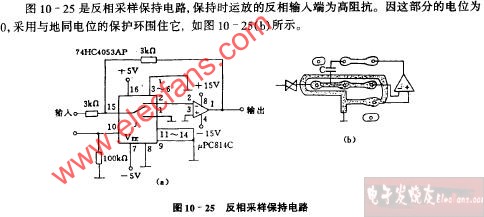

反相采样保持电路图

2009-07-17 14:43:55 821

821

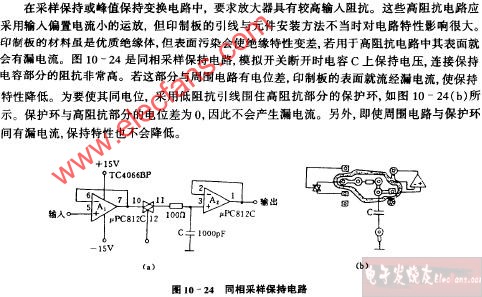

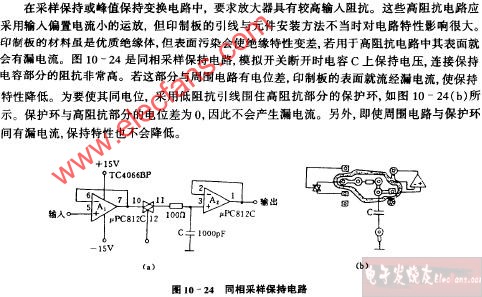

同相采样保持电路图

2009-07-17 14:51:13 901

901

DS1843 高速采样/保持电路

DS1843是一款采样/保持电路,对于电路板空间受限的快速信号采集

2009-11-16 17:57:24 1754

1754

采样时间为20US的中速采样和保持电路

电路的功能

所谓采样和保持

2010-05-05 15:53:51 1931

1931

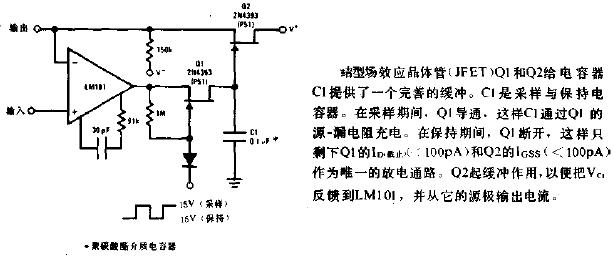

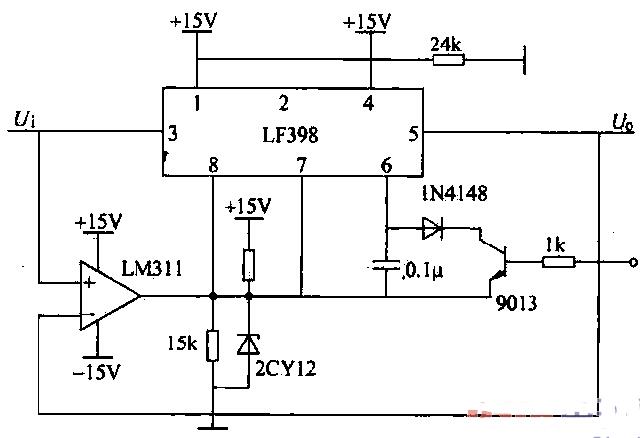

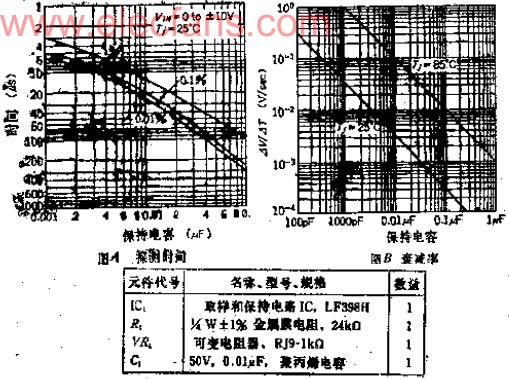

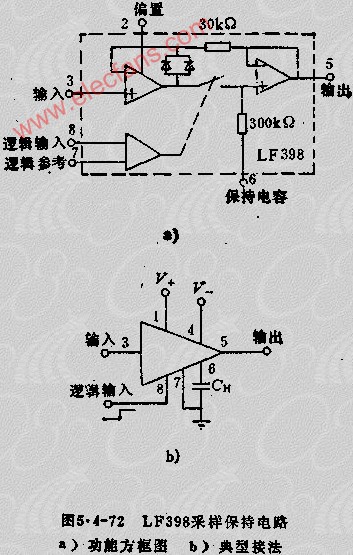

单片采样保持电路

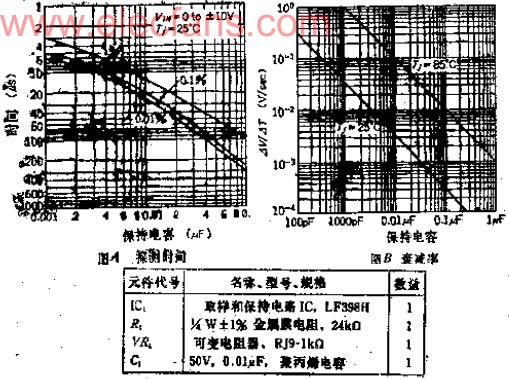

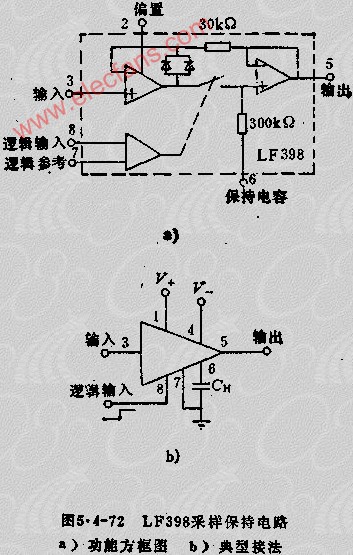

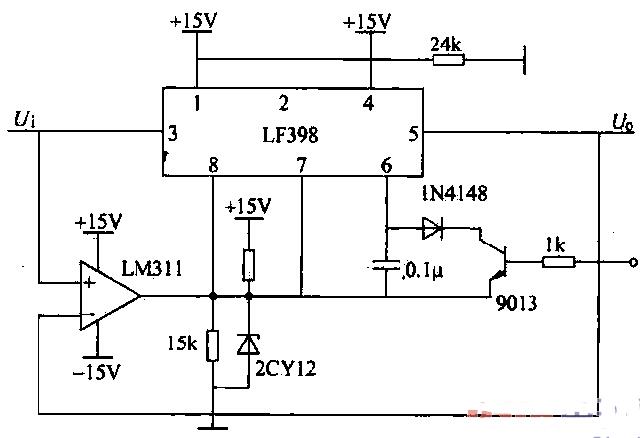

现在已有多种单片采样保持电路的产品。图5.4-72是单片采样保持电路LF398。该电路在作为单位增益跟随器使用时,其DC增益精度为0.002%到0.01

2010-05-23 18:19:30 3544

3544

本文采用一种全差分电荷转移型结构的采样保持电路,这种结构可以很好地消除与输入信号无关的电荷注入和时钟馈通;通过底极板采样技术,消除与输入信号相关的电荷注入和

2010-06-07 14:46:26 3403

3403

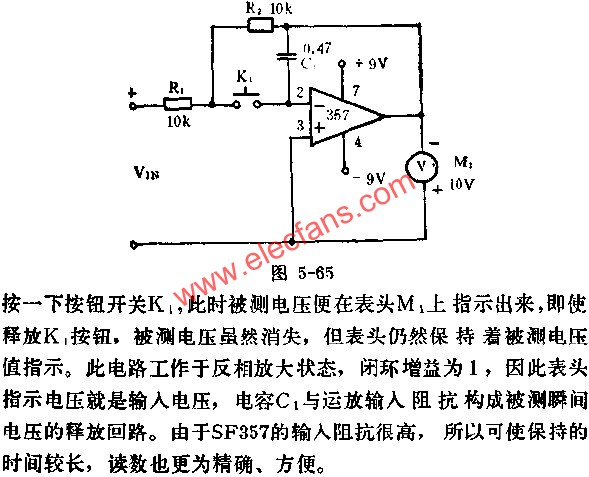

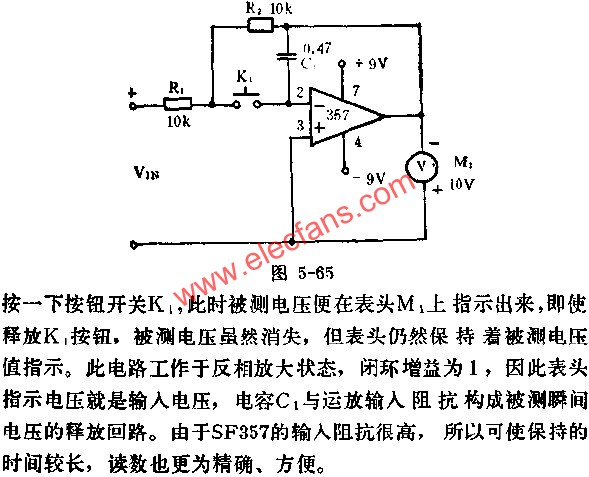

图中所示是用SF357运放组成的电压采样保持电路.这种电压采样保持电路可以方便地观察任一时间内的被测瞬间电

2010-10-08 12:53:57 12995

12995

另外,如果 信号 调理电路 和 传感器 之间 的ADC 时,该 电路可 影响 ADC的输入 结构的选择。 有些 ADC可 配置的, 允许 选择 之间 单 端或 伪差分 输入结构 ( 器MAX186 , MAX147 ),而其他 允许 在单 端或 全差分 选择( MAX1298 , MAX1286 )。

2011-02-12 17:27:46 265

265 许多高性能ADC设计均采用差分输入。全差分ADC设计具有共模抑制性能出色、二阶失真产物较少、直流调整算法简单的优点。

2011-12-05 14:50:45 8625

8625

本文在0.35微米N阱工艺的基础上,设计了单电源供电的全差分斩波运放电路,同时,为了减小残余电压的失调, 采用了T/H(跟踪-保持)解调技术,该电路在斩波频率150KHz工作时,输入等效

2011-12-26 10:06:13 7040

7040

采用多级噪声抵消技术的CMOS全差分LNA设计_姚春琦

2017-01-07 16:06:32 5

5 摘要 :本文介绍了一种以采样/ 保持器 L F398 芯片为主要器件的峰值保持电路。该电路具有结构简单、调试方便、性能优良等优点 ,可广泛应用于各种脉冲分析系统。

2017-11-04 10:07:35 28647

28647

设计了一种基于二极管桥的两级全差分跟踪保持电路, 两级模块由独立的时钟控制, 可以各自工作在跟踪模式。芯片采用 1 Lm GaAs HBT 工艺实现, 芯片大小为1. 8 mm2 mm , 功耗2.

2017-11-06 15:42:59 1

1 本文开始介绍了差分放大电路的概要和差动放大电路的组成,其次阐述了差分放大电路的特性和差分放大电路的基本状态,最后介绍了差分放大电路的作用以及它的作用。

2018-03-21 14:38:25 120805

120805

ADS832是一种高性能的16位,600千赫的A/D转换器,具有全差分、伪双极输入。该装置包括具有固有采样和保持的16位基于电容的SAR A/D转换器。

2018-05-15 16:47:21 2

2 LME497是一种超低失真,低噪声,高摆率全差分运算放大器优化和完全指定的高性能,高保真应用。

2018-05-16 15:52:03 16

16 的模块,采样保持电路的性能直接决定了整个ADC的性能,在以上系统中对功耗的要求十分严格。本设计在实现高速高精度采样保持功能的同时,还实现了MDAC功能,这样既能降低ADC功耗又能减少芯片面积。

2019-06-13 08:19:00 7198

7198

采样保持电路(S/H)是数据采集系统尤其是模数转换器(A/D)的一个重要组成部分。近几十年来无线通讯的迅速发展,使得数据的传输速率越来越快。复杂度不断提高的调制系统和电路使得模数转换器(ADC)的采样频率达到射频的数量级,与此同时,模数转换器的精度也超过12位以上。

2019-12-18 07:54:00 6294

6294

峰值电压采样保持电路:峰值电压采样保持电路如图12-50所示。峰值电压采样保持电路南一片采样保持器芯片LF398和一块电压比较器LM311构成。LF398的输出电压和输入电压通过LM3J1进行比较t当U.》Uo时.

2020-01-21 17:21:00 17745

17745

采样/保持电路是模数转换器的重要组成部分,它的性能决定着整个A/D转换器的性能。随着科学技术的发展,系统对A/D转换器的速度和精度要求越来越高,因此,设计一个高性能的采样/保持电路就显得尤为重要。

2021-03-23 10:34:50 7826

7826

LTC6405演示电路-采用简化混频器和ADC型号的全差分ADC驱动器

2021-06-08 16:17:06 5

5 220MHz高性能差分振荡器SiT9121

2021-09-10 16:19:49 5

5 应用于电机驱动的隔离运放单端和差分输出对采样性能的影响

2022-10-31 08:23:23 11

11 本应用笔记解释了输入端相同值电阻的不同容差如何改变全差分ADC的THD性能。电阻器的成本随着容差每降低一次而显著变化

2023-01-12 09:38:23 2220

2220

在可编程逻辑控制器(PLC)输出模块中存在每通道采样保持架构,它采用开关电容和缓冲器作为采样保持放大器(SHA),以便存储单通道高性能DAC的选定输出样本。这些样本通过-一个模拟开关或多路复用器在不同保持电容之间切换。

2023-03-17 15:22:45 3272

3272

本文介绍在应用电机驱动器中,采用隔离运放的系统架构和TI明星产品。涉及了相关电路设计和外部信号调理与MCU的配合。结合后级ADC,深入讨论了隔离运放单端结构输出和差分结构输出对整体采样性能的影响,提供了相应的分析和建议。

2023-03-23 09:24:29 6184

6184

差分放大电路原理分析 双差分放大电路的作用 差分放大电路是一种电路结构,采用两个输入信号进行放大,将输入信号的差值作为输出信号。双差分放大电路是其中一种常见的差分放大电路结构,更为稳定可靠

2023-09-04 17:00:14 4857

4857 在高性能交换机中,差分时钟信号(LVDS、CML、HCSL)起着至关重要的作用。这些信号技术具备抗干扰能力强、信号完整性高的特点,广泛应用于高速数据传输和同步。为了确保信号的稳定性、完整性和低抖动特性,差分振荡器必须满足特定的性能要求。本文将详细探讨这些差分时钟信号技术及其对差分振荡器的要求。

2024-05-17 09:00:00 1413

1413

电子发烧友网站提供《OPA1632高性能、全差分音频运算放大器数据表.pdf》资料免费下载

2024-06-05 13:00:33 0

0 电子发烧友网站提供《OPA1633高性能、全差分音频运算放大器数据表.pdf》资料免费下载

2024-06-05 09:40:14 0

0 恒流源差分放大电路是一种广泛应用于模拟电路设计中的电路结构,具有许多优点。以下是对恒流源差分放大电路优点的分析: 高输入阻抗 恒流源差分放大电路具有非常高的输入阻抗,这是因为差分放大电路的输入端连接

2024-08-02 15:45:41 2538

2538 恒流源差分放大电路是一种在模拟电子学中广泛使用的电路结构,它利用恒流源的特性来提高差分放大器的性能。这种电路在许多应用中都非常有用,例如在高精度测量、信号处理和传感器接口中。 1. 恒流源差分放大

2024-09-03 09:42:38 3000

3000

![]()

![]()

![]()

![]()

![]()

![]()

![]()

电子发烧友App

电子发烧友App

评论