集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-02-01 08:59:17 1179

1179 今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-02-06 11:54:41 6502

6502

今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-07-17 09:03:55 4968

4968

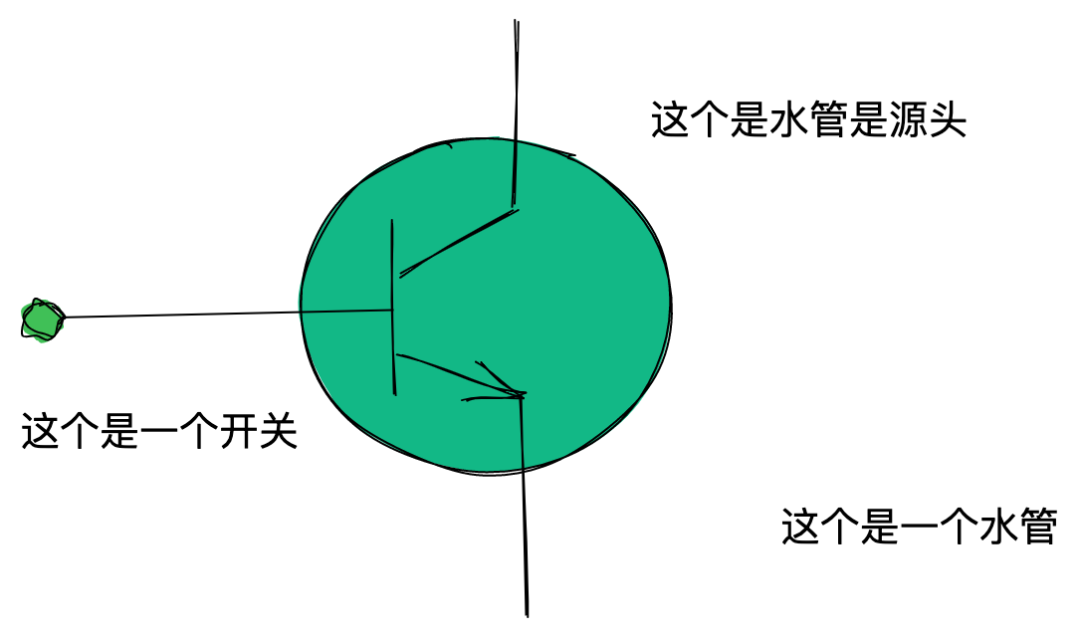

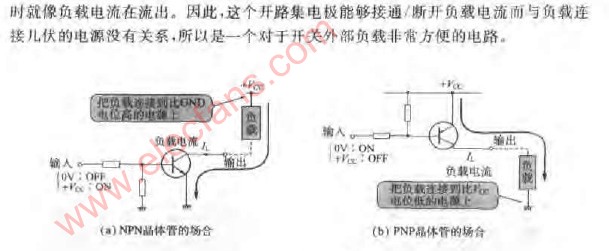

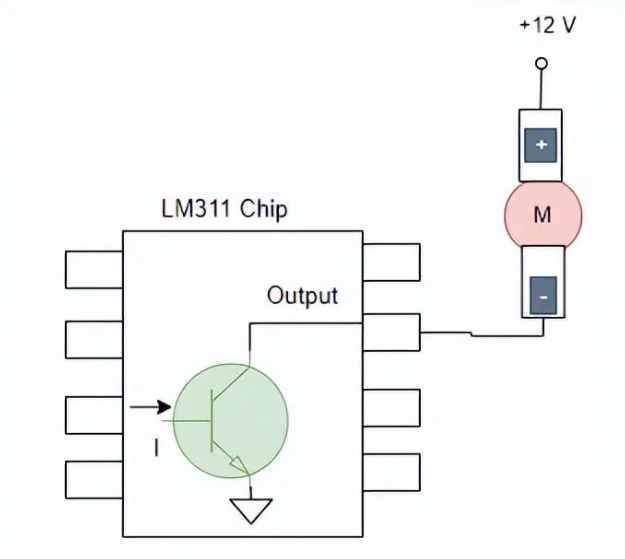

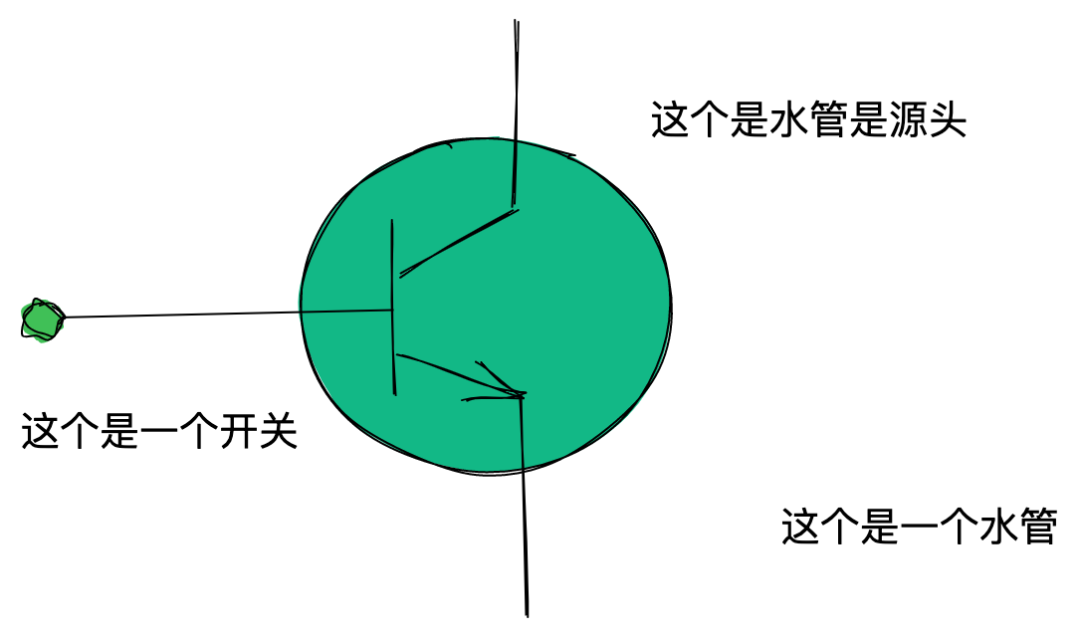

集电极开路就像是一个开关,其一端连接电源或接地。集电极开路电路常用在集成电路的输出,其输出可以根据使用的晶体管类型(NPN型或PNP型)为外围提供灌电流和拉电流能力。

2023-07-21 10:00:28 2686

2686

集电极开路 漏极开路 推挽 上拉电阻 弱上拉 三态门 准双向口

2016-06-02 16:22:21

时给引脚或线路节点一个固定的默认的电平。上拉电阻有时还用来增加输出引脚的驱动能力。当所接电阻值比较大时称为弱上拉或弱下拉,否则就是强上拉或强下拉。上拉电阻应用比较普遍,大部分OC或OD输出都需要接上拉电阻。单片机的大部分I/O引脚也配备了弱上拉电阻。

2019-05-20 11:15:28

1、集电极开路输出上拉电阻电路为什么会速度降低和噪声变大?在此基础出引出了三态门?

2、多集电极开路上拉电阻输出实现了线或结构,有高为低,全低为高。那么什么电路结构可以实现线与结构,射极跟随,推挽,互补或者其他简单输出电路?

2024-01-28 16:32:00

CCG5 的 VBUS_C_CTRL 引脚预计是漏极开路输出,但在这种情况下,漏极电流有多大?

2025-05-22 07:06:23

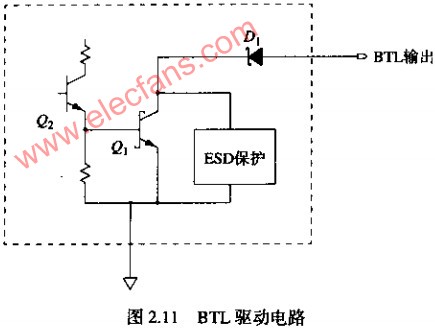

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2022-02-08 06:50:38

TDA7498e的引脚DIAG有何功能,漏极开路诊断输出是什么意思?

2024-10-18 08:01:53

端口需要配置为漏极开路输出或集电极开路输出,请问该怎么用啊没有相关的寄存器可以配置输出模式

2018-08-13 06:41:32

我使用 xmc7100 芯片,使用 pwm 功能时,我需要将引脚配置为开路和漏极输出。 当我没有连接上拉电阻器时,示波器会检测到应该没有波形,但是有波形表明开路和漏极输出配置不成功,为什么不呢? 能否将 pwm 引脚配置为开路和漏极输出?

2024-01-23 06:34:37

本帖最后由 gk320830 于 2015-3-4 23:25 编辑

【经典】集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

2012-07-29 21:17:03

什么是集电极开路(OC)?什么是漏极开路(OD)?

2021-03-10 06:35:21

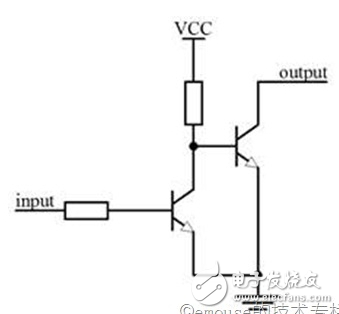

推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉

2021-11-24 07:22:11

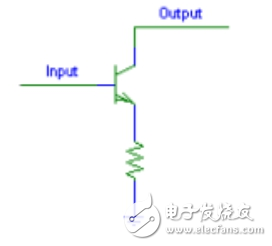

单片机I/O开漏输出详解开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构

2021-11-24 08:11:44

本帖最后由 zhihuizhou 于 2011-11-2 10:20 编辑

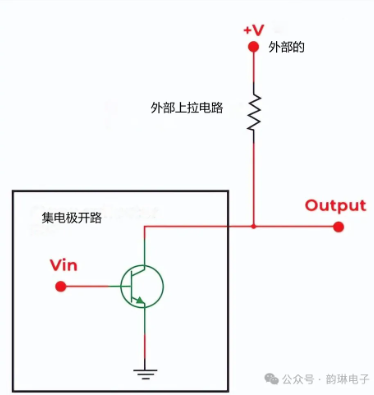

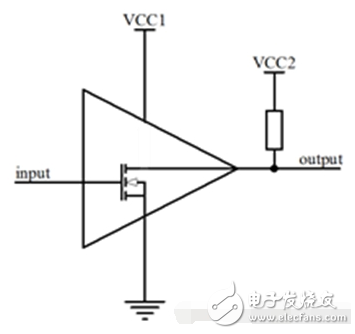

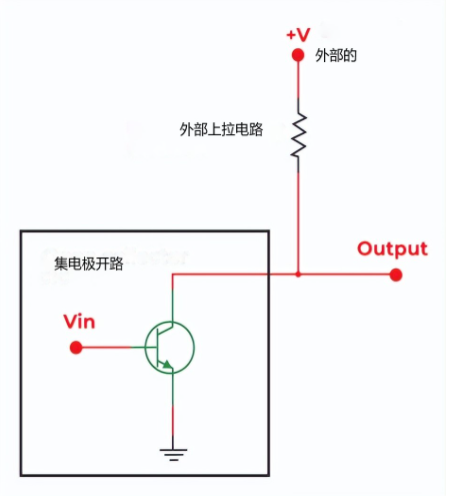

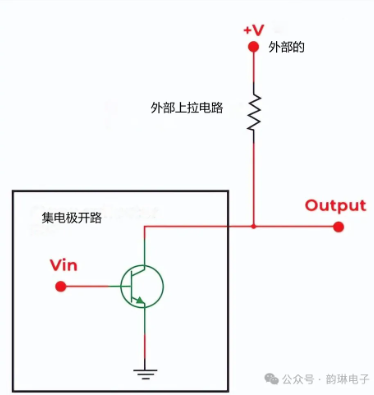

集电极开路、漏极开路、推挽、上拉电阻、弱上拉、三态门、准双向口集电极开路输出的结构如图1所示,右边的那个三极管集电极

2011-11-02 10:20:11

我正在连接一个5V PIC18到2.5V设备。PIC18上的一些输出可以是开路漏极。我非常熟悉漏极/开路集电极输出,并使用了很多年。然而,说明书上的措辞有点麻烦。从PIC18F66K80系列说明书第

2020-05-12 10:28:10

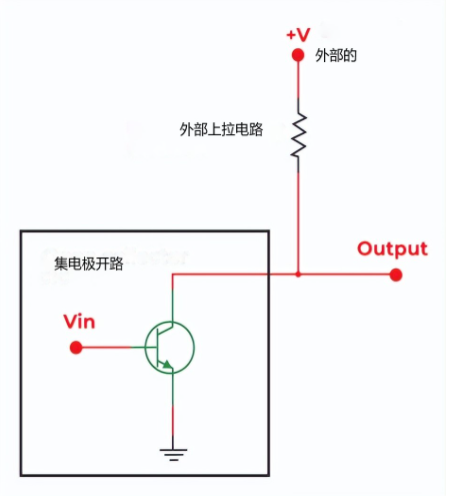

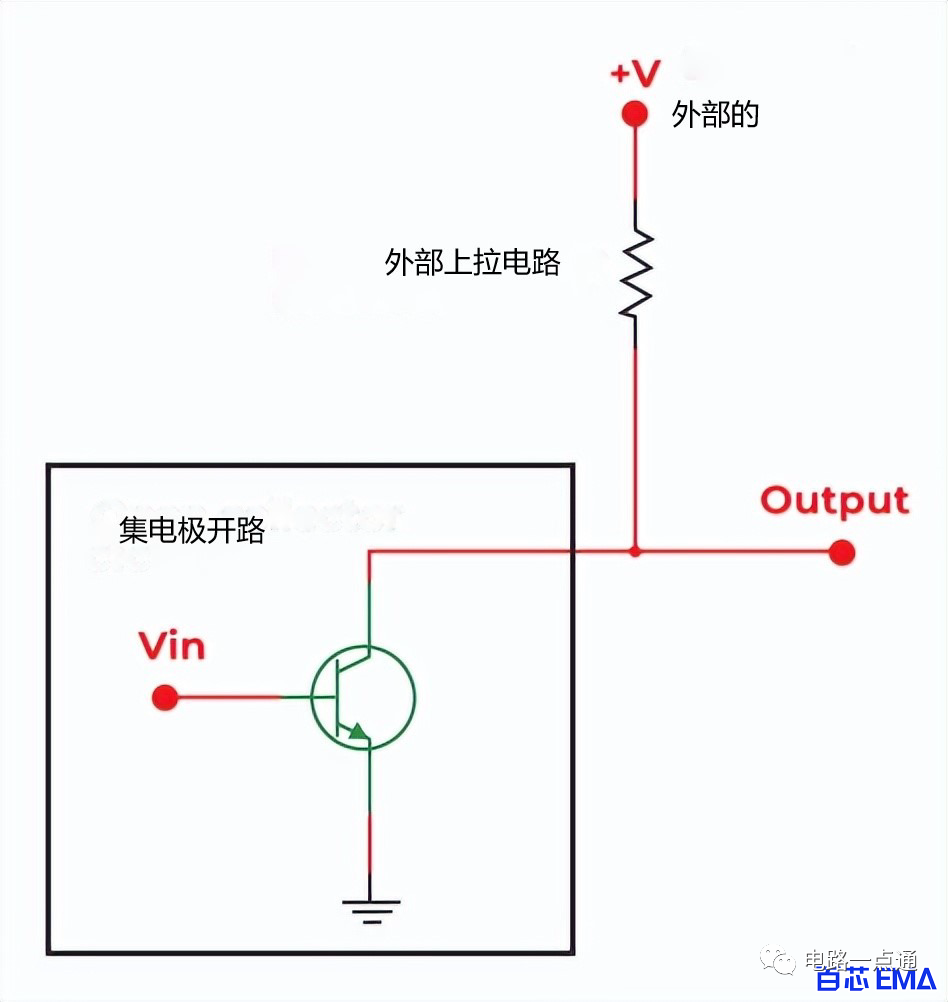

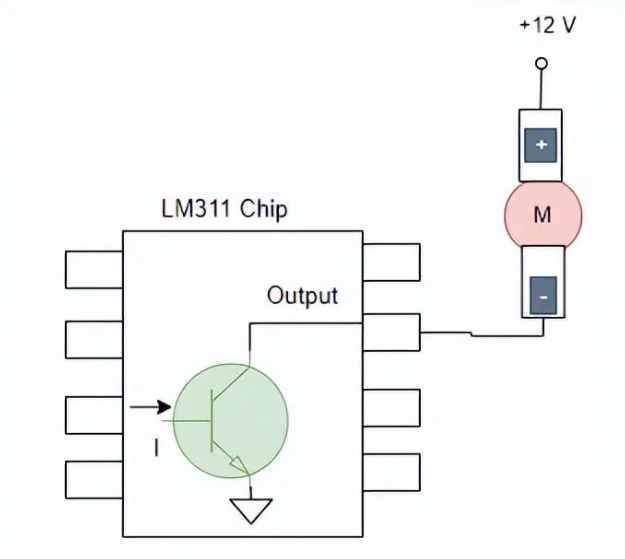

的,Vcc也要在数据手册规定的范围内。集电极或者漏极开路输出引脚是由一个晶体管控制的,当晶体管关闭时,输出引脚为悬空状态(开路或者高阻态)。一个常见的列子就是当N沟道晶体管导通时,输出信号接地,但关断时,输出

2019-04-23 08:00:00

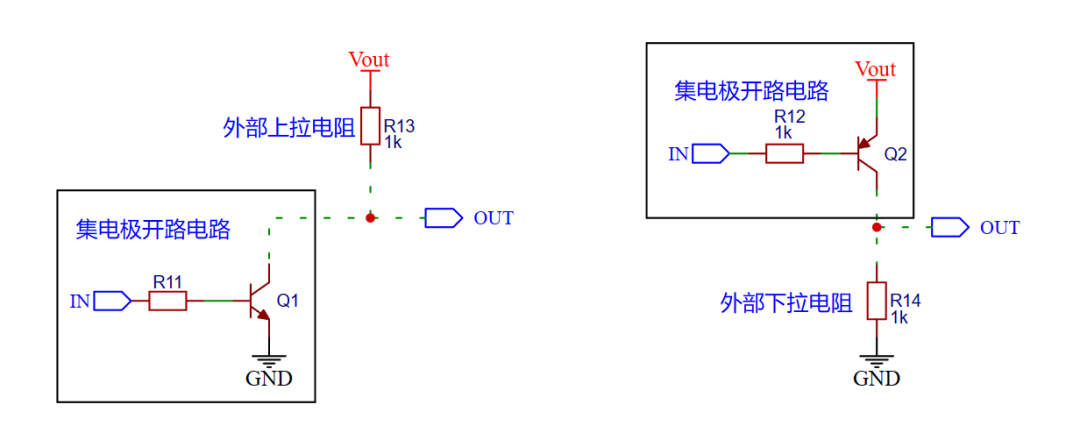

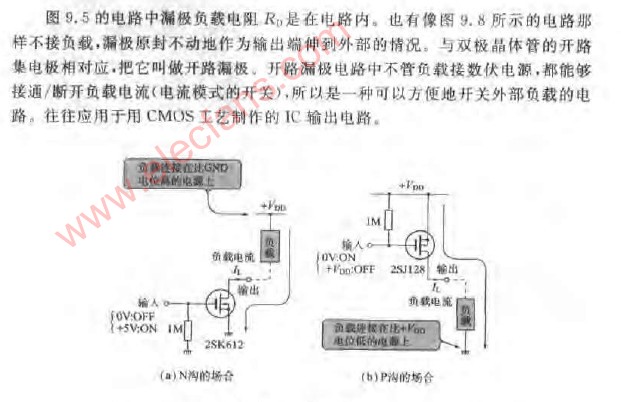

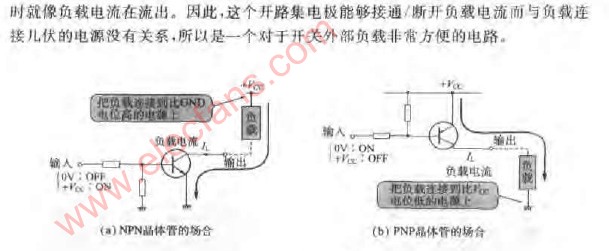

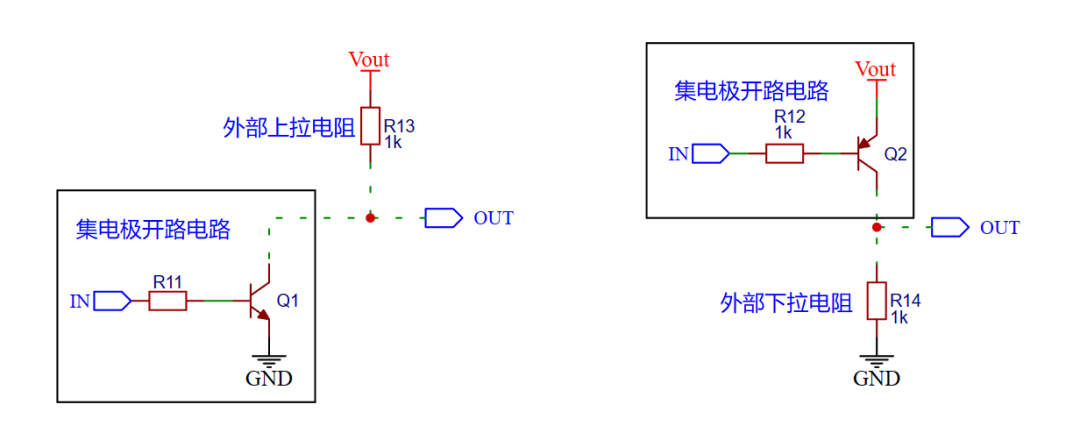

1.什么是源型漏型?什么是上拉电阻?下拉电阻?什么是线驱动输出集电极开路输出,推挽式输出?我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做

2021-11-23 07:22:08

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2021-11-03 06:28:05

当三极管为开路输出时,三极管集电极通过一个负载,再从负载另一端接到电源,-----------------------------通常我们称为集电极开路输出。那么三极管为发射极这边来接负载时,这个

2019-08-01 00:03:31

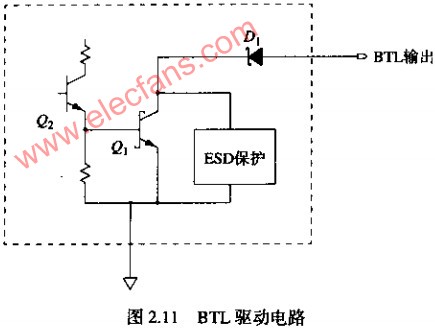

集电极开路门和三态输出门的应用

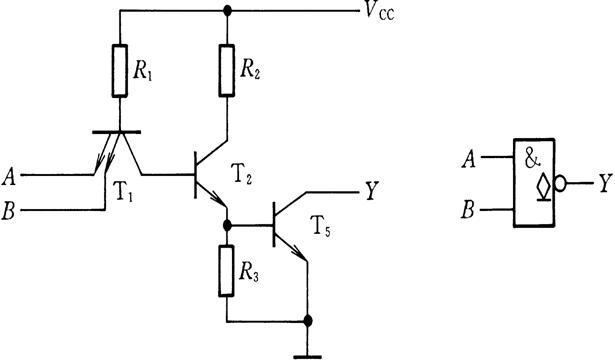

一、 实训目的1.熟悉集电极开路门(OC门)和三态输出门(TSL门)的逻辑功能;2.熟悉用OC门构成线与功能;3.熟悉用TSL门

2009-04-07 23:23:53 59

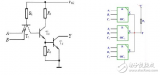

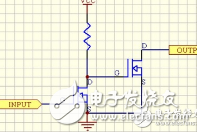

59 我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,

2010-08-14 17:15:55 136

136 集电极开路门

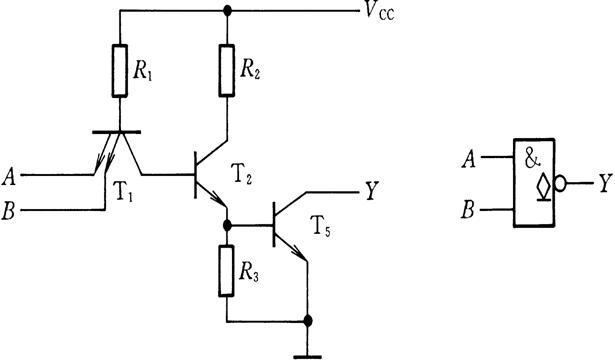

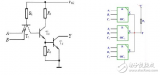

在工程实践中将两个门的输出端并联以实现与逻辑的功能称为线与。 考察下图所示的情况。当将图中所示的两个逻辑门的输出连接在一起,并且

2009-04-07 00:15:19 23791

23791

集电极开路与非门的电路和图形符号

2009-07-15 19:02:06 8515

8515

开路漏极电路图

2009-08-15 16:37:46 1147

1147

开路集电极电路图

2009-08-15 17:27:30 1079

1079

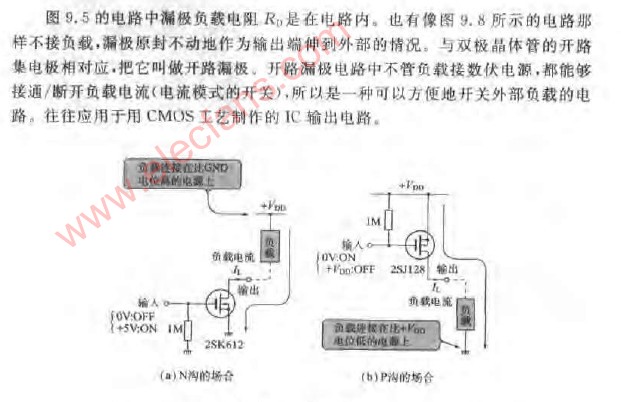

什么是漏极开路(OD)? 对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可

2010-03-04 15:37:00 54078

54078 漏极开路(OD)原理说解

漏极开路(OD),它与集电极开路(OC)是一致的,就是把下图的三极管改成CMOS管就是了。

2010-03-04 15:38:44 3951

3951 集电极开路(OC)/漏极开路(OD)输出的结构

A:我们先来说说集电极开路输出的结构。集电极开路输出的结构如图1所示,右边的那个

2010-03-04 15:41:39 2949

2949 用来计算TTL集电极开路输出电路静态功耗的公式如下:

其中:VT=上拉电阻的有效

2010-06-01 16:17:42 3319

3319

集电极开路_漏极开路_推挽_上拉电阻_弱上拉_三态门_准双向口,感兴趣的小伙伴们可以瞧一瞧。

2016-11-16 18:32:35 0

0 介绍了什么是集电极开路,漏极开路,推挽上拉,电阻弱上拉,三态门。

2017-02-28 22:08:40 2

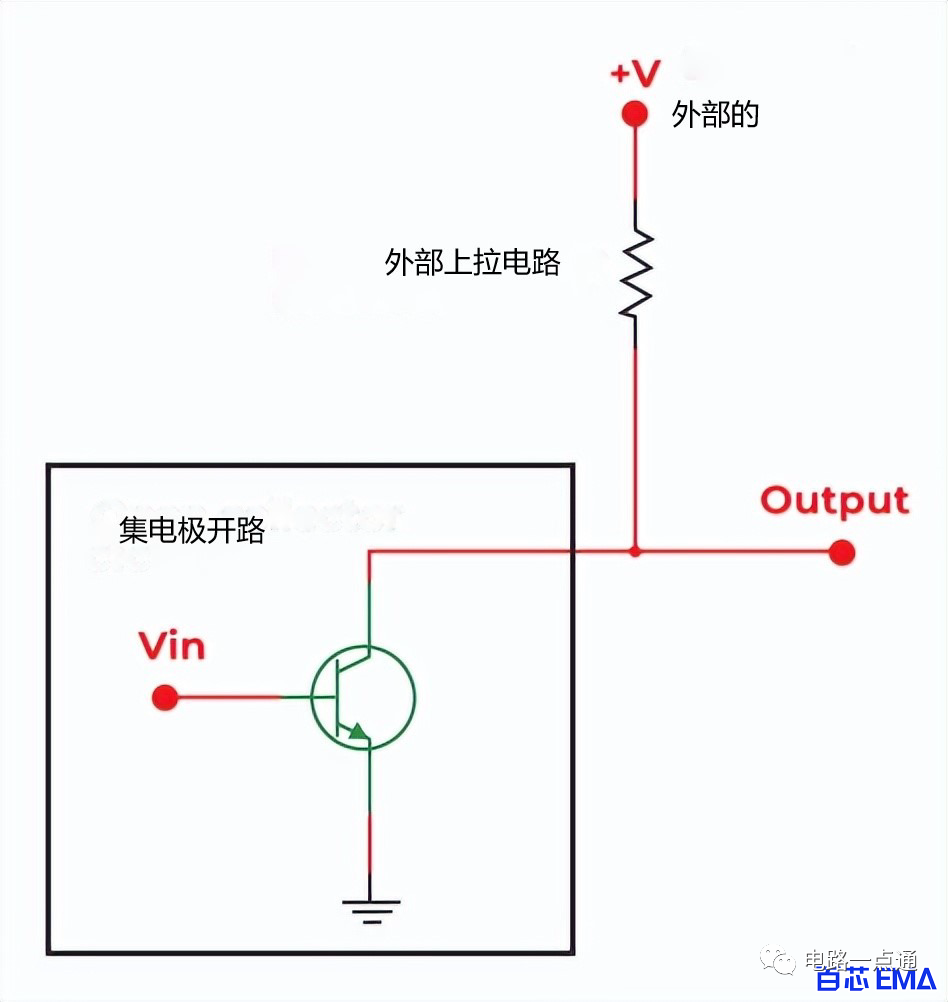

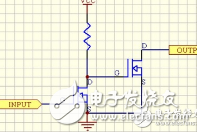

2 三极管导通时,集电极输出低电平;三极管关断时,集电极输出悬空,因此该电路在工作时需要外接负载电阻和电源。只要电阻的阻值和电源电压的数值选择得当,就能够做到既保证输出的高、低电平符合要求,输出端三极管的负载电流又不过大。

2017-11-09 12:17:53 155777

155777

漏极开路(OD)输出,跟集电极开路输出是十分类似的。将上面的三极管换成场效应管即可。这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。对于漏极开路(OD)来说,输出端相当于三极管的集电极。 要得到高电平状态需要上拉电阻才行。 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内)。

2017-11-09 14:17:01 19382

19382

集电极开路输出的结构,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。漏极开路是驱动电路的输出三极管的集电极开路,可以通过外接的上拉电阻提高驱动能力。

2017-11-09 14:28:38 18381

18381

线与”逻辑是因为多个逻辑门的输出三极管(场效应管、二极管),共用一个上拉电阻,只要一个逻辑门输出低电平,即集电极(漏极)开路输出的管子导通,就把上拉电阻接地,输出低电平;只有全部输出管截止,输出端被上拉电阻置为高电平,这就是与逻辑的运算结果。

2017-11-09 17:13:35 25795

25795

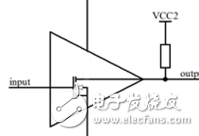

该装置包含六个独立的门,每个门执行缓冲功能。开路集电极输出需要外部上拉电阻才能正常逻辑操作。

2019-04-24 08:00:00 1

1 首先讲一下集电极开路输出(Open-Collector),单片机I/O常用的输出方式的开漏输出(Open-Drain),漏极开路电路概念中提到的“漏”是指 MOSFET的漏极。同理,集电极开路电路中的“集”就是指三极管的集电极。在数字电路中,分别简称OD门和OC门。

2019-08-26 17:30:00 12

12 集电极开路输出端或者MOS管漏极输出端其性质都是一样的,这种电路在数字电路中都要加上拉电阻。比如在单片机P0口其内部驱动电路是MOS构成的,其结构就是一个漏极开路电路,其内部没有上拉电阻。

2019-09-28 07:00:00 10202

10202 PmodOC1是使用MMBT3904晶体管的集电极开路BJT模块。

2019-11-29 14:38:33 2176

2176

一般芯片的数据手册将对输出管脚说明这一点,在如下功能电路图中,其中输出管脚就采用漏级开路输出模式。

2020-03-21 10:56:54 25536

25536 电子发烧友网为你提供什么是集电极开路(OC)?什么是漏极开路(OD)?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-13 08:42:31 9

9 DM5438/DM7438缓冲器集电极开路输出资料手册免费下载。

2021-06-01 17:51:18 11

11 推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2021-10-28 17:51:00 9

9 推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉

2021-11-15 20:21:06 34

34 单片机I/O开漏输出详解开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构

2021-11-15 20:36:07 7

7 推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2021-11-16 09:21:01 21

21 推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般

2021-12-05 10:36:05 13

13 1.1.1 接口相关电路及概念1. 集电极开路输出在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提到的“漏”是指

2022-01-14 14:32:40 23

23 因此集电极开路的输出视为NPN晶体管,它允许电流吸收到公共端。对于这样集电极开路电路,必须有一个电源才能使输出正常工作。当我们要求未连接任何电源时计算输出电压时,电压不会发生变化。必须计算输出端的电压以了解集电极开路电路的正常运行。

2023-01-08 15:03:01 6075

6075 今天给大家分享的是:集电极开路电路、集电极开路晶体管电路、集电极开路工作原理、集电极开路TTL、集电极开路输出接线图、集电极开路优缺点。

2023-01-13 09:48:30 3192

3192 集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

2023-01-16 09:16:28 1684

1684 具有漏极开路输出的低功率逆变器-74AUP1G06_Q100

2023-02-10 19:12:15 0

0 具有漏极开路输出的低功耗双逆变器-74AUP2G06

2023-02-10 19:18:57 0

0 具有漏极开路输出的低功率逆变器-74AUP1G06

2023-02-14 19:05:03 0

0 具有漏极开路输出的 2 输入与门-74AHC1G09_Q100

2023-02-14 19:11:18 1

1 具有漏极开路输出的 2 输入与门-74AHC1G09

2023-02-14 19:11:35 0

0 具有漏极开路输出的低功率逆变器-74AXP1G06

2023-02-15 20:15:26 0

0 具有漏极开路输出的低功耗三重缓冲器-74AUP3G07

2023-02-17 18:49:48 0

0 带漏极开路输出的六角反相器-74LVC06A

2023-02-17 19:46:23 0

0 带漏极开路输出的六角反相器-74LVC06A_Q100

2023-02-17 19:46:40 0

0 带漏极开路输出的六角反相器-74HC05_Q100

2023-02-17 19:54:47 0

0 带漏极开路输出的六角反相器-74HC05

2023-02-17 19:54:59 0

0 具有漏极开路输出的三路反相器-74HC_HCT3G06

2023-02-20 19:55:15 0

0 带漏极开路输出的六角反相器-74LV05A

2023-03-03 19:49:05 0

0 何为集电极开路电路?集电极开路就像是一个开关,其一端连接电源或接地。集电极开路电路常用在集成电路的输出,其输出可以根据使用的晶体管类型(NPN型或PNP型)为外围提供灌电流和拉电流能力。由于NPN

2023-07-31 23:07:05 3332

3332

ttl电路中推拉输出,集电极开路输出,三态输出有何不同? TTL电路是一种常见的数字逻辑电路,在电路中经常出现推拉输出、集电极开路输出、三态输出这些术语。这些输出方式在不同的电路中具有不同的意义

2023-08-31 10:32:19 6998

6998 电子发烧友网站提供《74AHCT07A具有漏极开路输出的六进制缓冲器.pdf》资料免费下载

2023-09-27 09:35:17 0

0 集电极开路电路是一种常见的逻辑电路,它的特点是输出端有一个开路的集电极。

2024-02-17 15:11:00 3245

3245

集电极开路是各种集成电路中常见的输出。集电极开路就像一个接地或断开的开关。除了将IC或任何其他晶体管的输出连接到特定设备外,还连接到NPN晶体管的集电极开路的基极端子,NPN晶体管的发射极端子与接地引脚内部连接。

2024-02-15 09:24:00 1977

1977

集电极开路门的内部结构设计会直接影响其开关速度。例如,电极间的距离、材料选择、通道长度等都会对开关速度产生影响。

2024-03-18 17:10:20 2517

2517

电子发烧友网站提供《具有开路集电极输出的四个2输入正NAND缓冲器数据表.pdf》资料免费下载

2024-05-11 10:10:07 0

0 电子发烧友网站提供《具有开路集电极输出的八进制缓冲器/驱动器数据表.pdf》资料免费下载

2024-05-13 10:14:21 0

0 电子发烧友网站提供《具有开路集电极输出的八路缓冲器和线路驱动器数据表 .pdf》资料免费下载

2024-05-13 10:33:45 0

0 电子发烧友网站提供《具有集电极开路输出的四路2输入正NOR缓冲器数据表.pdf》资料免费下载

2024-05-13 11:19:22 0

0 电子发烧友网站提供《四个2输入互斥NOR门,带开路集电极输出数据表.pdf》资料免费下载

2024-05-14 09:36:51 0

0 电子发烧友网站提供《具有集电极开路输出的四路2输入正与门数据表.pdf》资料免费下载

2024-05-14 10:20:33 0

0 电子发烧友网站提供《集电极开路输出的四路2输入正NAND门数据表.pdf》资料免费下载

2024-05-15 10:05:39 0

0 电子发烧友网站提供《具有集电极开路输出的四路2输入异或门数据表.pdf》资料免费下载

2024-05-16 10:51:00 0

0 电子发烧友网站提供《具有开路集电极输出的八路缓冲器和线路驱动器数据表.pdf》资料免费下载

2024-05-17 10:22:47 0

0 电子发烧友网站提供《具有集电极开路输出的四路2输入正NOR缓冲器数据表.pdf》资料免费下载

2024-05-17 10:19:15 0

0 电子发烧友网站提供《漏极开路输出的三重逆变器缓冲器/驱动器数据表.pdf》资料免费下载

2024-05-21 10:44:45 0

0 电子发烧友网站提供《具有开路集电极输出的八路总线收发器数据表.pdf》资料免费下载

2024-05-22 10:37:20 0

0 电子发烧友网站提供《具有开路集电极输出的十六进制反相缓冲器数据表.pdf》资料免费下载

2024-05-22 10:33:51 0

0 电子发烧友网站提供《具有开路集电极输出的八进制缓冲器/驱动器数据表.pdf》资料免费下载

2024-05-22 11:06:28 0

0 电子发烧友网站提供《使用漏极开路输出的 SN74HC266 四路2输入XNOR 门数据表.pdf》资料免费下载

2024-05-23 10:20:32 0

0 电子发烧友网站提供《具有集电极开路输出的四路2输入正NAND缓冲器数据表.pdf》资料免费下载

2024-05-23 10:19:37 0

0 电子发烧友网站提供《集电极开路输出的十六进制非逆变器数据表.pdf》资料免费下载

2024-05-23 10:18:22 0

0 电子发烧友网站提供《具有开路集电极输出的八进制缓冲器/驱动器数据表.pdf》资料免费下载

2024-05-29 09:53:08 0

0 在集成电路的广阔领域中,集电极开路作为一种独特的输出形式,扮演着举足轻重的角色。它如同一个精密控制的开关,既能实现电路的通断,又能灵活应对不同的电流需求。 集电极开路的基本概念与原理 集电极开路

2024-09-19 10:19:12 1992

1992

NPN双极晶体管在集电极开路配置下运行时,其行为模式介于完全导通与完全截止之间,仿佛一个精密的固态开关。在没有施加基极偏置电压的情况下,晶体管处于关断状态,此时集电极与发射极之间的电阻极高,几乎无

2024-09-19 10:23:53 2652

2652 集电极开路逻辑,顾名思义,是指集电极处于开路状态的一种电路配置。在这种状态下,输出端要么接地,形成电流通路;要么保持开路,即与地断开连接。这种独特的输出方式使得集电极开路逻辑在电路设计中具有广泛

2024-09-19 10:29:50 1722

1722 PNP集电极开路输出是指在这种输出配置下,当晶体管导通时,其集电极(即输出端)与电源轨相连,实现高电平输出;而当晶体管关断时,输出端则通过外部连接的“下拉”电阻被动地拉低至低电平。这种输出

2024-09-19 10:38:23 2917

2917 集电极开路逻辑作为一种独特的输出方式,其输出端可以吸收电流,但无法提供电流。这一特性使得多个集电极开路输出能够轻松地连接在同一条公共信号线上,而不会发生相互干扰。这种设计不仅节省了布线空间,还提

2024-09-19 10:47:09 1088

1088 集电极开路逻辑的优点主要体现在以下几个方面: 集电极开路逻辑具有出色的兼容性和连接性。由于其独特的漏极开路特性,集电极开路逻辑能够轻松地与其他数字设备相连,无需额外的接口或转换电路。这种直接

2024-09-19 10:51:56 1326

1326

电子发烧友App

电子发烧友App

评论