在运放的使用中,最初级的硬件设计者的想法就是只有增益倍数这一个参数。当然这是运放的基本能力,但是显然只知道放大倍数是不能说其会使用运放的。或许你知道运放,知道差分放大是放大差分信号的,甚至还知道共模抑制比。那么,今天来聊聊共模电平对于运放以及信号系统的意义。

2022-09-21 17:19:10 3082

3082 我们在选择运放的时候,第一步需要考虑的就是运放的供电。大部分情况下,我们需要放大的信号都是共模电压接近0的微弱直流或者交流信号,如果我们选择了需要正负供电的运放,而提供的负电源轨又是GND的时候,小信号往往无法得到正确的放大,造成电路设计错误。

2022-12-06 15:35:40 7445

7445

,特别容易忽视运放的一些重要指标参数,比如:输入偏置电流、输入失调电压、输入失调电流、最大共模输入电压、共模抑制比、输入噪声电压等等。其实这些参数对运放精度会有相当大的影响,如果不搞懂这些参数含义会让你在

2023-04-25 09:23:43 8834

8834

定义了运放能正常工作的一个共模输入电压区间,并描述了输入电压与两个电压轨靠近的程度。对VICMR的另一种认识方式是,它描述了由最小值VICMR、VICMRMIN和最大值VICMR、VICMRMAX所

2011-10-24 21:06:52

。但是,哪种电容有影响?差模电容?共模电容?还是都有?运放输入电容一般可以在输入阻抗参数一栏找到,差模电容和共模电容都有标明。输入电容模型如图1:共模电容连接各个输入端到地,而差模电容连接在两个输入端

2018-09-21 15:29:00

请赐教。这里的运放能否正常工作,我是想采集锂电池某一节的电压。

2013-08-24 20:50:15

运放共模输入阻抗和差模输入阻抗,这两者有什么区别?

2021-03-29 07:55:35

理想情况下应为 0 V。因此,对应于 0 V差分输入,该运算放大器的输出端电压必须等于VCM。

请教下,运放以单位增益放大共模信号,而以G增益放大差模信号怎么理解

2024-09-20 10:02:29

运放输入的“共模输入阻抗”是输入对地(或对电源)的阻抗,“差模阻抗”则是两输入端间的阻抗。通常(VFA)运放的共模输入阻抗比差模要大很多,但由于深度负反馈的作用,差模阻抗影响减小很多。对于一楼图中

2019-06-03 07:25:00

运放输入的共模信号和差摸信号,具体是怎么定义的?

2017-05-05 22:41:02

你好,我想咨询下运放OP282的共模输入电容和差模输入电容是多少?在45度的相位裕度时带宽是多少?谢谢

2023-11-23 07:23:24

拓扑采用反相放大结构(反相端接信号,同相端直接接地)。

有直流偏置电压加在运放的反相端,直流偏置电压范围+/-10V。

麻烦问一下该运放反相端的最大输入电压是多少?+/-10V的偏置电压是否会造成运放

2024-08-13 07:27:41

是:反比例运放,反向端输入Vi,则反向端的电压为:Vi/2(共模)+Vi/2(差模)=Vi,正向端为:Vi/2(共模)+(-Vi/2)(差模)=0。所以说,"此放运放的共模信号将为0"

2018-01-31 21:34:00

请教各位,

1. 运放的输入阻抗是指差分输入阻抗还是共模输入阻抗?

2. 二者有什么差别呢?

3. 从电路的角度,二者与运放输入端的连接方式是如何呢?

2024-08-16 06:25:07

的共模输入电压幅度范围内说的,超出了该范围运放的高共模抑制比的特性就不复存在了,以致于器件不能正常工作。降低端子的输入阻抗可以有效的减小电场干扰。4.开环输出阻抗及闭环输出阻抗 输出电压与输出电流

2018-07-13 01:31:17

电阻和输入电容,在低频时仅指输入电阻。 (2)共模输入阻抗 共模输入阻抗定义为,运放工作在输入信号时(即运放两输入端输入同一个信号),共模输入电压的变化量与对应的 输入电流变化量之比。在低频情况下,它表现

2018-09-29 15:26:19

运放的差模输入与共模输入的区别

2024-09-18 07:37:44

的应用,选取失调电压小的运放。输入偏置电流一般无法准确补偿。越大的CMRR,对抑制开关噪声(共模干扰),越有效果。PSRR越大,辅电对运放输出影响越小

2022-10-18 09:35:27

工作条件的原理是什么?

还有一种运放,能够实现较高的共模输入电压,也就是其共模输入电压能够达到额定供电电压的数倍甚至数十倍,但是运放的参数要求,运放的共模输入电压不会超出供电电压,请问这是什么原因?其原理是什么,为什么会用到这种运放结构,这种运放相较于普通运放的优缺点是什么?

2024-05-06 21:37:13

仔细捕捉, 发现出现这个问题的原因是运放正相输入端输入电压低于 -0.7V 导致的.

运放数据手册虽然都提到输入共模范围的要求, 但却从来没有看到当输入信号超出这个范围时会发生什么情况. 这个波形

2024-09-14 06:18:01

欧,此时当输入端差模电压为3.4mV时,输出电压为3.4V,放大倍数变为1000倍,与数据手册描述也不符合。

请问该电路是否存在问题?为何放大倍数存在如此大的偏差?

在单电源供电时,我考虑过是否是因为输入共模电压过低导致?请问在单电源供电情况下,输入共模电压是否在1/2VCC最合适?

2023-11-24 07:01:27

我看到ADS1278上写输入参看电压2.5V,输入共模电压2.5V。一般输入共模电压不是一个范围吗,为什么是一个确定的数了?我现在混乱了。

2024-03-08 10:56:54

较大的共模干扰(线缆无屏蔽层)。

ADS8688前端电路不知是否应该用仪表运放提高抗共模干扰能力,还是可以直接利用ADS8688的高输入阻抗和差分输入能力来实现ADC精度要求。

2024-12-24 07:08:09

想问下INA240A1D输入端(IN+、IN-)共模电压问题。

从官方给的芯片数据手册看,当VS=5V时,运放的两输入端可以承受-4~+80V的共模电压。目前我想把运放使用在VS=3.3V时,请问IN+、IN-的共模电压范围是多少?

2024-08-06 06:42:19

LT1395运放的共模输入电压范围是多少?输入共模电压和电源电压之间的关系是怎样的。数据手册只给出了5V和±5V条件下的输入共模电压范围。假如采用Vs=+7V单端供电,输入共模电压范围是多少?

同样运放输出电压和电源电压的关系呢?

想用这款芯片做电压跟随,有没有推荐的资料呢?谢谢!

2023-12-05 06:29:47

OPA1632的输入信号可以和运放不共地吗,会不会容易受到干扰

2024-08-08 07:27:15

幅频特性曲线与使用R=1MΩ,C=2pF的一阶低通滤波几乎一致,是否可由此判断图中跟随器的接入等效于在R3一端接入了运放的共模输入阻抗?但是将运放换为OPA827,其GBP22MHz,压摆率28V/μs

2024-07-29 08:30:38

了运放输入共模电阻上了?OPA277共模电阻是250GΩ。电压的正负是不是由偏置电流的方向决定的?

而在图3中,R8,R9就作为了输入共模电阻,所以共模电压就非常小了。

2024-09-18 08:49:49

如上电路图示应用中,运放前级的差分输入电阻值范围怎么限制,它的选值与运放的差模输入阻抗和共

模输入阻抗有什么关系。是不是可以无限的取大?

2024-08-28 07:37:23

规格书并没有明确这个问题,但是应用示例中给出了如下图的差分输入形式。

当输入电压Vsource与运放的供电Vcc不共地(即两个电压相互隔离)时,运放能否正常工作?

2024-07-30 06:23:20

TINA能否仿真运放的最大共模电压范围?

在仿真中,+-5V供电的LM358,在共模电压加到7v还能正常放大,与实际不符。

是否所有运放的模型都不能体现最大共模的范围?

2024-09-12 06:58:06

不出来。还是先看图吧。好简单哦,可惜你就是调不出来。还是先看图吧。什么电源轨、共模输入范围、增益积带宽、带载能力、压摆率。。。我全都考虑了啊,还是不对呢?因为,CFA和VFA(电压反馈运放)不一样

2017-07-26 16:19:00

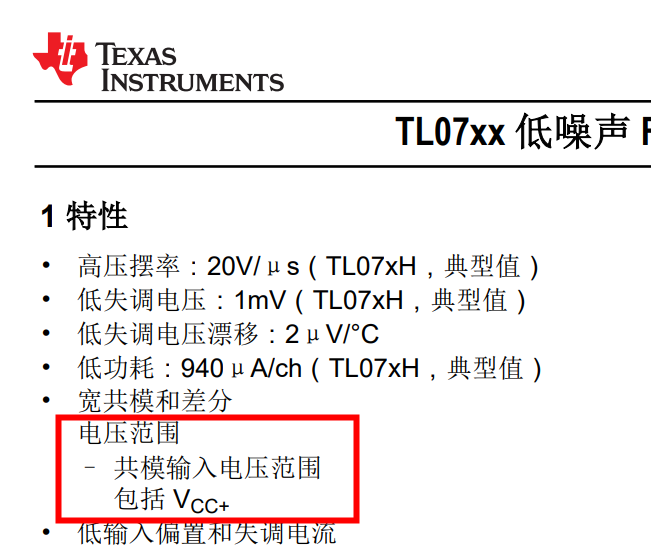

一颗运放,并且没有找到问题原因,幸运的是,在没有完全弄清原理的前提下,我们碰巧选到了一颗可以正常工作的运放。来看下这款运放的一个指标,运放共模输入范围:运放共模输入范围是运放输入电压的一个区间,它表征

2017-08-15 14:52:02

放大器的对称程度及增益。这很明显,没有任何运放提供其共模抑制比的同时,附加了外部电路的结构条件。对于单端输入,无论是同相还是反相,其等效共模值均是输入值的一半。但因同相放大的输入阻抗通常大于反相放大,其

2018-01-18 14:24:52

功率带宽、建立时间、等效输入噪声电压、差模输入阻抗、共模输入阻抗、输出阻抗。(1)输入失调电压Uos:输入失调电压定义为集成运放输出端电压为零时,两个输入端之间所加的补偿电压。输入失调电压实际上反映了运

2014-05-26 13:30:40

的输入端电流变化量的比值。差模输入阻抗包括输入电阻和输入电容,在低频时仅指输入电阻。

(2)共模输入阻抗

共模输入阻抗定义为,运放工作在输入信号时(即运放两输入端输入同一个信号),共模输入电压的变化量

2023-11-22 07:09:18

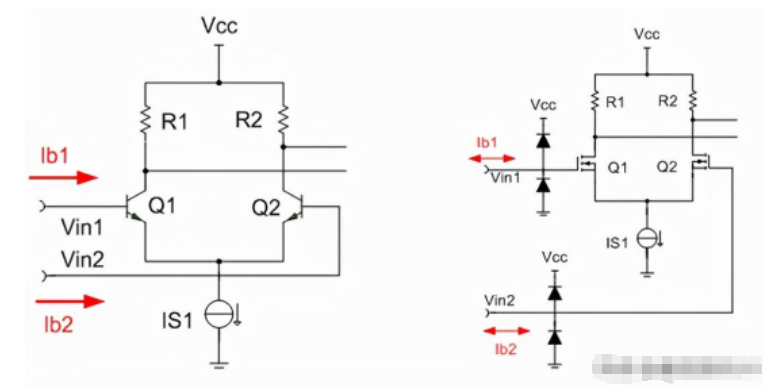

仪表放大器(IA)是配备反馈组件的全闭环放大器,其可以在抑制共模信号的同时放大差分输入信号。虽然内部设计可能不尽相同,但常用的三运放拓扑(图1)很有代表性。很多类型产品配备单一外部电阻器RG,增益

2017-04-01 14:40:53

hi,我在研究ADL5566参数的时候,从手册中了解到ADL5566的输入共模电压1.2V-1.8V/3.3VCC,但是我在看到ADL5566的demo板的时候,模拟输入前端使用AC耦合,进入运放

2018-08-02 10:20:02

AD7760 datasheet里似乎没有明确的说明内置运放输入(VinA+/VinA-)的允许共模电压范围,图52的例子里给的是共模电压0V,输入±2.5V的信号。

如果我希望在VinA+

2023-12-04 06:32:39

典型的差分放大电路(减法电路)输入信号与运放不共地,是否有问题?

2024-08-13 06:38:36

到底什么是运放的输入共模区间?超出这一区间的影响是什么?如何解决运放的VICMR问题?

2021-04-19 08:21:51

共模电压范围能不能理解为运放构成跟随器时的最大输入电压,而差模输入电压是运放开环时两输入端的差值范围。

还有就是有没有具体的电路来测试这两项参数?

2024-08-07 06:30:43

假设R1~R4都是理想5K的电阻,运放的CMRR为130dB,那么由此运放CMRR带来的共模输出电压怎么算呢?原理图如下:

2024-08-15 07:51:51

差分输入需要与运放共地吗,不共地的话,差分信号是怎么通过运放形成回路的,如本图所示,求大神指教

2023-11-15 08:14:49

OP2177数据手册中的18页图63组成的差动放大电路,如果输入电压和运放的供电电源不共地的话,该电路是否还有效?

2019-01-25 14:04:04

怎么根据共模抑制比Kcmr、最大共模输入电压Vic挑选运放

常见的集成运放推荐?

2024-08-19 06:22:13

端的输入电压相等且相位相同。对于高输入阻抗的运放来说,如果共模输入电压幅度超出一定的范围,其是不能够正常工作的。之所以强调该点,是因为对于初学者来说往往忽略了这点。运放在实际的工作环境中总是存在比较

2012-01-11 16:41:01

忽略了这点。运放在实际的工作环境中总是存在比较强的电磁场干扰的,对于高输入阻抗的输入端子来说,是非常容易感应外界的干扰电压的,而这种干扰电压一般都是以共模信号的形式存在的。虽然说运放一般具有很高

2012-12-16 22:03:14

小(PCB导线电阻);R1非常大->+∞(实际也就绝缘电阻那么大)

对于运放有两个参数,怎么理解?:

输入电阻

差模 RINDM 30 k

共模 RINCM 100 G

2024-09-03 06:12:30

吗?但是这个运放的输入电压范围又可以到达-0.3~5V(5V单供电情况下)。所以我猜想,运放是“识别”的了这个输入信号的。那么问题来了,怎么区分共模数日电压范围和输入电压范围呢?也即什么时候看共模电压输入

2017-12-28 21:57:58

目的:测量运放的共模输入阻抗,被测运放的datasheet中标注的共模阻抗为220G欧姆,请问用何种方法测量。

需要注意什么??谢谢!

2024-08-26 07:03:14

输入范围:器件(运放、仪放……)保持正常放大功能(保持一定共模抑制比CMRR)条件下允许的共模信号的范围。显然,不存在“某一端”上的共模电压的问题。但“某一端”也一样存在输入电压范围问题。而且这个范围

2018-03-12 13:24:07

角度,就像几何学里的坐标变换,同一个点在不同坐标系中的坐标值不同,但始终是同一个点。运放的共模输入范围:器件(运放、仪放……)保持正常放大功能(保持一定共模抑制比 CMRR)条件下允许的共模信号的范围

2018-01-09 09:00:50

请问共模输入电压范围是指的什么?

在一个放大器设计初期选型的时候关于这个参数我该怎么选择?

在选定一个运放后,我的电路是应该调整到这个共模输入电压范围内?又该怎么调整?

2024-09-25 08:31:55

请问运放OP284F的输入共模电压可不可以为0?我将两个输入端短路接到地上,然后通过外部电阻调节增益,观察输出来评估其噪声性能,请问这种方法合适吗?

2018-11-22 08:56:55

请问运放OP284F的输入共模电压可不可以为0?我将两个输入端短路接到地上,然后通过外部电阻调节增益,观察输出来评估其噪声性能,请问这种方法合适吗?

2023-11-28 07:10:51

运放的单端输入电压范围与共模输入电压范围是一回事,怎么理解,没看懂?对于其他放大器,怎么共模输入电压范围就要小于单端输入电压范围了

2019-06-11 04:36:19

各位老师好!请问,脑电采集时电极-皮肤接触阻抗比较高,那么前置运放选型的时候,要求具有高输入阻抗的特点,请问这个高输入阻抗指的是差模输入阻抗,还是共模输入阻抗?还是都要高?还是其他情况?

2019-01-16 17:25:20

826输入共模电压只有vs电压(最大+-18v),希望能可以推荐一款48V共模电压的、性能接近仪器仪表的运放。INA149倒是高共模,但内部分压比1:20有点高。差分输入vin1-vin2电压最大

2024-08-27 06:17:18

这个问题一直混淆着我:差分运放就是差动运放吗?仪表运放也可以差分输入,它们之间的关系到底如何?

我想在一个数据采集的前端处理部分用 AD620,输入为0-10v单端信号,AD620的(IN-)接地

2023-11-28 08:22:50

电阻和输入电容,在低频时仅指输入电阻。 (2)共模输入阻抗 共模输入阻抗定义为,运放工作在输入信号时(即运放两输入端输入同一个信号),共模输入电压的变化量与对应的 输入电流变化量之比。在低频情况下,它

2019-12-26 14:44:23

集成运放的主要参数是什么?答:(1)最大差模输入电压Vidmax 指运放两输入端所允许加的最大差模电压值,超过该值,运放输入极差分对管将被反

2009-04-22 20:32:37 7132

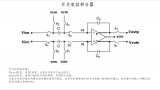

7132 使用三运放搭建输入缓冲级和输出级电路

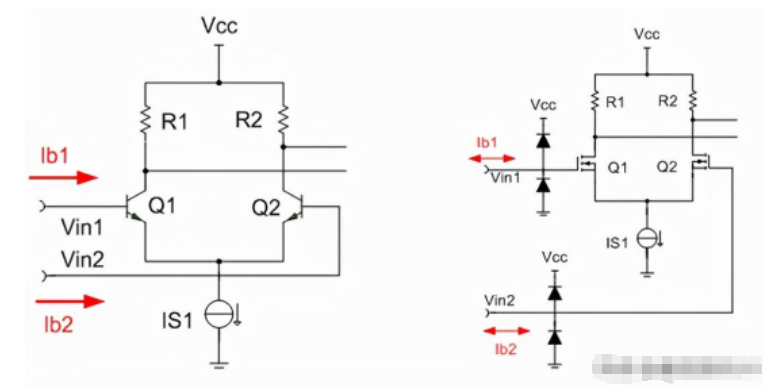

传统IA使用三运放搭建输入缓冲级和输出级电路(图2)。输入缓冲级电路提供全差分增益、单位共模增益和高阻输入,差分

2009-12-07 22:47:26 2300

2300

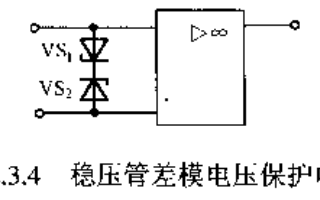

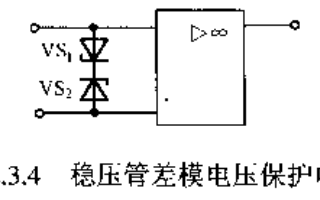

电子发烧友为您提供了运放差模电压击穿输入级保护电路图全集,希望能够帮助您解决难题!

2011-06-22 08:55:43 5164

5164

模电运放基本模块及其介绍共讲述了 电压跟随器 ,同相放大器,反向放大器等七种模电运放基本模块电路及其原理分析。

2011-08-10 15:38:54 275

275 运放仪表放大器,其VCM为共模电压,而VDIFF为相同仪表放大器的差动输入。

2011-11-24 11:26:20 9181

9181

AD620是一款单芯片仪表放大器,采用经典的三运放改进设计。有两个输入端,即正输入端和负输入端,信号通过两路输入,实现差分放大,这样可以去掉输入信号中对地的共模干扰。由此可见,AD620可以抵抗输入信号中的共模干扰。

2017-11-15 17:40:56 8812

8812

共模输入是共模输入电压。所谓同相比例运放也就是输入信号在同相端,而同相比例运放满足负反馈,即满足虚短和虚断,根据虚短,U+ = U- ,而U+ = Uin,所以共模信号= (U+ + U-)/2 = Uin.

2017-11-18 10:37:45 50670

50670

电路的精度。此外,两个辅助运放也是全差分的,也需要共模反馈。由于辅助运放不需要大的输出摆幅,而且辅助运放nbooster和pbooster是接成跟随器的形式,所以稳定了输入共模也就稳定了输出共模。

2018-06-08 08:59:00 11077

11077

今天讲解集成运放输入电压保护的常用方法、设计思路,以供大家学习借鉴。 01 差模输入电压保护电路 输入端差模电压超过集成运放差模输入电压的允许范围,将导致集成运放损坏,必要时需加保护电路。 (1

2020-10-31 10:22:47 17737

17737

电子发烧友网为你提供运放共模输入阻抗和差模输入阻抗,这两者有什么区别?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-02 08:52:17 9

9 AD8479-EP:超高共模电压精密差放

2021-05-15 20:02:49 8

8 运放的共模抑制比,我们先了解一下运放的共模输入电压,运放的共模输入电压是指运放的两个输入引脚电压的平均值,注意是“平均值”,这一点很重要,如下图所示。对于双极性输入级的运放,运放的共模输入电压,一般达不到电源轨

2023-04-27 14:56:54 4

4 共模差模输入计算公式详解 共模差模输入是电路中常见的一个概念,常用于放大运算器及其他电路中。本文将详细介绍共模差模输入的概念、计算公式及其应用。 一、共模和差模信号 在电路中,信号可以分为共模和差

2023-09-19 17:23:09 11099

11099 为什么共源共栅运放被称为telescope? 共源共栅运放,也被称为telescope,是一种特殊的MOSFET运放。它由一对共源共栅电路构成,可以被看作是两个基本的单级MOSFET放大器级联

2023-09-20 16:29:41 1996

1996 在给一个精密传感器模拟前端设计信号调理模块,是否应该使用轨到轨输入的运放? 在设计信号调理模块时,选择运放是一个非常关键的决定。在这篇文章中,我们将分析什么是轨到轨运放、何时需要使用轨到轨运放以及轨

2023-10-29 14:21:35 1013

1013 你是否考虑过运放的输入偏置电流对电路的影响呢? 输入偏置电流是指运放在没有输入信号的情况下,输出端所产生的微小电流。这个微小电流会在运放的反馈回路中流动,从而导致电路的偏差。因此,在设计运放电

2023-10-30 09:22:02 1912

1912 等。在这些因素中,共模抑制比率(CMRR)是我们需要关注和了解的一个重要指标。 CMRR是运放的一个重要参数,它是指在输入信号一致时,输出信号与两个输入信号之间的差异,也就是共模电压,之间的比率。这个比率越大,说明运放的共

2023-11-06 10:20:00 1113

1113 运放的共模抑制比高有什么作用?共模抑制比比较高的运放有哪些啊? 共模抑制比(Common Mode Rejection Ratio,CMRR)是一个衡量运放的性能的重要指标,表示运放在输入信号的共模

2023-11-20 16:35:53 3089

3089 全差分运放中输出共模点由共模反馈进行稳定,而并未有电路或手段为运放输入提供DC共模点,该自建立的输入共模点如何进行建立和确定的?

2023-12-01 14:32:37 3708

3708

电子发烧友App

电子发烧友App

评论