作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 3153

3153 当我们安装好Vivado 的时候,也同时装好了Vivado HLS.。 这是个什么东西?我就有一种想一探究的感觉。网上一查,Vivado High-Level Synthesis。学习了一段时间

2020-10-14 15:17:19 2880

2880

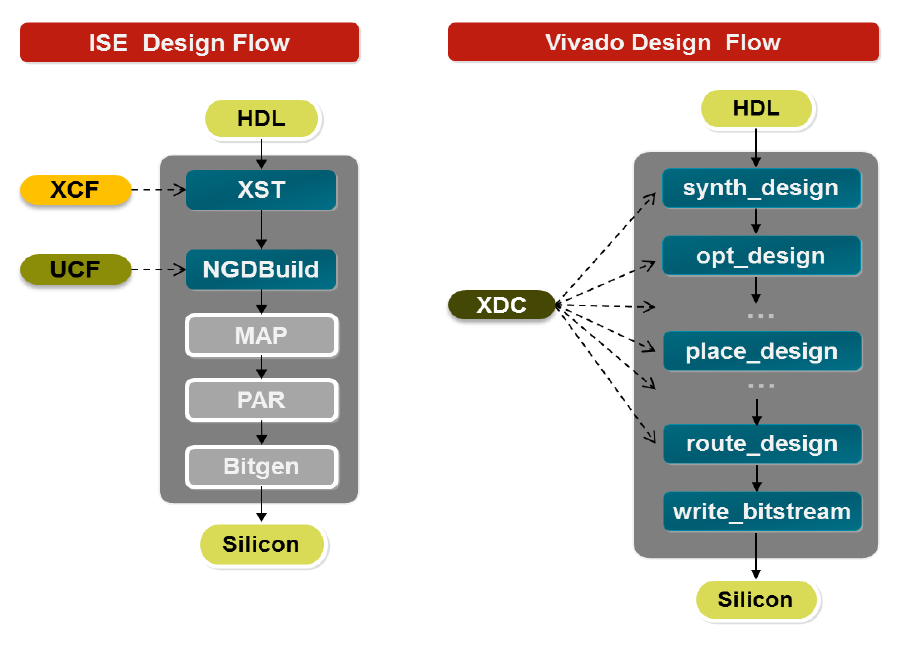

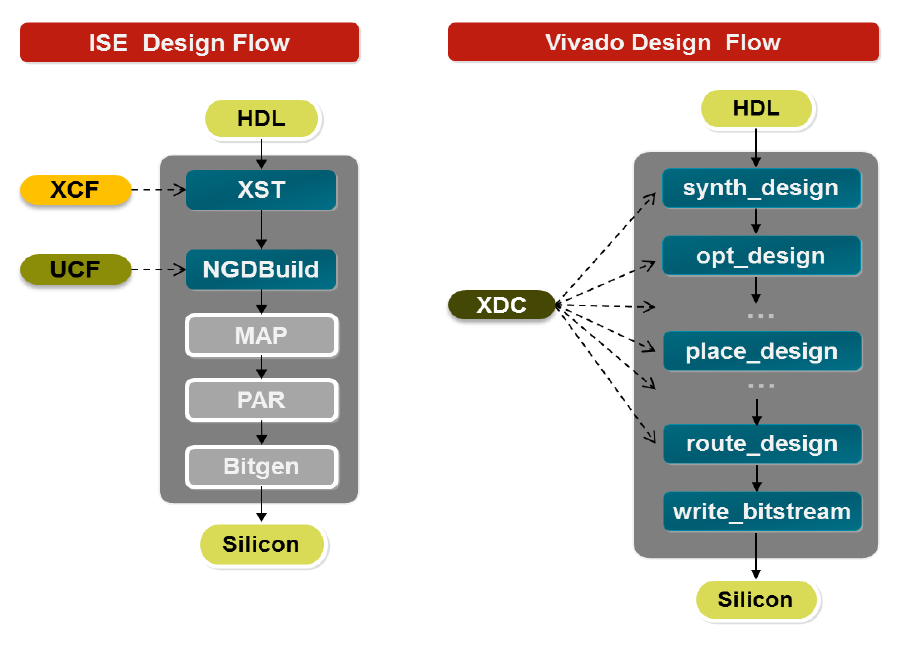

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。

2022-09-14 09:09:56 1526

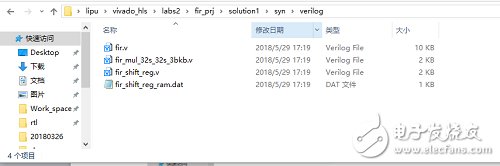

1526 的RTL代码。在ISE或者Vivado开发环境中做RTL的集成和SOC/FPGA实现。2.2.1 VivadoHLS视频库函数HLS视频库是包含在hls命名空间内的C++代码。#include

2021-07-08 08:30:00

SoC器件上快速地加速和集成您的计算机视觉应用。本次研讨会将通过对一个具体案例的流程进行“逐层拆解(Step-by-Step)一个设计案列”的方式,向您介绍如何利用Vivado HLS(高层次综合

2013-12-30 16:09:34

我在Vivado HLS中有以下错误的合成。我试图更新许可证文件但没有成功。请给我一个建议。@E [HLS-72]许可证签出不成功。确保可以访问许可证或通过环境变量指定适当的许可证。 执行

2020-05-20 09:13:21

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-11 07:09:49

嗨,在我的Vivado实现tcl脚本中,以下行导致错误:设置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

`Vivado 开发环境简介及设计流程`

2017-12-12 10:15:48

:Xilinx提供的第三方TCL脚本库的窗口;3.1.3 信息中心Documantationand Turorials:文档中心连接口,关联到DocNav,并筛选出Vivado的使用手册;Quick

2019-07-18 15:40:33

嗨,我需要为Vivado 2016.3运行tcl来运行多个测试平台。如果我使用下一个:launch_simulationrun -allwait_on_run [current_run

2020-05-20 15:53:34

本帖最后由 FindSpace博客 于 2017-4-19 16:57 编辑

在c simulation时,如果使用gcc编译器报错:/home/find/d/fpga/Vivado_HLS

2017-04-19 16:56:06

vivado可以正常使用,但是HLS总是出现图片中的错误。请问该如何解决?谢谢!

2020-08-12 01:36:19

你好!如果我想使用vivado hls来合成具有axi流接口的代码,是否有必须遵循的标准编码风格?

2020-04-21 10:23:47

你好,我做了Project->生成TCL脚本。现在,我希望能够从tcl脚本中指定.bit文件名。我怎么做?以上来自于谷歌翻译以下为原文hello,I did the Project->

2018-11-09 11:49:07

宏定义LEDS_CTL 的使用Makefile脚本语法简介Makefile测试

2020-12-22 06:39:05

PS和PL互联技术ZYNQ芯片开发流程的简介

2021-01-26 07:12:50

` 今天继续与大家分享一下使用TcL脚本生成Vivado工程及编译的开发体验。创龙提供了丰富的入门教程与Demo程序,帮助我们快速熟悉FPGA开发流程。先来了解一下什么是Tcl呢?Tcl是“Tool

2020-06-07 13:59:52

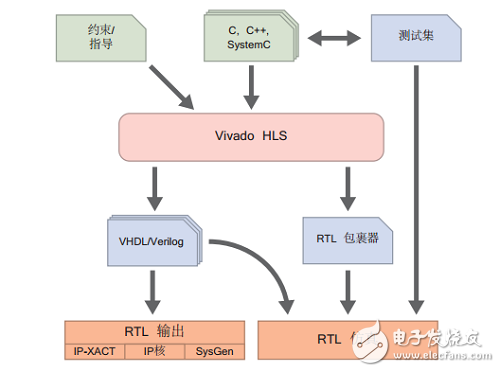

,大大减少了使用传统RTL描述进行FPGA开发所需的时间。本章包括以下几个部分:1.1高层综合简介1.2HLS设计流程1.3接口综合1.4算法综合1.5HLS库1.1高层综合简介在介绍HLS之前,我们

2020-10-10 16:44:42

【资料分享】Vivado HLS学习资料

2013-11-02 11:21:14

请问大家,这个tcl脚本文件是做什么用的呢????本人是菜鸟,还望大家多多指教啊

2013-06-14 16:05:26

求助大神 制作能够 “加载TCL脚本功能”得用什么控件!求指教求指点~!万分感谢~!{:36:}百度了好几天都没有~!

2013-04-22 09:55:43

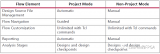

。Vivado支持工程模式(ProjectBased Mode)和非工程模式(NoneProject Mode)两种,且都能通过Tcl脚本批处理运行。工程模式主要是在Vivado图形化界面IDE中运行和调试

2022-06-17 14:52:14

你好,我使用Vivado HLS生成了一个IP。从HLS测量的执行和测量的执行时间实际上显着不同。由HLS计算的执行非常小(0.14 ms),但是当我使用AXI计时器在真实场景中测量它时,显示3.20 ms。为什么会有这么多差异? HLS没有告诉实际执行时间?等待回复。问候

2020-05-05 08:01:29

嗨,专家我以前在Windows下设计,最近我搬到了linux。是否有关于如何使用脚本运行ISE / VIVADO的指南,例如Perl的?谢谢。克里斯以上来自于谷歌翻译以下为原文Hi, experts

2019-02-19 10:59:18

你好,我编写了一个Tcl脚本来合成Vivado Design Suite 2014.4中的设计(适用于Zynq ZC 706)。设计中的库未编译。弹出错误,表示找不到特定的.vhd文件。我检查了

2020-04-16 10:15:31

将Vivado HLS与Virtex 6(ML605评估套件)一起使用时,我遇到以下问题。我想导出一个RTL Designas Pcore,以便稍后将其导入XPS作为完整设计的一部分。根据相对

2018-12-28 10:33:38

前 言本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

你好我正在尝试在vivado HLS中创建一个IP,然后在vivado中使用它每次我运行Export RTL我收到了这个警告警告:[Common 17-204]您的XILINX环境变量未定义。您将

2020-04-03 08:48:23

所有: 我正在尝试编写一个TCL脚本来重命名带有修订号的.bit文件。我需要一种方法让Vivado告诉我活动实现的名称。例如,如果我的活动实现是impl_5,我需要知道这一点,以便找到正确的.bit

2018-11-12 14:23:34

尊敬的先生,由于突然断电我的桌面电脑在vivado HLS正在进行我的代码的C-Synthesis时关闭了,电源恢复后我启动计算机并尝试启动HLS,然后小方形HLS符号来了(我把屏幕截图放在了注册

2020-04-09 06:00:49

嗨,我想试试JESD204硬件演示。为此,我必须在Windows命令提示符下使用“vivado -mode batch -source”运行.tcl脚本,但是当我输入此内容时,我收到一条错误,即vivado命令未知或错误。我现在能做什么?非常感谢您提前和最好的问候扬 - 菲利普

2020-07-30 07:00:03

您好我有一个关于vivado hls的问题。RTL是否来自xivix FPGA的vivado hls onyl?我们可以在Design Compiler上使用它进行综合吗?谢谢

2020-04-13 09:12:32

您好Xilinx的用户和员工,我们正在考虑购买Zynq 7000用于机器视觉任务。我们没有编程FPGA的经验,并希望使用Vivado HLS来指导和加速我们的工作。关于这种方法的一些问题:您对

2020-03-25 09:04:39

Vivado 策略选择的文章中详细描述。

我们要展示的是如何对设计流程进行改动来更好的满足设计需求,这些动作往往只能通过 Tcl 脚本来实现。

充分利用物理优化

物理优化即 phys_opt_design

2023-06-28 19:34:58

。Vivado HLS作为该套件的一个组件,能帮助设计人员将采用C/C++语言开发的算法编译为RTL,以便在FPGA逻辑中运行。Vivado HLS工具非常适用于嵌入式视觉设计。在此流程中,您用C/C++

2014-04-21 15:49:33

你好,我有一个与switch语句的合成有关的问题。我开始使用Vivado HLS并且我已经创建了一个小的file.cpp,仅用于学习,但是当Vivado HLS合成文件时,我没有得到任何开关语句

2019-11-05 08:21:53

请问Vivado HLS出现这种情况是什么原因呢

2021-06-23 06:13:13

Vivado HLS设计流程是怎样的?

2021-06-17 10:33:59

嗨伙计,在我的PC Vivado设计套件2015.2和SDK 2015.2工作,但只有vivado HLS 2015.2没有打开,这就是为什么我想重新安装Vivado HLS 2015.2。如何下载

2018-12-27 10:57:49

Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 testbench来验证设计。 Integrate带有Xilinx IP Block的 HLS IP 这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

2017-02-07 17:59:29 4179

4179

,Xilinx Vivado HLS是一个高级综合工具,能够将C语言转换成硬件描述语言(HDL),也就是说我们可以用C语言来实现HDL模块编程了。 图1 Vivado HLS工作流程 第一位Hacker

2017-02-08 20:01:59 550

550

大,我是否能够利用Vivado HLS完成这项要求较高的运算呢? 我开始从软件方面考虑这个转换,我开始关注软件界面。毕竟,HLS创建专用于处理硬件接口的硬件。幸好Vivado HLS支持创建AXI slave的想法,同时工作量较少。 我发现Vivado HLS编码限制相当合理。它支持大多数C + +语言

2017-02-09 02:15:11 310

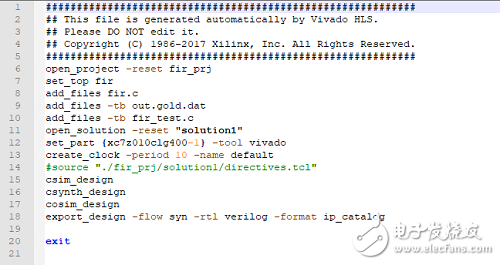

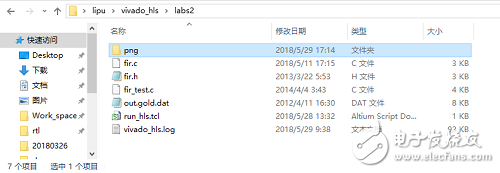

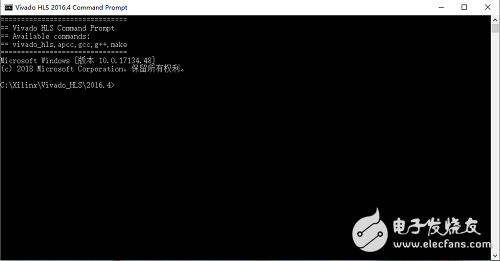

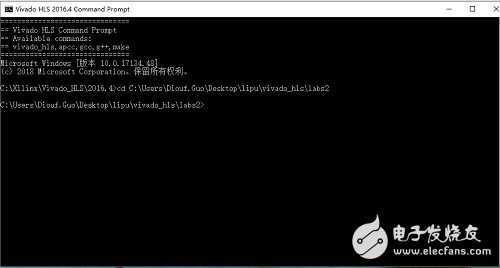

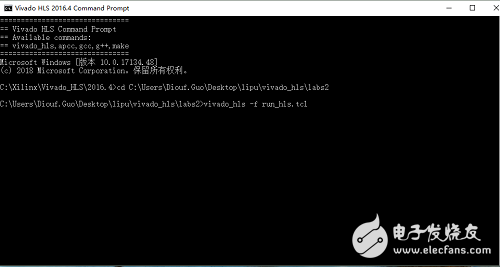

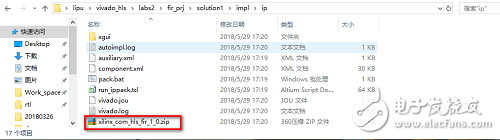

310 路径:cdc:\Vivado_HLS_Tutorial\Introduction\lab3. 3.在命令提示符窗口中,键入:vivado_hls -f run_hls.tcl建立工程 4.在命令提示符

2017-02-09 05:07:11 411

411

/HLV 的优势,并希望探索在公司内部署该流程。要让 HLS/HLV 能成功予以采用, HLS 编码风格、代码检查、约束驱动型综合、设计构造以及 C++ 和 SystemC 代码的结构和功能验证都需要

2017-09-11 11:37:38 9

9 在使用高层次综合,创造高质量的RTL设计时,一个重要部分就是对C代码进行优化。Vivado Hls总是试图最小化loop和function的latency,为了实现这一点,它在loop

2017-11-16 14:44:58 3362

3362 随着无线网络的数据流量和密集度不断增加,所有运营商都面临着非常大的挑战。一套好的数据压缩算法能够帮助运营商节省不少的网络基础设备的开支。使用Xilinx Vivado HLS工具评估开放式无线电设备

2017-11-17 02:25:41 1267

1267

使用Xilinx Vivado HLS(Vivado 高层次综合)工具实现浮点复数QRD矩阵分解并提升开发效率。使用VivadoHLS可以快速、高效地基于FPGA实现各种矩阵分解算法,降低开发者

2017-11-17 17:47:43 3293

3293

其实Tcl在Vivado中还有很多延展应用,接下来我们就来讨论如何利用Tcl语言的灵活性和可扩展性,在Vivado中实现定制化的FPGA设计流程。 基本的FPGA设计实现流程 FPGA的设计流程简单来讲,就是从源代码到比特流文件的实现过程。大体上跟IC设计流程类似,可以分为前端设计和后端设计。

2017-11-18 01:48:01 3295

3295

在ISE下,对综合后的网表进行编辑几乎是不可能的事情,但在Vivado下成为可能。Vivado对Tcl的支持,使得Tcl脚本在FPGA设计中有了用武之地。本文通过一个实例演示如何在Vivado下利用Tcl脚本对综合后的网表进行编辑。

2017-11-18 03:16:01 6899

6899

Xilinx的新一代设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握

2017-11-18 03:52:01 4675

4675

1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

2017-12-04 10:07:17 0

0 在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

2018-01-10 14:33:02 19813

19813

TCL脚本语言 Tcl(Tool Command Language)是一种很通用的脚本语言,它几乎在所有的平台上都可以解释运行,而且VIVADO也提供了TCL命令行。最近发现TCL脚本貌似比GUI下操作VIVADO效率高一些,方便一些。

2018-04-11 12:09:00 9154

9154 本文内容介绍了基于用Vivado-HLS为软件提速,供参考

2018-03-26 16:09:10 7

7 工具命令语言(TCL)是集成在VIVADO环境中的脚本语言。TCL是半导体工业中用于应用程序编程接口的标准语言,并由SyoSype®设计约束(SDC)使用。

2018-08-09 08:00:00 38

38 OPENCV(Open Source Computer Vision)被广泛的使用在计算机视觉开发上。使用Vivado HLS视频库在zynq-7000全可编程soc上加速OPENCV 应用的开发,将大大提升我们的计算机视觉开发。

2018-11-10 10:47:49 1323

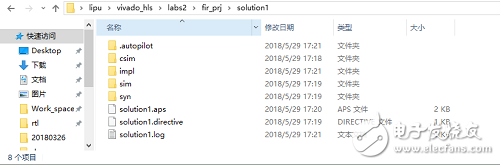

1323 了解如何使用GUI界面创建Vivado HLS项目,编译和执行C,C ++或SystemC算法,将C设计合成到RTL实现,查看报告并了解输出文件。

2018-11-20 06:09:00 3651

3651 了解如何使用Tcl命令语言以批处理模式运行Vivado HLS并提高工作效率。

该视频演示了如何从现有的Vivado HLS设计轻松创建新的Tcl批处理脚本。

2018-11-20 06:06:00 2887

2887 尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C 描述的算法却是不可以的。

2019-07-29 11:07:16 5072

5072

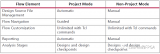

工程模式的关键优势在于可以通过在Vivado 中创建工程的方式管理整个设计流程,包括工程文件的位置、阶段性关键报告的生成、重要数据的输出和存储等。

2019-07-24 17:30:38 4204

4204

,还是从对使用者思路的要求,都是全新的;在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言XDC以及脚本语言Tcl的引入则成为了快速掌握Vivado使用技巧的最大障碍,以至于两年多后的今天,仍有很多用户缺乏升级到Vivado的信心。 本文介绍了Tcl在V

2020-11-17 17:32:26 2112

2112 Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助VivadoIDE或Tcl命令来运行。相比之下,VivadoIDE给project模式提供了更多的好处,而Tcl命令使得non-project模式运行起来更简单。

2020-10-21 10:58:07 3294

3294

的是VivadoIP,用于支持Vivado IP 设计流程。后者用于Vitis应用加速流程,此时,Vitis HLS会自动推断接口,无需在代码里通过Pragma或Directive的方式定义Interface,最终会输出.xo文件。 User Control Settings还有其他的一些变化,如下表

2020-11-05 17:43:16 37066

37066 这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。

2020-11-29 11:04:53 3879

3879

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2022-07-25 17:45:48 3057

3057

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

2021-01-31 08:12:02 8

8 使用Vivado Design Suite创建硬件。 3. 在Vitis 统一软件平台中编写软件并在板上运行。 01 导出 IP 在AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,我们创建了 1 个包含 AXI4-Lite 接

2021-04-26 17:32:26 3506

3506

1.实验目的通过例程探索Vivado HLS设计流用图形用户界面和TCL脚本两种方式创建Vivado HLS项目用各种HLS指令综合接口优化Vivado HLS设计来满足各种约束用不用的指令来探索

2021-11-06 09:20:58 6

6 Vitis HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis 应用加速开发流程中实现硬件

2022-05-25 09:43:36 1930

1930 XDC约束可以用一个或多个XDC文件,也可以用Tcl脚本实现;XDC文件或Tcl脚本都要加入到工程的某个约束集(set)中;虽然一个约束集可以同时添加两种类型约束,但是Tcl脚本不受Vivado工具管理,因此无法修改其中的约束;

2022-06-30 11:27:23 2848

2848 HLS的FPGA开发方法是只抽象出可以在C/C++环境中轻松表达的应用部分。通过使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

2022-08-02 10:10:17 1542

1542 对于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后为了统一将HLS集成到Vitis里了,集成之后增加了一些功能,同时将这部分开源出来了。Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

2023-01-15 11:27:49 1317

1317 是Vitis HLS。在Vivado 2020版本中替代原先的Vivado HLS, 功能略有差异。 HLS 的机理 简单地讲,HLS采样类似C语言来设计FPGA 逻辑。但是要实现这个目标,还是不容易

2023-01-15 12:10:04 2968

2968 Vivado是Xilinx推出的可编程逻辑设备(FPGA)软件开发工具套件,提供了许多TCL命令来简化流程和自动化开发。本文将介绍在Vivado中常用的TCL命令,并对其进行详细说明,并提供相应的操作示例。

2023-04-13 10:20:23 1551

1551 Xilinx的新一代设计套件Vivado相比上一代产品 ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。但是对初学者来说,新的约束语言 XDC 以及脚本语言 Tcl 的引入则成为

2023-04-15 09:43:09 958

958 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 674

674

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

电子发烧友网站提供《Vivado设计套件Tcl命令参考指南.pdf》资料免费下载

2023-09-14 10:23:05 1

1 电子发烧友网站提供《Vivado设计套件用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-14 14:59:39 0

0 电子发烧友网站提供《Vivado Design Suite用户指南:使用Tcl脚本.pdf》资料免费下载

2023-09-13 15:26:43 0

0 电子发烧友网站提供《UltraFast Vivado HLS方法指南.pdf》资料免费下载

2023-09-13 11:23:19 0

0 电子发烧友网站提供《将VIVADO HLS设计移植到CATAPULT HLS平台.pdf》资料免费下载

2023-09-13 09:12:46 2

2 电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

2023-11-16 09:33:36 0

0

电子发烧友App

电子发烧友App

评论