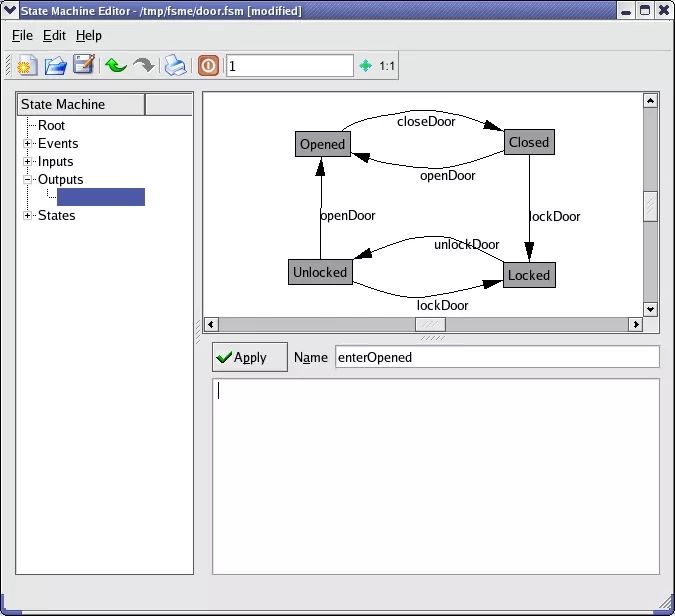

上篇文章,使用嵌套switch-case法的状态机编程,实现了一个炸弹拆除小游戏。本篇,继续介绍状态机编程的第二种方法:状态表法,来实现炸弹拆除小游戏的状态机编程。

2023-06-20 09:05:05 1190

1190

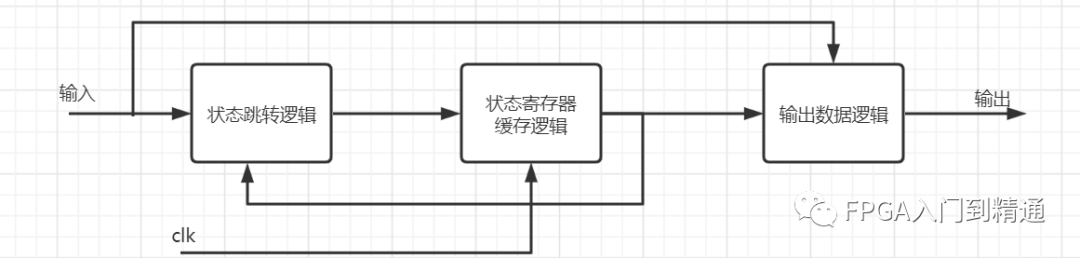

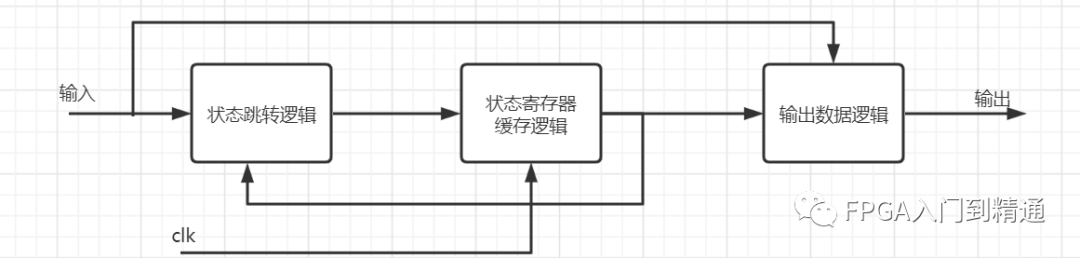

安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类型的状态机,充分掌握实现方案所需的工具和技巧,将确保您实现最佳解决方案。本文主要介绍如何在FPGA中实现状态机

2013-03-29 15:02:57 12361

12361

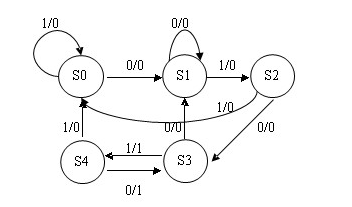

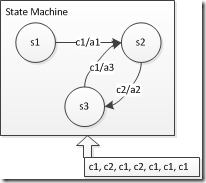

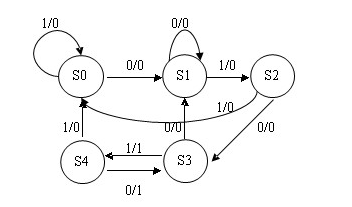

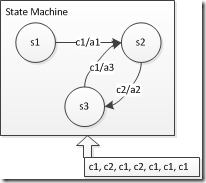

首先可以确定采用米利型状态机设计该电路。因为该电路在连续收到信号0101时,输出为1,其他情况下输出为0,所以采用米利型状态机。

2020-09-08 14:06:59 7424

7424

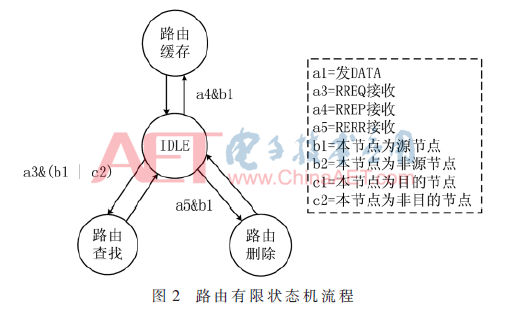

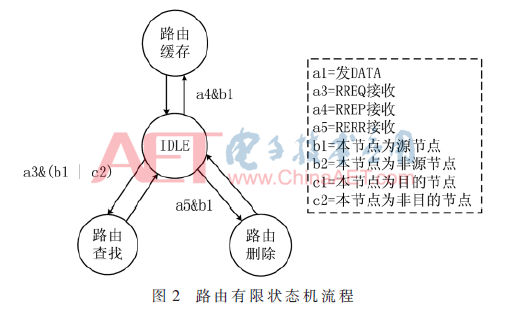

本文为在FPGA中支持DSR协议的路由表项管理功能,设计一种基于有限状态机[8]的实现方法。

2020-12-22 16:27:25 1921

1921

说起 Spring 状态机,大家很容易联想到这个状态机和设计模式中状态模式的区别是啥呢?没错,Spring 状态机就是状态模式的一种实现,在介绍 Spring 状态机之前,让我们来看看设计模式中的状态模式。

2023-12-26 09:39:02 667

667

关系,因而在状态图中每条转移边需要包含输入和输出的信息。状态编码 数字逻辑系统状态机设计中常见的编码方式有:二进制码(Binary码)、格雷码(Gray码)、独热码(One-hot码)以及二一十进制码(BCD

2012-03-09 10:04:18

今天给大侠带来如何写好状态机,状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以很多公司在硬件工程师及逻辑工程师面试中,状态机设计几乎是必选题目。本篇在引入状态机设计思想

2020-09-28 10:29:23

在FPGA/CPLD设计中频繁使用的状态机,常出现一些稳定性问题,本文提出了一些解决方法,实验表明该方法有效地提高了综合效率. 随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL

2012-01-12 10:48:26

]图1]3 基于CPLD 的FPGA 加载方案3.1]在 设备端通信产品中,基于CPLD 的FPGA 从并加载框如图2 所示,配置数据存储在FLASH 中,且在加载数据之前,CPU 通过局部总线和双倍

2019-07-12 07:00:09

加载容量最大可以达到4.125 MB。1]2 从并加载方式的实现以Xilinx 公司Spartan - 6 系列FPGA 为例,与从并加载相关的管脚如表1 所示。表1 从并加载管脚名称由表1 可以看出

2019-06-14 06:00:00

FPGA状态机的文书资料

2014-09-14 19:01:20

1.1 FPGA状态机跑飞原因分析1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA状态机跑飞原因分析;5)结束语。1.1.2 本节引言“不积跬步,无以至千里;不积小流

2021-07-29 06:15:53

和比较,并给出了FPGA与这两种DSP芯片进行链路口通倍的具体方法。在FPGA内部实现了DSP链路口的设计,同时给出了DSP进行链路口通信的具体设置方法。由于实时处理中数据的重发会严重影响处理的实时性

2019-06-19 05:00:08

和比较,并给出了FPGA与这两种DSP芯片进行链路口通倍的具体方法。在FPGA内部实现了DSP链路口的设计,同时给出了DSP进行链路口通信的具体设置方法。由于实时处理中数据的重发会严重影响处理的实时性,故

2018-12-04 10:39:29

及路线图详见报到通知)四、 课程简介本课程为期三天,旨在帮助已经掌握一定设计基础的工程师进一步了解FPGA逻辑设计的方法与优化技巧。讲述了逻辑设计的验证、高级状态机的设计、基于FPGA的DSP设计方法

2009-07-24 13:13:48

[table][tr][td] Fpga 学习笔记7(状态机设计实例):因内容比较简单,而且在这篇日志中也有相关的知识点,就不写了。该集主要知识点:1、利用状态机实现滤除物理按键所产生的抖动波形。2

2018-07-03 10:45:39

状态机设计指导

2012-08-20 23:45:55

本帖最后由 eehome 于 2013-1-5 09:56 编辑

状态机设计的例子

2012-08-19 23:01:07

状态机设计中always @(*) beginnext = 2'bx;case (state)idle: next=s1;s1: next=s2;s2: next=idle;end以上代码先给

2021-10-06 18:49:10

不用再花费大量时间等待生成BIT文件下载到FPGA才能实际验证。下面我们以简单的QPSK调制解调为例,为大家展示AD9361+Simulink是如何快速搭建链路并实时仿真的。首先我们在simulink

2016-11-25 17:38:07

AX58x00系列EtherCAT从站芯片有哪些优点?AX58x00系列EtherCAT从站芯片有哪些应用?

2021-08-20 07:55:27

本帖最后由 afnuaa 于 2017-5-24 11:22 编辑

状态机是一种普遍而有效的架构,我们可以利用状态机设计模式来实现状态图或流程图的算法。State Machines

2017-05-23 17:11:34

STM32F303+LAN9252的EtherCAT下位机设计从去年年末接触EtherCAT总线以来,由于其他一些工作原因,前期设计的基于STM32F303+LAN9252开发板一直未能跑通,仅实现

2021-08-04 06:38:32

本帖最后由 御宇1995 于 2015-6-6 15:06 编辑

实验课要用FPGA(Altera的cycloneIV)实现交通灯,有用状态机和非状态机两种方法,以下是代码状态机实现(一个数

2015-06-06 15:03:52

PC 上运行的 EtherCAT 主站软件与 Spartan-6 FPGA 之间的通信。

在这方面有专业知识的人能否提供以下建议?

兼容性:XMC4300 从控制器与 Spartan-6 FPGA

2024-03-06 07:47:12

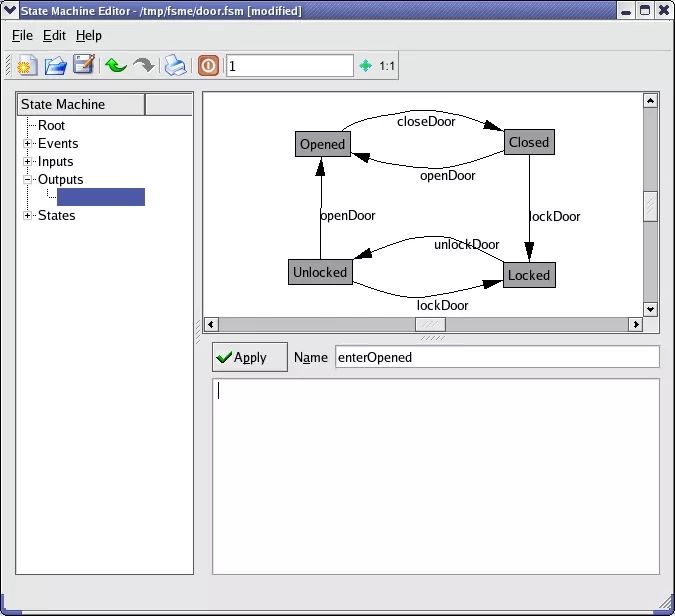

异步或者同步复位来确保状态机上电有个初始态。实验步骤:为了实现让FPGA输出一个HELLO字符串,首先画出其状态转移图,如图8-3所示。图8-3 “HELLO”状态转移图由上图可以看出如果在任意态不符合

2016-12-26 00:17:38

的资源、布局等2、安装linux系统,并安装EtherCAT的相关软件3、进行实验演示4、撰写结项报告试用目的:了解EtherCAT协议,熟悉EtherCAT从站协议在linux系统下部署的方法,并将成果应用于实际场景之中。

2017-06-02 16:07:31

申请理由:项目描述:1.使用开发板作为EtherCAT从站微处理器,配合自己设计的基于ET1100的从站控制器,搭建基于EtherCAT工业以太网的电机控制平台,或者用来实现图像高速采集2.本人双

2016-11-07 16:37:23

项目名称:基于I.MX 6UL的EtherCAT从站的设计试用计划:EtherCAT(以太网控制自动化技术)是一个以以太网为基础的开放架构的现场总线系统,它是一个开放源代码,高性能的系统,目的是利用

2017-06-23 17:18:25

亚信电子(ASIX Electronics Corporation)于2019年推出最新一代小封装并集成两个百兆以太网PHY的EtherCAT从站专用通讯SoC解决方案「AX58200 2/3端口

2020-04-20 14:34:08

Corporation)继2018年推出第一代大中华地区首款AX58100 EtherCAT从站控制芯片,2019年推出新一代小封装的AX58200 2/3端口EtherCAT从站专用通信SoC后,亚信电子

2021-11-24 11:45:02

本次EtherCat主站移植是基于SOEM源码进行移植,收集并整理部分资料作为学习EtherCat通讯参考内容。一 、T EtherCAT主站 M SOEM源码解析 ----M EEPROM访问1

2023-04-17 10:29:28

通过简单的例子介绍了FPGA设计中最常见的设计思想——状态机,通过状态机,可以实现很复杂的时序控制内容,学好状态机,是掌握FPGA技术的重中之重。接下来,大家请看视频教程,由于视频中有部分网络的链接

2015-09-25 12:26:01

,主要通过独立按键消抖这样一个实验,来进一步举例讲解状态机的设计思想,独立按键消抖有多种方式可以实现,这里采用状态机的方式,既能方便大家理解按键消抖的整个过程,又能进一步领会状态机的设计思想。 接下来

2015-09-29 14:19:42

笔试时也很常见。[例1] 一个简单的状态机设计--序列检测器序列检测器是时序数字电路设计中经典的教学范例,下面我们将用Verilog HDL语言来描述、仿真、并实现它。序列检测器的逻辑功能...

2022-02-16 07:29:49

介绍EtherCAT从站设备仿真功能的应用情境,与如何开启亚信AX58100 EtherCAT从站芯片的设备仿真(Device Emulation)功能。

2021-02-08 18:12:37

其它的EtherCAT从站控制器解决方案,AX58100已集成两个可同时支持光纤和铜线网络应用的高速以太网PHY并支持一些额外的控制接口,例如脉冲宽度调制(PWM)接口,增量(ABZ)/霍尔编码器接口

2018-08-21 12:15:39

:分布时钟—从器件和主器件上的高精度时间同步方法。支持环回的快速链路断开检测(需要以太网物理层 (PHY) 收发器支持)--当以太网PHY检测到一个链路断开时,它通知EtherCAT硬件。在10µs内

2018-09-06 15:25:39

。 可能会出现一些错误,这些错误需要在验证过程中利用测试矢量找到。 对于在图形用户界面中进行的所有小更改,都需要重复此验证过程。图1. 数字电源图形用户界面 还有一种更方便的方式是选择基于状态机的数字电源

2018-10-09 10:36:37

。可能会出现一些错误,这些错误需要在验证过程中利用测试矢量找到。对于在图形用户界面中进行的所有小更改,都需要重复此验证过程。图1. 数字电源图形用户界面图2. 基于状态机的ADP1055框图还有一种更

2018-10-18 11:25:17

。可能会出现一些错误,这些错误需要在验证过程中利用测试矢量找到。对于在图形用户界面中进行的所有小更改,都需要重复此验证过程。图1. 数字电源图形用户界面还有一种更方便的方式是选择基于状态机的数字电源控制器

2018-10-16 12:56:53

基于EtherCAT的主站通信控制器设计

2016-09-20 16:05:02

AD9361的AD数据,并连接的到simulink仿真链路中进行实时的仿真。HIL_RX连接链路后的结构图。使用软硬件协同仿真的结构,能实时的抓取无线信号并进行仿真,验证算法实现的正确性能。首先确保了仿真信号

2019-02-19 10:52:13

EVB-LAN9252-DIGIO,LAN9252 DIGIO评估板满足仅对硬件EtherCAT从设备的需求,并使用LAN9252实现这一目标。我们将DIGIO接口与控制信号一起暴露,无需连接MCU

2020-05-25 09:11:08

基于赛灵思的FPGA的EtherCAT主站总线控制 ,论坛有做运动控制这方面的技术吗?目前我已实现带32轴同步运行,同步抖动±75ns,控制精度125us。感兴趣的可以一起探讨下

2018-07-23 12:00:39

一篇经典文献,详细讲解了一段、两段、三段式状态机的实现,效率、优缺点。看完后相信会对状态机有一个详细的了解。 状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许 多公司

2011-10-24 11:43:11

完全自主可控ethercat从站 ip核,有源码和testcase,有兴趣的可以访jingfengxun.com,也可以私信。

2017-08-22 20:27:30

于Linux系统的免费开源EtherCAT主站程序,框架如下所示。图 3IgH EtherCAT主站通过构建Linux字符设备,应用程序通过对字符设备的访问实现与EtherCAT主站模块的通信。IgH

2021-10-29 11:17:36

设计要求:1、 带EtherCat主站接口。2、 总从站最多32个。3、 伺服从站最多16个。4、 有一组伺服可以实现两轴同步功能。5、有用户程序空间(PLC的功能)联系方式:杨先生***。

2021-08-19 15:30:07

(SoC))上实施全新、低成本、无 DDR 的 EtherCAT 从站的参考设计。此参考设计展示了完全在 SoC 内部存储器中运行整个 EtherCAT 从站堆栈的能力。通过消除外部 ASIC 和 DDR

2018-10-16 10:43:09

本文考虑了系统的综合要求:系统容量、作用距离、收发时延及算法实现复杂度,采用了8倍图像压缩、RS编码加交织的方式进行了无线链路的设计,采用大规模FPGA完成发送端及接收端的算法实现,并通过试验验证设计指标满足系统要求。

2021-05-31 07:00:51

1.状态机设计原则2.状态机练习13.状态机练习1答案4.波形对比方法5.状态机练习26.状态机练习2答案7.状态机练习38.状态机练习3答案9.状态机练习410.状态机练习4答案11.状态机练习

2015-10-31 13:52:12

C2000实时控制微控制器(MCU)的EtherCAT从站节点的硬件开发。该博文概述了EtherCAT技术非常适合工业自动化应用中C2000 MCU的原因,以及为何TI DesignDRIVE团队

2022-11-09 07:01:29

同步模式。自由运行由从站自主控制运行周期,一般用于开机初始化过程中,主要完成一些初始化工作和状态机的切换。DC同步模式受DC同步信号的控制,DC触发的周期由主站设置,DC的脉冲宽度可以再XML文件

2019-12-10 18:04:04

EtherCAT实现的特点和优势。在第3部分中,我们将详细介绍自行开发从站节点应用程序的三个阶段,并介绍TI C2000 controlSUITE™软件中的EtherCAT包如何为每个阶段提供支持

2022-11-09 07:24:31

本帖最后由 eehome 于 2013-1-5 09:56 编辑

高效安全的状态机设计

2012-08-13 17:53:44

高级数据链路控制涉及三种类型的站,即主站、从站和复合站。 主站的主要功能是发送命令(包括数据信息)帧、接收响应帧,并负责对整个链路的控制系统的初启、流程的控制、差错检测或恢复等。

2019-11-01 09:10:17

如何写好状态机:状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入

2009-06-14 19:24:49 96

96 状态机设计:8.1.1 数据类型定义语句TYPE语句的用法如下:TYPE 数据类型名IS 数据类型定义OF 基本数据类型;或TYPE 数据类型名IS 数据类型定义;TYPE st1 IS ARRAY ( 0 TO 15 ) OF STD_L

2009-08-09 23:07:03 36

36 本文给出了采用这些技术的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。

为了使FPGA或CPLD中的状态机设计

2009-04-15 11:27:04 600

600

有限状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个时序逻辑函数,传统的电路图输入法通过直接设计寄存器组来实现各个状态之间的转换, 而用硬件描述语言来描述有限

2011-11-11 09:49:28 1887

1887

本文给出了采用这些技术的高速环境状态机设计的规范及分析方法和优化方法,并给出了相应的示例。

2011-12-16 10:09:43 1296

1296

设计并实现了一种基于状态机的串口通信协议,并将此协议应用到称重仪表的上位机通信中。本文介绍了串口通信协议的数据包格式以及其通信状态机,并给出了协议实现的部分示例代

2012-05-08 15:22:27 169

169 为了能够更简洁严谨地描述MTM总线的主模块有限状态机的状态转换,同时减少FPGA芯片功耗,提高系统稳定性,文中在分析MTM总线结构和主模块有限状态机模型的基础上,基于VHDL语言采

2012-05-29 15:39:09 20

20 状态机原理及用法状态机原理及用法状态机原理及用法

2016-03-15 15:25:49 0

0 本文主要介绍了IP模块的有限状态机的实现。

2016-03-22 15:42:47 0

0 本文提出一种优秀 、高效的 Verilog HDL 描述方式来进行有限状态机设计 介绍了 有限状态机的建模原则 并通过一个可综合的实例 验证了 该方法设计的有限状态机在面积和功耗上的优势。

2016-03-22 15:19:41 1

1 EDA的有限状态机,广义而言是指只要涉及触发器的电路,无论电路大小都可以归结为状态机。有限状态机设计在学习EDA时是很重要的一章。

2016-06-08 16:46:10 3

3 FPGA学习资料教程——华清远见FPGA代码-状态机

2016-10-27 18:07:54 9

9 练习九.利用状态机的嵌套实现层次结构化设计目的:1.运用主状态机与子状态机产生层次化的逻辑设计;

2017-02-11 05:52:50 3126

3126

EtherCAT是一种实时工业以太网协议,使用链路冗余技术是实现链路稳定性和可靠性的重要手段。介绍了基于FPGA的EtherCAT链路冗余原理,设计通过FPGA实现主站与从站、从站与从站之间的通信

2017-11-15 12:42:13 6654

6654

本篇文章包括状态机的基本概述以及通过简单的实例理解状态机

2019-01-02 18:03:31 9928

9928

状态机可以用两种方法实现:竖着写(在状态中判断事件)和横着写( 在事件中判断状态)。这两种实现在本质上是完全等效的,但在实际操作中,效果却截然 不同。

2019-10-09 07:09:00 2306

2306 状态机可以用两种方法实现:竖着写(在状态中判断事件)和横着写( 在事件中判断状态)。这两种实现在本质上是完全等效的,但在实际操作中,效果却截然 不同。

2019-10-09 07:08:00 1603

1603 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-10-09 07:07:00 3198

3198 状态机有三种描述方式:一段式状态机、两段式状态机、三段式状态机。下面就用一个小例子来看看三种方式是如何实现的。

2019-08-29 06:09:00 2514

2514

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-10-09 07:02:00 2138

2138 状态机可归纳为4个要素,即现态、条件、动作、次态。这样的归纳,主要是出于对状态机的内在因果关系的考虑。“现态”和“条件”是因,“动作”和“次态”是果。

2019-10-09 07:04:00 1882

1882 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为摩尔(Moore)型状态机和米莉(Mealy)型状态机。

2019-05-28 07:03:49 2648

2648 是FPGA设计中一种非常重要、非常根基的设计思想,堪称FPGA的灵魂,贯穿FPGA设计的始终。 02. 状态机简介 什么是状态机:状态机通过不同的状态迁移来完成特定的逻辑操作(时序操作)状态机是许多数字系统的核心部件, 是一类重要的时序逻辑电路。通常包括三个部分: 下一个

2020-11-05 17:58:47 6145

6145

玩单片机还可以,各个外设也都会驱动,但是如果让你完整的写一套代码时,却无逻辑与框架可言。这说明编程还处于比较低的水平,你需要学会一种好的编程框架或者一种编程思想!比如模块化编程、状态机编程、分层思想

2021-07-27 11:23:22 19225

19225

经典双进程状态机的FPGA实现(含testbeach)(肇庆理士电源技术有限公司图片)-该文档为经典双进程状态机的FPGA实现(含testbeach)总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-08-31 13:26:52 3

3 用状态机设计A_D转换器ADC0809的采样控制电路实验(通信电源技术期刊版面费)-用状态机设计A_D转换器ADC0809的采样控制电路.适合新手学习参考

2021-09-16 12:05:05 28

28 share,作者:亚索老哥)),原来状态机还可以这么简单地玩~~亚索老哥提出的状态机六步法(1)、定义状态接口(2)、定义系统当前状态指针(3)、定义具体状态,根据状态迁移图来实现具体功能和状态切换(4)、定义主程序上下文操作接口(6)、主程序通过上下文操作接口来控制系统当前状态的变化亚索老哥的状态机例程

2021-12-16 16:53:04 7

7 (41)FPGA状态机一段式1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA状态机一段式5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:59 0

0 LABVIEW的状态机实现资料合集

2022-01-04 11:18:40 41

41 嵌入式状态机是一种常用的软件设计模式,它能够提高代码的可读性和可维护性。状态机是一个抽象的概念,它描述了一个系统或者组件的不同状态以及在不同状态下如何响应输入和事件。状态机可以应用于各种领域,比如通信协议、嵌入式系统、控制系统等。

2023-04-14 11:55:10 1035

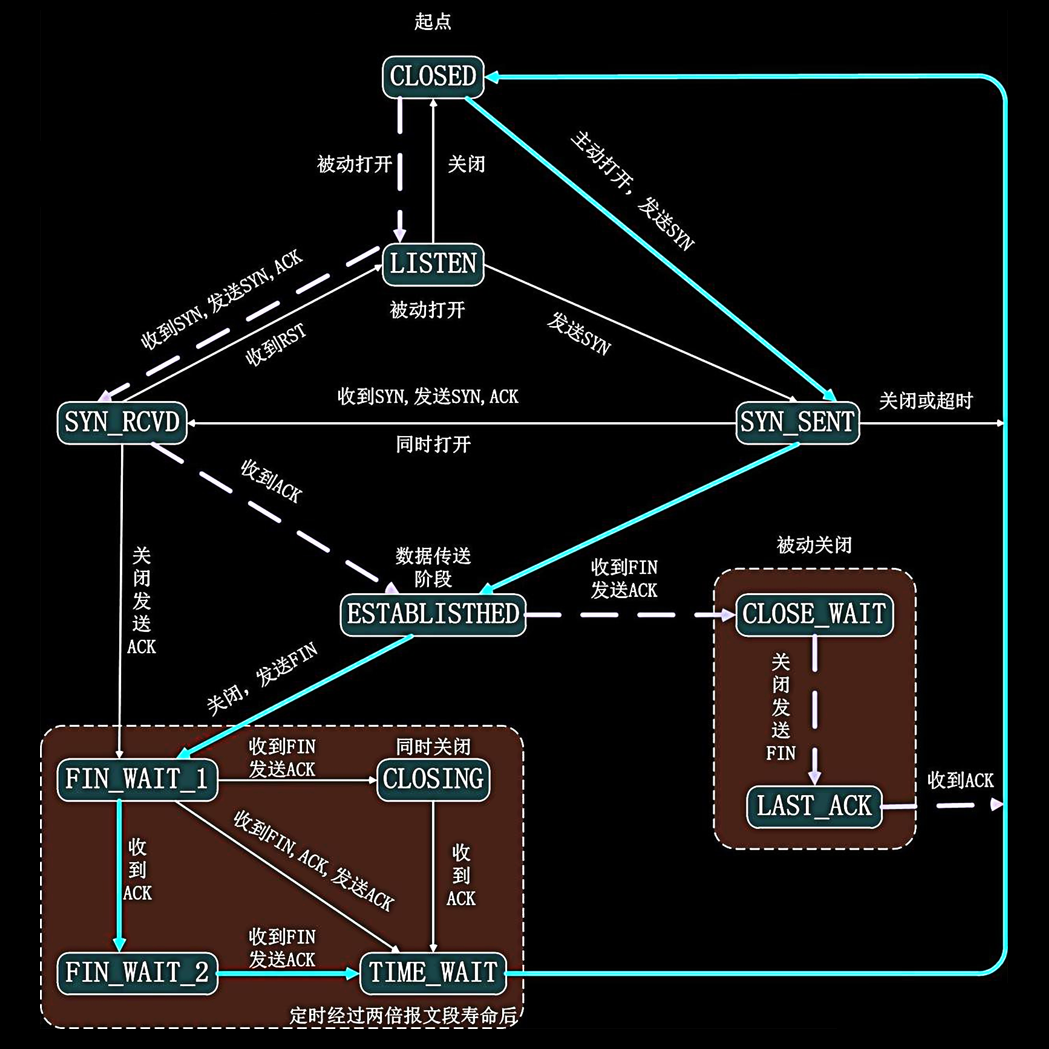

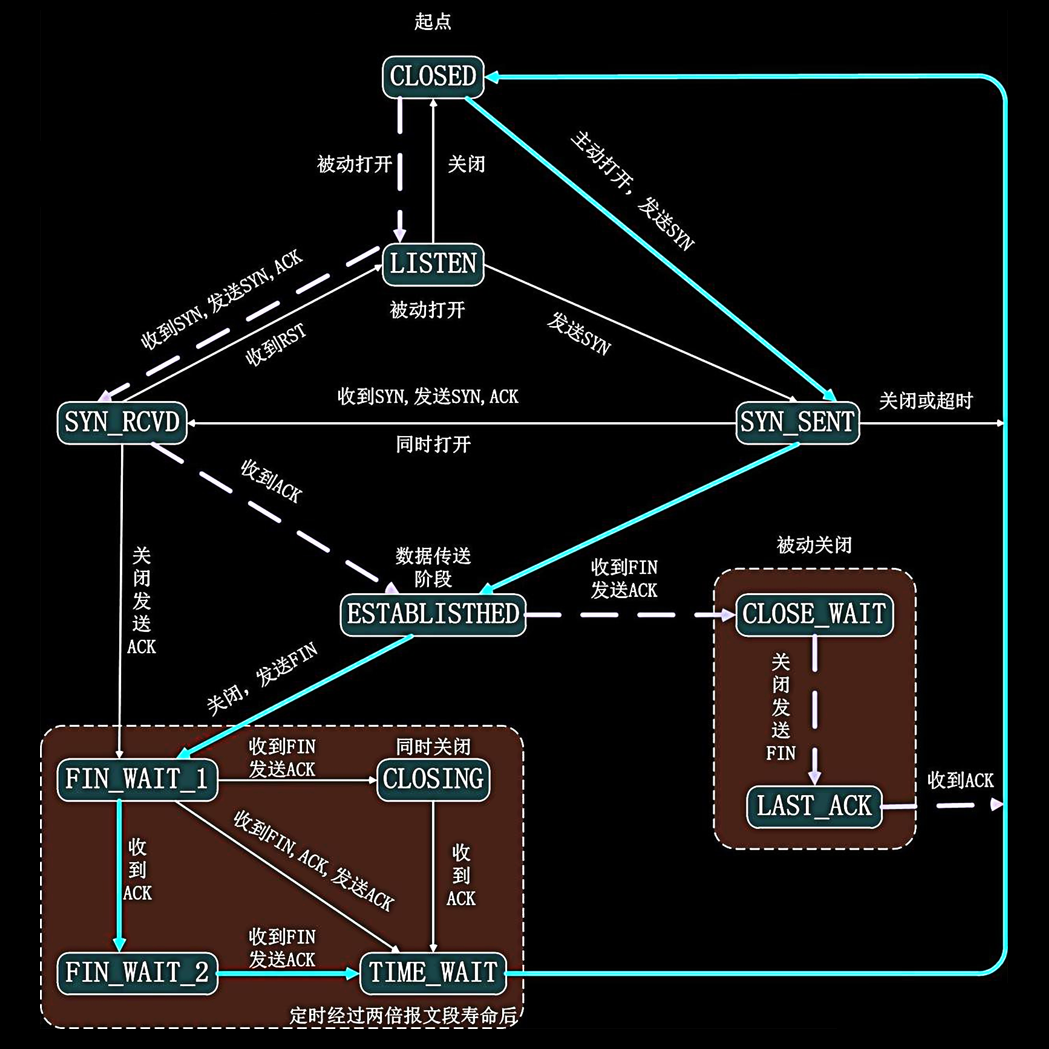

1035 TCP状态机是TCP连接的变化过程。TCP在三次握手和四次挥手的过程,就是一个TCP的状态说明,由于TCP是一个面向连接的,可靠的传输,每一次的传输都会经历连接,传输,关闭的过程,无论是哪个方向的传输,必须建立连接才行,在双方通信的过程中,TCP的状态是不一样的

2023-04-21 11:47:57 1005

1005

FPGA的特点是并行执行,但如果需要处理一些具有前后顺序的事件,就需要使用状态机。

2023-05-22 14:24:12 559

559

状态机模式是一种行为模式,通过多态实现不同状态的调转行为的确是一种很好的方法,只可惜在嵌入式环境下,有时只能写纯C代码,并且还需要考虑代码的重入和多任务请求跳转等情形,因此实现起来着实需要一番考虑

2023-06-22 14:26:00 411

411

状态机往往是FPGA 开发的主力。选择合适的架构和实现方法将确保您获得一款最佳解决方案。 FPGA 常常用于执行基于序列和控制的行动, 比如实现一个简单的通信协议。对于设计人员来说,满足这些行动

2023-07-18 16:05:01 500

500

状态机的基础知识依然强烈推荐mooc上华科的数字电路与逻辑设计,yyds!但是数电基础一定要和实际应用结合起来,理论才能发挥真正的价值。我们知道FPGA是并行执行的,如果我们想要处理具有前后顺序的事件就需要引入状态机。

2023-07-28 10:02:04 457

457

有限状态机,简称状态机,通俗的说,就是把全部的情况分成几个场景,这些场景的工作方式明显不同。简单来说就是如下所示的状态转移图

2023-08-31 15:30:49 585

585

定制状态机 目前得到的状态机已经能够响应来自外部的各种事件,并适当地调整自己当前所处的状态,也就是说已经实现了状态机引擎的功能,接下来要做的就是根据应用的具体需求来进行定制,为状态机加入与软件系统

2023-09-13 16:57:37 823

823

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,状态机被广泛应用于各种场景,如CPU指令集、内存控制器、总线控制器等。

2023-10-19 10:27:55 3419

3419

电子发烧友App

电子发烧友App

评论