随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2015-02-02 17:32:52 2204

2204

GMII、SGMII和SerDes的区别和联系? GMII和SGMII区别,上一篇已经介绍了,这一篇重点介绍SGMII和SerDes区别。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29958

29958

端高速串行信号重新转换成低速并行信号。 采用SerDes技术的高速串行接口增加了带宽,减少了信号数量,同时带来了诸如减少布线冲突、降低开关噪声、更低的功耗和封装成本等许多好处,相比传统并行总线架构有不少的提升。 并行接口与SerDes 串行接口和并行接口的发展

2023-10-12 09:02:14 1624

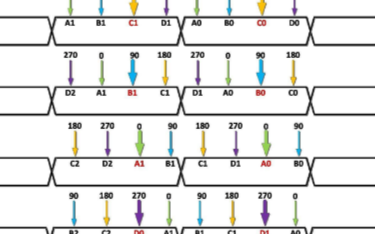

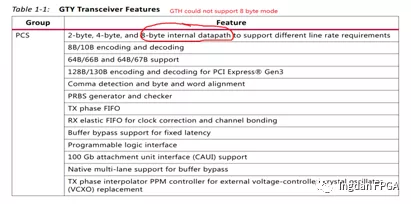

1624 10Gbps的数据,再进行后续的处理。在100G流量获取中,包括PMA、PCS和MAC共三个模块。PMA实现100GE的介质接口,由高性能FPGA自带的高速SERDES实现,一个100GE接口需要10路高速

2014-10-25 16:20:12

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-05-29 17:52:03

随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。

2019-05-23 07:42:43

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02:12

SerDes的发送端TX的均衡原理是什么?怎样利用高速接口SerDes去实现芯片间信号的有线传输?

2021-06-17 07:15:16

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。a)、时钟...

2021-07-28 08:35:42

是否可以将数据总线宽度配置为24位?我检查了8, 16位和32位之间的差异,只改变了最后8位中的第七十九行(CyuU3pIPIBGPGIFIFBuxCONFIG)。我需要24位数据宽度和SPI为我的启动从SPI闪存(固件)。如果我查看数据表中的PIN表,可以看到数据总线和SPI总线之间没有交叉点。

2019-08-21 09:02:22

,极其注重精确性与快速性,GPMC并口“小数据-低时延”的特点显得格外耀眼,能够很好地提高数据传输效率,降低传输成本。

(2)大数据-高带宽

大数据时代对能源电力领域的数据量传输、数据处理等方面

2023-08-22 10:58:39

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

并口“小数据-低时延”的特点显得格外耀眼,能够很好地提高数据传输效率,降低传输成本。

(2)大数据-高带宽大数据时代对能源电力领域的数据量传输、数据处理等方面提出了更高的要求。GPMC提供了最大

2023-09-30 23:43:29

接口,及串行EPROM接口。LOCAL总线的数据宽度为32位,时钟频率可达到50MHZ, 并且支持数据预取功能。PCI9054的总线操作包括PCI总线操作和本地总线操作。对于PCI总线操作,它完全遵守

2008-10-09 11:23:38

:PCI总线接口,LOCAL总线接口及串行EPROM接口。LOCAL总线的数据宽度为32位,时钟频率可达到50MHz并且支持数据预取功能。PCI9054的总线操作包括PCI总线操作和本地总线操作。对于PCI

2018-12-05 10:12:42

目录1、cpu处理的数据宽度2、数据总线宽度3、地址总线宽度4、性能差别1、cpu处理的数据宽度CPU处理的数据的宽度,参与运算的寄存器的数据长度代表单片机的位数。也就是一个一个时钟周期里,处理器

2021-07-13 06:20:07

嗨,我在我的项目中使用SRIO Gen2 v4 ipcore。我已经在kintex 7(xc7k160t)中实现了它。生成的ipcore具有数据宽度为64的用户axi接口。有没有选项可以将用户界面总线宽度更改为32或16.我无法在ipcore GUI中找到这样的选项。

2020-04-27 09:52:17

引进。我们在研制某新型飞机火控雷达系统的检测设备的过程中,组建了VXI总线雷达自动检测系统。在研制该系统过程中,我们开发了一种利用CPLD和双口RAM设计的寄存器基VXI总线仪器接口电路,下面我们就这一

2018-11-27 11:48:33

串随着数据速率的增加,有关实施并行总线的问题也随之增多。较快总线比较慢总线功耗高,而且由于定时容差的降低,信道数量的增加,布局难度也越来越大。随着数据速率的增加,保持信道间的时滞也日益重要,原因是较大的时滞差异会导致系统定时问题…

2022-11-21 06:38:25

如何利用以太网硬件协仿真接口实现便捷和高带宽的仿真?

2021-05-28 06:36:35

的命令队列。这样不同的端口都可以访问Memory接口,完成对Memory的读写操作。MPFE都是基于Avalon总线的时序进行地址、命令和数据的交互的。在实际有效带宽一定的情况下,MPFE可以将带宽按照

2019-06-13 05:00:06

TMS320C32的外部存储器接口的特点 TMS320C32是一个32位微处理器,它可以通过24位地址总线、32位数据总线和选通信号对外部存储器进行访问。其外部存储器接口结构如下图l所示。 在图l中

2019-06-14 05:00:08

带宽、易扩展等优点,已经逐渐成为现代数据传输的发展趋势。基于USB的数据采集系统充分利用USB总线的上述优点,有效地解决了传统数据采集系统的缺陷。USB的规范能针对不同的性能价格比要求提供不同的选择,以

2009-04-11 17:20:15

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

(ALE)信号支持区分地址与数据周期.

[size=13.3333330154419px]其实其他系列也都有的。

外部总线接口有下列功能:

支持外部设备最大64K字节 (8位数据宽度

2023-06-16 06:41:36

如何利用485总线去传输数据呢?传输过程是怎样的?

2022-03-01 07:39:30

什么是DSP流水线协议?如何利用FPGA与ADSP TS201去设计总线接口?

2021-04-28 06:31:06

在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂算法处理上的优势,DSP+FPGA的实时信号处理系统的应用越来越广泛。那么,我们该怎么利用FPGA与ADSP TS201设计总线接口呢?

2019-08-09 06:56:11

PCI总线是什么?有什么特点?如何利用FPGA去设计PCI总线的接口电路?设计PCI总线接口时应注意哪些问题?

2021-05-31 06:37:24

本文将以嵌入式实时视频数据存储系统为例,说明如何利用FPGA作为嵌入式处理器的数据协处理器,利用CPLD进行主处理器与协处理器之间数据通信的方案来解决处理器接口总线速度对系统性能的影响。该方案对解决类似的问题具有一定的参考作用。

2021-05-10 06:30:18

什么是PCI总线?它有什么特点?如何利用FPGA设计PCI总线的接口电路?设计PCI总线接口时应注意哪些问题?

2021-04-29 06:10:31

如何利用双端口RAM去实现PCI总线接口?

2021-05-06 06:30:53

`我们都知道CAN 总线以其可靠性高、成本优等特点在汽车、工业局域通讯得到广泛应用。但是随着各种专用控制器的蓬勃发展,控制功能的需求逐渐复杂多样化,随之带来的是各控制器之间的交互也日趋复杂。CAN

2019-12-19 15:09:07

Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

2019-10-21 07:09:44

嗨,在xilinx应用笔记(XAPP973第2页)中,我发现声明“iMPACT仅支持通过Virtex-5 FPGA系列成员进行间接编程的16位数据总线宽度。”它是否仍适用于Virtex 6 FPGA

2020-06-08 13:10:56

带来了总线效率的问题,针对变长数据输入的情景,当芯片内部总线位宽变大时,若每个总线字在数据传输过程中不能被有效利用,则可能导致总线效率降低。原作者:徐铭伟、刘欢

2022-10-11 14:27:34

是高精度的在线测量设备,应用于扁平吊带的自动宽度测量当中,可配备软件分析系统,为您带来高质量的多种数据信息,提升生产效率,对扁平吊带进行实时监测。</p> 扁平吊带宽度的在线精准测量`

2018-12-13 10:09:58

的,但是现在提一下,基频的计算方式,若当前serdes传输0101的方波pattern,可以使得信号变化最剧烈,这时候信号的带宽是最高的,方波信号的周期就是data rate/2。例如:一个时钟信号

2023-03-24 15:12:28

PCI总线特点及开发现状PCI接口配置空间的实现求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案

2021-04-15 06:17:20

使用 cyusb3014 主模式时出现数据宽度问题。

我将 AutoMaster 的示例更改为在 FPGA 中访问标准 FIFO。 有两个变化:

1. GPIF 状态机要兼容标准 FIFO 接口时序

2024-02-23 06:16:59

传输,最大总线速度是40 MB/s。1996年的新标准VME64(ANSI/VI-TA1-1994)将总线数据宽度提升到64位,最大数据传输速度为80 MB/s。而由FORCE COMPUTERS制定

2019-04-22 07:00:07

;(2)设置本地数据总线的宽度是16位时,分别表示(高字节有效)、(低字节有效)、LA1(地址位1)信号::,LD[07..00]有效;:LA1;:没有使用;:,LD[15..08]有效;(3)设置

2019-05-30 05:00:02

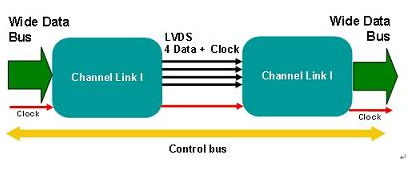

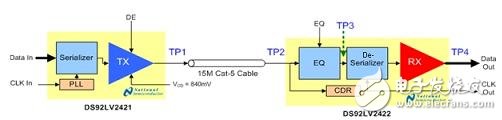

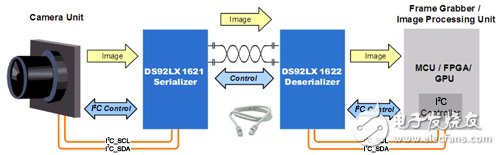

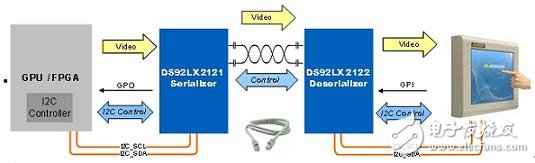

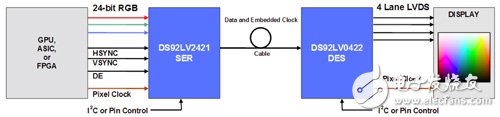

姚琳为了满足视频系统、工业和医疗显示和视频传送等应用消除较长连接电缆限制、提高数据速率,以及需要双向传输辅助数据的要求,Intersil公司推出了一款采用双向I2C接口的SERDES IC

2019-05-08 07:00:01

亲爱的先生,FX3支持32位GPIF II接口。我们使用GPIF设计器1来绘制接口和状态机图。在接口中只有8、16、24、32选择GPIF数据总线宽度。但是我需要12 GPIF数据总线。请帮助选择12位GPIF数据总线。谢谢你最好的问候,拉米什

2019-09-17 12:28:17

求一频带宽度测量量方法。

2012-04-08 10:42:06

SERDES结构是怎样构成的?高速SERDES接口在网络方面有哪些应用?

2021-04-28 07:19:38

利用单总线传输数据与电源

2009-05-04 13:33:12 28

28 PCI 总线是先进的高性能32/64 位局部总线,成为微机总线标准。PCI 总线接口设计较其它总线接口设计复杂,本文讨论了接口设计的方案,选择CH365 作为接口芯片,描述了数据采集

2009-08-19 10:19:55 27

27 提出了一种利用USB总线接口的数据采集系统的设计方案,并给出了系统的硬件与软件的具体实现方法。通用串行总线作为一种崭新的微机总线接口规范,其特点十分适合应用

2009-08-31 11:40:19 19

19 M31 SerDes PHY IP M31 SerDes PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。SerDes IP支持从1.25G到10.3125Gbps的数据速率

2023-04-03 20:29:47

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

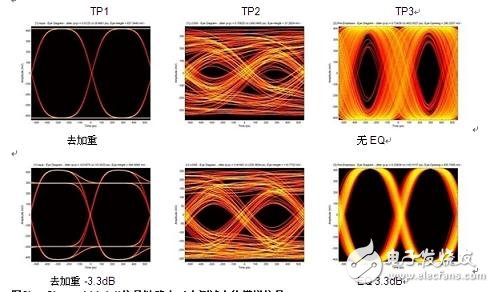

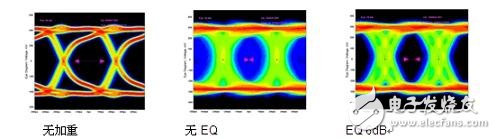

38 利用眼图模板评估串行器和解串器(SerDes)的性能

Abstract: Maxim has developed a family of serializer and deserializer

2008-11-26 14:08:24 2054

2054

利用TJA1080的FlexRay总线接口设计

介绍基于TJA1080的FlexRay总线在数字信号处理器(DSP)C5509上的实现。整个系统以DSP为核心,采用TJA1080总线控制器实现F

2009-03-29 15:13:40 9009

9009

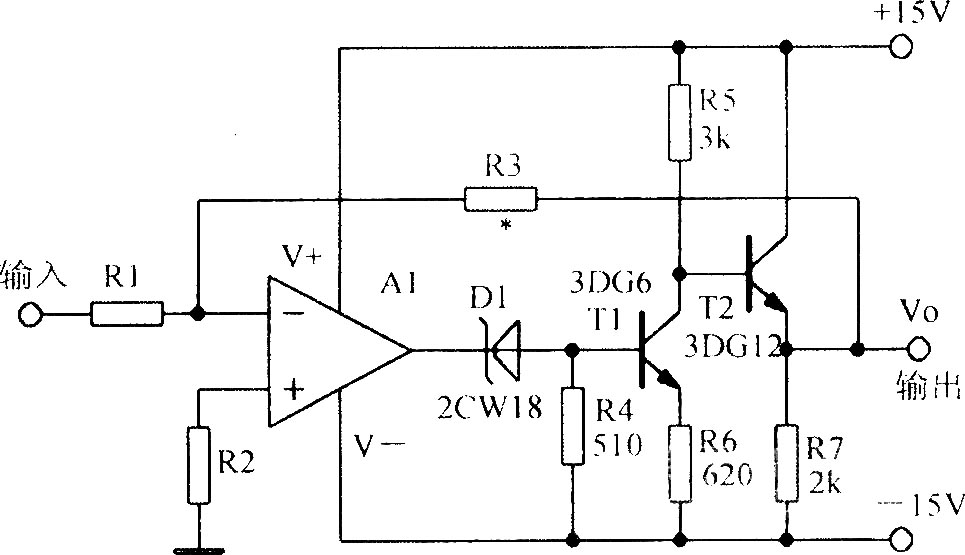

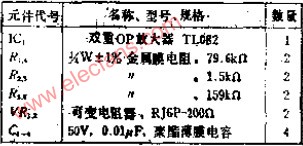

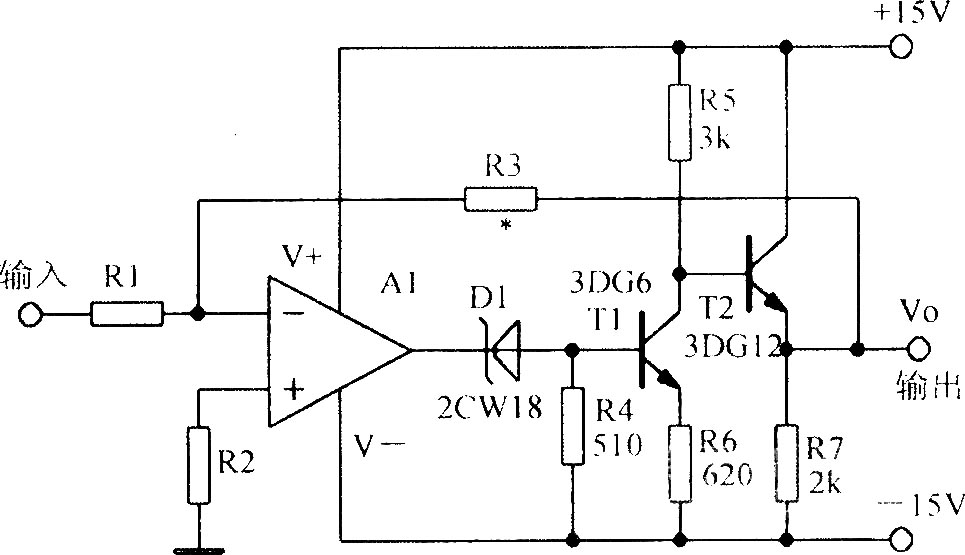

能够扩展频带宽度的放大电路图

2009-04-02 15:54:42 1414

1414

条码打印机的碳带宽度/碳带长度 碳带宽度

2009-12-30 11:49:58 1797

1797 什么是数据总线宽度/地址总线宽度?

数据总线宽度

数据总线负责整个系统的数据流量的大

2010-02-04 10:25:01 6588

6588 高带宽嵌入式应用中SoC微控制器的新型总线开发

传统SoC总线架构已不能满足新的联网嵌入式设计对高带宽数据流进行实时控制的需求, NetSilicon开发的可编程总线带宽

2010-03-03 16:16:51 622

622

什么是交换带宽/背板带宽

交换机的背板带宽,是交换机接口处理器或接口卡和数据总线间所能吞吐的最大数据量。背板带宽标志了交

2010-04-07 16:35:17 720

720 可扩大通带宽度的有源双调谐电路

电路的功能

带通滤波器为了获得

2010-05-14 12:04:44 1037

1037

PC/104作为一种嵌入式总线标准已经被很多控制系统所采用,而PCIE/104接口的提出将未来最为流行的串行差分总线结构,引入到了这种嵌入式总线标准,从而为各种高速、高带宽的嵌入式系

2011-08-17 11:04:06 4109

4109

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架构。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线

2017-10-26 15:37:45 4

4 Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

2019-05-24 15:33:25 4072

4072

只要SERDES接口的高级架构是合理的,SERDES总线的成功实现就归结为“实现细节”。

2019-08-14 17:57:00 2615

2615 很多人把计算机总线宽度和总线带宽混为一谈,其实他们是不一样的。

2019-09-01 09:52:44 13427

13427 串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。

2020-05-18 10:51:18 2964

2964

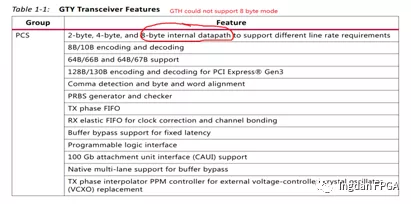

总线而成为高速接口设计的主流。 如今,随着SerDes接口的广泛应用,许多高端的FPGA都内嵌有SerDes接口硬核。在FPGA中内嵌的SERDES的硬核,可以大大地扩张FPGA的数据吞吐量,节约功耗,提高性能,使FPGA在高速系统设计中扮演着日益重要的角色。 国产

2020-07-28 12:05:16 1128

1128 速度的并行总线传输串行化的数据。一个实例是用单个PCI-Express 通道,替代传统的32 位、64MHz PCI 总线(可达到2.112Gb/s) ,仅用4 条线(运行在2.5GHz) ,可达到4Gb/s总数据率。简言之, SERDES 协议允许用较少的引脚数传输较高的数据率。

2020-10-09 17:25:07 18

18 因为摄像头输出的LVDS信号速率会达到600Mbps,我们将不能够通过FPGA的I/O接口直接去读取这么高速率的信号。因此,需要使用Xilinx FPGA内的SerDes去实现高速数据的串并转换。

2020-12-30 17:24:00 39

39 AD5425:带串行接口的8位高带宽乘法DAC数据表

2021-04-14 12:53:57 11

11 AD5452W:带串行接口的12位高带宽乘法DAC数据表

2021-04-14 13:04:56 0

0 尽管SERDES(SERializer/DESerializer)拥有十分复杂的设计和验证过程,但已成为SoC中不可或缺的组成部分。成熟稳定的SERDESIP,降低了设计成本和风险,加快了产品SoC

2021-07-23 11:21:19 3986

3986 SERDES的优势 引脚数量和通道优势 SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量。对于早期的SERDES,这意味着数据可以通过同轴电缆或光纤发送。 对于现代的SERDES来说

2021-07-23 11:59:46 3794

3794 总线带宽就是总线的最大传输速度,带宽越大速度就越快。但是总线带宽的计算公式里却要除以一个8很多人都不知道为什么,接下来详细介绍一下:

2022-01-29 17:04:00 14959

14959 本文给大家提供利用axi_master接口指令端的几个静态参数的优化技巧,从扩展总线接口数量,扩展总线位宽,循环展开等角度入手。最核心的优化思想就是以资源面积换取高带宽的以便并行计算。

2022-07-01 09:39:14 1015

1015 在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口,存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据

2022-08-02 11:28:14 4854

4854

铝带宽度测量(激光三角反射传感器测宽方案)

2022-09-21 17:34:31 194

194

首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03:55 4706

4706

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2023-07-27 16:10:01 1565

1565

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO

2023-10-16 14:50:37 558

558

呢? 1. 带宽利用率:SerDes技术可以通过将多个并行数据通道转换为单个高速串行链路来提高带宽利用率。这种方式可以减

2023-11-07 10:26:07 512

512

电子发烧友App

电子发烧友App

评论