FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。HLS系列 – High LevelSynthesis(HLS) 的端口综合1

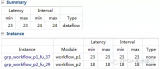

在之前HLS的基本概念1里有提及,HLS会把c的参数映射成rtl的端口实现。本章开始总结下HLS端口综合的一些知识。 1.HLS综合后的rtl端口大体可以分成2类: Clock Reset端口: 每个设计只能有一个Cloc...

2017-02-08 587

美启动大脑阿波罗计划:绘制10万神经元活动地图

30年前,美国政府启动人类基因组计划—— 一个长达13年的测序及绘制所有人类基因的研究项目。尽管项目一开始遭到了怀疑乃至反对,但是该计划却让遗传学研究领域从此焕然一新,并被认为...

2017-02-08 154

HLS系列–High Level Synthesis(HLS)的端口综合2

在上一章HLS的端口综合里有提及,HLS综合后的端口分为2中类型:BlockLevel和Port Level Interface。其中Port level是我们需要重点关注的,它又可以细分为4中类型: A. AXI4-Interface:支持Stream,Lite,Full共...

2017-02-08 493

基于DirectShow的多摄像头视频采集

1.为什么使用DirectShow 笔者使用的是两个USB摄像头,单摄像头视频采集使用OpenCV的VideoCapture类没有问题,但是双摄像头就有问题,一个正常,另外一个采集不到信息,显示一片灰色。网上有种解...

2017-02-08 3010

HLS系列 – High Level Synthesis(HLS) 的一些基本概念4

继续HLS的基本概念。 1、DataFlow的概念,以及Dataflow和Pipeline的区别 如下所示的图像处理过程,数据处理由2个滤波器构成: 默认情况下,HLS会遵循c逻辑中的先后顺序,依次调度2个函数。所以整...

2017-02-08 672

借助NOR Flash实现UltraScale FPGA后配置解决方案

作者:kenshin NOR Flash是一种非易失性存储器件,与其相似的还有NAND Flash,但是NOR Flash具有类似SRAM的并行接口,有足够的地址引脚来寻址,读数据的速度更快,因此多用于微控制器启动配置外部...

2017-02-08 982

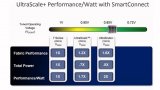

Xilinx 专家教你如何将系统级的单位功耗性能提升2

您的系统是否有不容妥协的功耗预算和热要求?大多数情况下答案是肯定的! 一般而言您无法随意提升性能,因为这样会导致功耗的不受控制。单位功耗性能是设计系统时最关键的指标之一,...

2017-02-08 228

百度采用 Xilinx FPGA 加速机器学习应用

全可编程技术和器件的全球领先企业赛灵思公司 (Xilinx, Inc. (NASDAQ:XLNX))今天宣布,全球领先的中文互联网搜索引擎提供商百度正在采用赛灵思 FPGA 加速其中国数据中心的机器学习应用。两家公司...

2017-02-08 202

MicroZed开发板笔记,第72部分:多周期约束

By Adam Taylor 在最近的几篇博客中,我们研究了基本的时序约束。那么在设计中我们现在应该能定义时钟了,并且可以创建和声明它们的关系,还应该能在时钟和系统中声明任何缺陷。作为系统设...

2017-02-08 270

如何通过SerDes获得32Gbps的板级传输速度

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 我设计PCB已经多久了,但很不好意思的说,一直都没听说过PCB可以有超过1Gbps的信号传输。我正在写的东西是关于最新的Xilinx 16nmVirtex UltraSca...

2017-02-08 416

一个DSP怪物的演化:具有大量DSP的UltraScale+ 和UItraScale全可编程器件

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 采用16nm工艺的Virtex UltraScale+全可编程器件的最多DSP数量是11904DSP48E2 slices。那是一个很大很大的数目。它已经大到足以让我好好地回顾赛灵思全...

2017-02-08 372

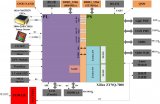

7000器件在测量类红外图像系统中的应用

备注:主图是从Fluke TiX1000宣传册中截取 作者:Hello,Panda 基于非制冷探测器的红外测量系统可在各领域广泛应用。如海关、机场等公共场所民众体温监测,芯片、焊点、激光光纤等微米级目标...

2017-02-08 175

模块间连接及输入输出端口设置

1、点击XPS的Ports选项卡,包括个模块,ExternalPorts是所有PS的对外输出管脚,也就是PS部分与外部相连的管脚;axi_interconnect_1是总线连接器模块;processing_system7_0是嵌入式处理器内核模块;my_gpio...

2017-02-08 1013

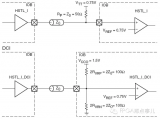

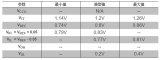

Xilinx FPGA I/O电平标准简介(三)

作者:Player FPGA那点事儿 一、GTLP(GunningTransceiver Logic Plus) GTL+电平标准即冈宁收发器逻辑电平标准加,是在Pentium Pro处理器中首先使用的一种高速总线电平标准,该标准需要差分放大输入bu...

2017-02-08 2418

浅谈Xilinx Microblaze Bootloader实现

作者:Hello,Panda 一般而言,Xilinx Microblaze会被用来在系统中做一些控制类和简单接口的辅助性工作,比如运行IIC、SPI、UART之类的低速接口驱动,对FPGA逻辑功能模块初始化配置及做些辅助计算等...

2017-02-08 1274

Xilinx FPGA I/O电平标准简介(二)

三、PCI(PeripheralComponent Interconnect) PCI电平标准即外设器件互联电平标准,该标准支持33MHz和66MHz的总线应用,包括PCI-X、PCI-33、PCI-66等各类电平标准,该标准的输入输出供电电压(VCCO)为3.3V,...

2017-02-08 2087

HLS系列– HLS中的数据类型1

数据类型优化的意义 C语言中所提供的数据类型,其长度都是8bit的整数倍(8,16,32,64bits)。但是rtl所描述的硬件,却可以支持任意长度的数据宽度。所以,在很多情况下,使用标准C所提供的数据...

2017-02-08 682

HLS系列–HighLevel Synthesis(HLS)的端口综合8

本章介绍PortLevel Interface中的最后一个IO Protocol:ap_bus 。 ap_bus可以用来和外部的总线进行互联,它不遵循任何标准的总线协议,但是它也有自己的总线接口时序,虽然并不复杂。从接口特性上,...

2017-02-08 353

HLS系列 – High Level Synthesis(HLS) 的端口综合7

在前几章里,已经分别介绍了BlockLevel Interface,Port Level Interface中的NoI/O Protocol和AXI4。本章里着重介绍下Port Level Interface的另一个子类别:MemoryInterface: Memory Interface中分为3个子类别,分别是:...

2017-02-08 826

FPGA配置– 使用JTAG是如何烧写SPI/BPI Flash的?

Xilinx的JTAG电缆可以通过FPGA“直接”烧写SPI/BPI。很多对xilinx开发环境不熟悉的用户,如果第一次接触这种烧写模式可能会有疑惑,FPGA是如何做到JTAG和Flash之间的桥接的,难道FPGA内部有专用的电...

2017-02-08 6686

深度学习:基于FPGA的解决方案更具优势

近几年来人工智能相关信息登上了各大媒体头条,自动驾驶,无人车也不再显得那么陌生,其实这一切都源于机器学习,深度学习和人工神经网络等相关学科的兴起。机器学习(Machine Learning,...

2017-02-08 265

HLS系列–实例分享,用HLS实现Goertzel算法(快速频点检测)

HLS非常适合一些信号处理模块的快速实现。下面是一个实际的例子,由于使用了HLS,非常高效的就完成了模块的rtl的实现,比用手工coding节约了大量的时间! 需求描述: 在一个项目里面,需要...

2017-02-08 645

基于vivado的fir ip核的重采样设计与实现

本文基于xilinx 的IP核设计,源于音频下采样这一需求。 创建vivado工程 1. 首先打开vivado,创建一个新的project(勾选create project subdirectory选项),并将工程命填为firfilter。 2.选择工程创建的类型为...

2017-02-08 3880

双通道方法让Zynq SoC资源利用最大化

By Adam P. Taylor 本篇的摘录和改编来自于Xcell杂志的最近一期 许多裸机应用和简单的操作系统只使用ZYNQ SoC PS( processing system)中的两个ARM内核中的一个,一种设计上的选择会潜在地限制了系统的性...

2017-02-08 256

Adam Taylor玩转MicroZed系列,第75部分:放置约束

By Adam Taylor 在先前的博客中我们研究过I/O约束,下一个合乎逻辑的步骤就是研究如何在我们的设计中用FPGA进行放置和布线约束。使用放置约束的原因如下:为了帮助实现时序,或者为了在设计...

2017-02-08 257

Adam Taylor玩转MicroZed系列74:物理约束

研究了相关的时序约束后,在设计中我们也不能忽视所能运用到的物理约束。一个工程师最常用的物理约束是I/O管脚的放置和与每个I/O脚相关的参数定义(标准、驱动能力等)。然而,还有其它...

2017-02-08 223

采用高速串行端口的I/O bit传输比FPGA仿真有更广的适用性

作者:Steve Leibson, 赛灵思战略营销与业务规划总监 Luis Bielich所撰写的名为Zero Latency Multiplexing I/O for ASIC Emulation的Xilinx应用手册XAPP1217介绍了一种技术。这种技术使用一个高速的串行接口,将许多...

2017-02-08 201

如何把PetaLinux移植到Xilinx FPGA上

作者:作者:Sweta(印度班加罗尔PES理工学院),Srikanth Chintala(印度班加罗尔远程信息处理开发中心),以及ManikandanĴ教授(印度班加罗尔PES大学) (赛灵思中国通讯杂志的最新一期(55期)...

2017-02-08 335

Adam Taylor玩转MicroZed系列73:用其他的Zynq

By Adam Taylor 在过去一周中,我接到了很多不同人的来信,他们正在使用以Zynq为基础的开发工具。他们非常想知道怎么样去把MicroZed系列博客教程应用到他们所选择的硬件平台上。加上Avnet Micro...

2017-02-08 443

关于XDC约束文件,你需要知道的几点

作者: 圆宵 FPGA那点事儿 在ISE时代,使用的是UCF约束文件。从Vivado开始,XDC成了唯一支持的约束标准。XDC除了遵循工业界的通行标准SDC(Synopsys Design Constraints)之外,还加入了XILINX FPGA特有的...

2017-02-08 4677

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |