完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

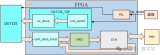

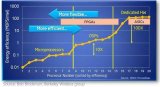

各行各业纷纷采用FPGA芯片是源于FPGA融合了ASIC和基于处理器的系统的最大优势。 FPGA能够提供硬件定时的速度和稳定性,且无需类似自定制ASIC设计的巨额前期费用的大规模投入。...

ASK即“幅移键控”又称为“振幅键控”,也有称为“开关键控”(通断键控)的,所以又记作OOK信号。ASK是一种相对简单的调制方式。...

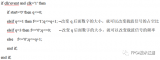

TLC549是一个8位的串行模数转换器,A/D转换时间最大为17us,最大转换速率为4MHz。下图为TLC549的访问时序,从图中可以看出,TLC549的使用只需对外接输入输出时钟(I/O CLK)和芯片选择(/CS)、输入的模拟信号(ANALOG IN)的控制。...

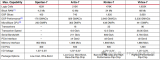

Xilinx7系列FPGA由四个FPGA系列组成,可满足一系列系统需求,从低成本、小尺寸、成本敏感的大容量应用到最苛刻的高性能应用的超高端连接带宽、逻辑容量和信号处理能力。...

Xilinx建议使用非阻焊定义的(NSMD)铜材BGA焊盘,以实现最佳板设计。NSMD焊盘是不被任何焊料掩模覆盖的焊盘,而阻焊定义的(SMD)焊盘中有少量阻焊层盖住焊盘平台。...

这款flash芯片的的存储是一个扇区4KB,一个扇区可以存256个字,一个字是8位,一个块是64KB,一共有256个块组成一个存储flash内存。...

上位机才能够在接收数据后正确显示图像。所以每帧图像的开始需要多传输8字节数据,一般规定每次传输一行数据,由于OV7725一行有640个像素,每个像素16位,而以太网每个时钟传输8位数据,因此需要1280个时钟才能传输完一次数据。...

AXI总线由一些核心组成,包括AXI主处理器接口(AXI4)、AXI处理器到协处理器接口(AXI4-Lite)、AXI主外设接口(AXI4)、AXI外设到主处理器接口(AXI4-Lite)等。...

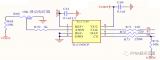

以核心处理板为核心,由信号源产生的待处理模拟信号通过同轴线缆连接到核心处理板的信号接口,同时,连接同步时钟等其他相关信号到核心处理板。...

一般都是先创建MIF文件,将图像中的像素信息用一个ROM储存起来,然后调用ROM里面的地址进行处理,相当于制作了一个ROM查找表。...

了解FPGA器件何时适合实现所需的系统功能是理解FPGA技术的关键要素。设计团队明白FPGA技术并不适用于每一个设计或应用程序。...

我们都知道RAM是根据地址查找对应的数据,而对于CAM,则恰好相反,是已知数据查找其对应的地址。像在网络报文处理里,根据报文的五元组的一些信息去查询其所属的规则地址,随后通过该地址去查询对应的RAM获取对应的Action信息。...

FPGA 被封装在更大的封装中,从而提供了更多的 I/O。"然而,I/O 的增加并不像逻辑资源那样引人注目。...

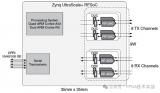

数据转换功能的集成为5G基站中的远程无线单元(RRU)提供了巨大的节能效果。对于每个JESD204通道,节省的成本大约为1W,或者对于来自天线阵列的每个数据流来说,节省的成本是不同的。...

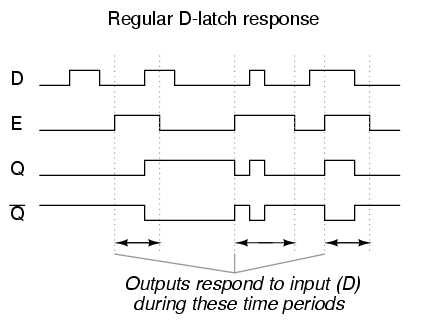

锁存器、触发器和寄存器它们的英文分别为:Latch、Flip-Flop、Register。我们对这三个单词的翻译真的是非常直观,从名字就能大概猜出它们的含义。...

科通技术了解到AnDAPT电源解决方案的目标市场是电源轨数量较多的市场,因此需要电源管理功能,并通过AnDAPT产品线帮助AMD产品线的客户简化电源设计。...

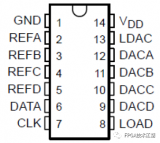

本设计采用串行数/模转换芯片TLC5620,TLC5620是一个拥有四路输出的数/模转换器,时钟频率最大可达到1MHz。...

FPGA 正是一种硬件可重构的体系结构。它的英文全称是Field Programmable Gate Array,中文名是现场可编程门阵列。 FPGA常年来被用作专用芯片(ASIC)的小批量替代品,然而近年来在微软、百度等公司的数据中心大规模部署,以同时提供强大的计算能力和足够的灵活性。...

首先是FPGA硬件的变化太多,各个模块可配参数的变化(比如卷积模块并行数的变化),另外一个是网络模型多种多样以及开源的网络模型平台也很多(tensorflow,pytorch等)。网络压缩也有很多种算法,这些算法基本上都会导致网络模型精度的降低。...

DNN中应用最广泛的是CNN和RNN,CNN是一种卷积网络,在图片识别分类中用的较多,RNN可以处理时间序列的信息,比如视频识别和语音识别。...