赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19707

19707

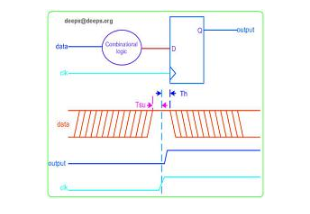

时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错。

2020-06-26 10:37:00 4550

4550

7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

2022-09-30 08:49:26 1326

1326 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

“全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

时钟周期约束是用于对时钟周期的约束,属于时序约束中最重要的约束之一。

2023-08-14 18:25:51 472

472 通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

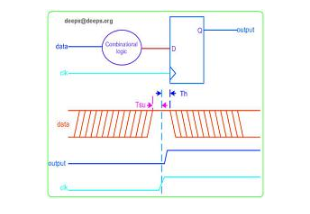

组合逻辑产生的时钟可能有毛刺,会被错误地当成有效时钟边沿,在设计中会导致功能错误。因此,不要使用组合逻辑的输出作为时钟。

2024-01-22 09:30:50 168

168

FPGA 时钟分配网络设计技术

2012-08-20 17:15:27

FPGA时钟时序资料

2014-06-03 20:13:27

(08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2022-02-23 07:26:05

(12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:08:36

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束

2017-05-25 15:06:47

;count:=0;else count:=count+1;end if; end if;end process; --------------时钟正常运行 以及时间的调整的控制开关

2012-06-01 22:02:40

想问下各位大佬,FPGA外部接上晶振后,到底是怎么生成时钟的,又是怎么使用这个时钟的?如果没有外部晶振,内部可以自发的产生时钟吗?

2019-03-27 11:45:32

FPGA时钟和复位电路设计本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt FPGA的时钟输入都有专用引脚

2015-04-24 08:17:00

你好我有一个关于时钟断言的问题基本上我的实验是JESD204B测试(KC 705带DAC37J82板)这是基本设置FPGA clk(IP内核时钟来自另一个DAC板通过FMC连接器)系统工作正常1.

2019-04-10 12:35:21

喜我对时钟门控有一些疑问。从我所读到/学到的东西 - 时钟门控可用于低功率fpga设计(关闭时钟以防止元件切换以节省功率)。但是,我还读到时钟门控很糟糕,因为它可能会引起系统故障。我想我已经看到了

2019-02-21 10:21:41

FPGA时钟问题 2010-06-11 15:55:39分类: 嵌入式1.FPGA的全局时钟是什么?FPGA的全局时钟应该是从晶振分出来的,最原始的频率。其他需要的各种频率都是在这个基础上利用PLL或者其他分频手段得到的。

2021-07-29 09:25:57

一般我们用的FPGA的时钟都是用晶振来提供的,我想请教一下大家,可以用锁相环芯片AD9518(或者其它锁相环)来生成时钟供给FPGA,作为FPGA的系统时钟

2013-08-17 11:20:41

本人菜鸟,写了一个fpga的时钟,但是不知道为什么秒上从0变为1 又变为0.。。。分跟时就根本没变化。。。不知道为什么啊。。。求指教//分频子模块module fenpin (clk,rst_n

2012-10-25 16:06:12

很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。1.全局时钟对于一个设计项目

2012-12-14 16:02:37

模块,充分理顺模块间的相互关系对于FPGA设计来说非常重要。以闹钟设计为例,我们通过建立四个清晰直观的模块(数码管显示模块,矩阵键盘扫描模块,时钟计数模块,闹钟设定模块),以及建立完善的信号列表和运用

2017-08-02 18:00:01

要区分,MRCC SRSS,要知道Clock Regin的概念,MRCC 进来CLK,Regin里外皆可到,SRCC 进来CLK,只能在Regina里面

2019-05-22 07:24:24

200MHz、125MHz与之类似。我想问的是能不能有方法通过1个晶振给所有该频率的FPGA管脚提供时钟。第一次见发帖,求大神解答

2015-10-09 21:35:56

视频信号(包括数据与时钟,其中数据位宽16位,时钟1位,最高工作频率148.5MHZ).2.遇到的问题时钟相对于数据的延时,也就是信号的建立与保持时间在经过FPGA后出现偏移。造成后端的DA不能正确的采集到数据。

2014-02-10 16:08:02

时钟问题:⑴ 利用与门、D 触发器等器件,分别画出如下两段代码的框图。⑵ 指出在 FPGA 中采用哪种处理方式比较合理,为什么?代码 1: 代码 2:第二种方案比较合理,第一种方案增加了时钟的时延,容易不稳定

2012-03-12 14:43:37

`带你深入全面了解FPGA硬件资源PLL`

2021-03-30 14:43:12

我在我的同学面前炫耀FPGA是做高速处理的,可是,当人家问我,我的时钟频率能达到多少时,我说利用PLL能拉到200MHz,他说,这么低啊?我的手机频率都是1.5G的呢。我无语。。。后来才了解到,他

2012-03-08 17:11:08

使用FPGA时钟展频技术搞定RE测试特权同学原创,转载请注明出处1 关于时钟展频应用展频技术是通过对尖峰时钟进行调制处理,使其从一个窄带时钟变成为一个具有边带谐波的频谱,从而达到将尖峰能量分散到展频

2016-10-11 17:32:44

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

2020-04-25 07:00:00

嗨,我想知道Virtex-6 FPGA可以预期多少时钟抖动。我已经阅读了有关Virtex-6 FPGA的所有文档,但没有找到数值。我发现的唯一的事情是它具有低抖动但不低或数值。

2020-06-12 14:56:20

//基本D触发器moduleD_EF(Q,D,CLK)input D,CLK;output Q;regQ;//在always语句中被赋值的信号要声明为reg类型 寄存器定义always @ (posedgeCLK) //上升沿,下降沿用negedge表示,^_^ 需要记忆begin Q

2016-01-22 14:09:25

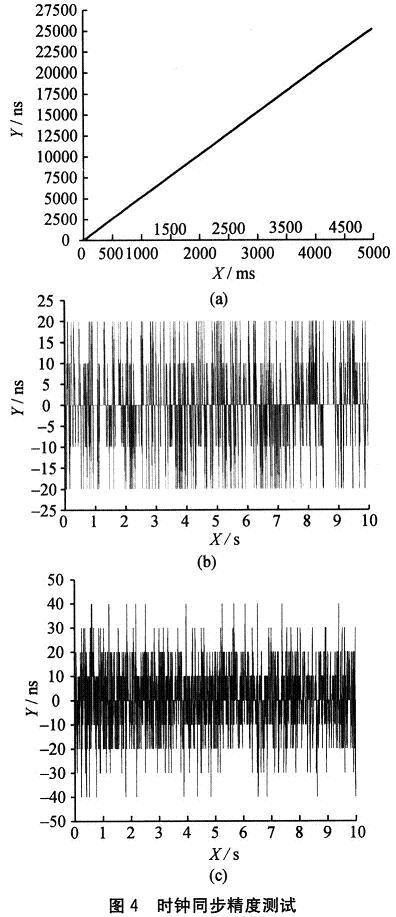

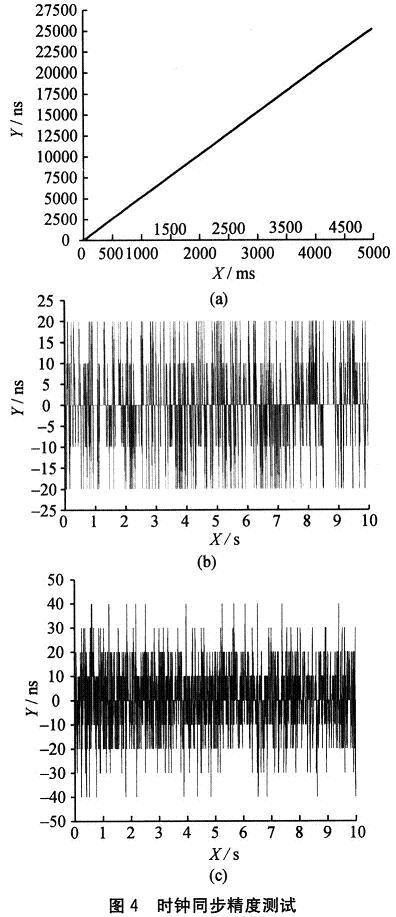

摘要:随着石油勘探的发展,在地震勘探仪器中越来越需要高精度的同步技术来支持高效采集。基于这种目的,采用FPGA技术设计了一种时钟恢复以及系统同步方案,并完成了系统的固件和嵌入式软件设计。通过室內测试

2019-06-18 08:15:35

基于FPGA的时钟设计

2012-08-17 23:58:55

同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

2019-10-16 07:11:33

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

怎样将FPGA时钟引脚作为普通输入引脚设置,在软件中怎样设置?求解答{:2:}

2013-05-21 20:11:34

提高FPGA的时钟精度的方案有哪些,哪位大神告诉一下

2015-10-13 08:22:31

有一篇文章说fpga的时钟周期一般采用整偶数,这个有什么...

2014-03-16 19:34:02

我做的一个基于DSP的系统中,DSP做主处理器,控制着整个系统,包括信号处理,整体调度等;选择了一块Xilinx的FPGA做FIFO UART和系统的逻辑控制和译码。DSP的时钟输入为15MHz

2023-06-19 06:43:17

计算FPGA外部引脚的频率。我需要将其与内部FPGA时钟同步吗?内部参考时钟以60Mhz运行,外部频率在10khz到15khz之间变化,不同步的外部频率是否会导致错误或问题?以上来自于谷歌翻译以下

2019-06-18 09:37:29

一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟电路是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 提出了一种基于FPGA的时钟跟踪环路的设计方案,该方案简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方案能够使接收机时钟快速准确地跟踪发

2010-11-19 14:46:54 31

31 FPGA的时钟频率同步设计

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速

2010-01-04 09:54:32 2762

2762

本文将探讨FPGA时钟分配控制方面的挑战,协助开发团队改变他们的设计方法,并针对正在考虑如何通过缩小其时钟分配网络的规模来拥有更多的FPGA I/O,或提高时钟网络性能的设计者们

2011-03-30 17:16:32 938

938

用大多数FPGA都可以实现一个数字UWB(超宽带)脉冲发生器。本设计可以创建一个两倍于FPGA时钟频率的脉冲信号(

2011-09-06 11:59:48 5280

5280

DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 一种基于FPGA的时钟相移时间数字转换器_王巍

2017-01-07 22:23:13 2

2 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义

2017-02-08 05:31:40 2048

2048

谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

时钟设施提供了一系列的低电容、低抖动的互联线,这些互联线非常适合于传输高频信号、最大量减小时钟抖动。这些连线资源可以和DCM、PLL等实现连接。 每一种Spartan-6芯片提供16个高速、低抖动的全局时钟资源用于优化性能。

2018-07-14 07:07:00 6504

6504

提出了一种基于FPGA的时钟跟踪环路的设计方粢,该方粢简化了时钟跟踪环路的结构,降低了时钟调整电路的复杂度。实际电路测试结果表明,该方集能够使接收机时钟快速准确地跟踪发射机时钟的变化,且时钟抖动小、稳准度高、工作稳定可靠。

2017-11-30 15:10:20 5

5 近期,一直在调试使用 Verilog 编写的以太网发送摄像头数据到电脑的工程(以下简称 以太网图传)。该工程基于今年设计的一款 FPGA 教学板 AC620。AC620 上有一个百兆以太网 接口

2018-02-06 14:39:47 9

9 如果输入信号需要反相,则要尽可能的调用输入带反相功能的符号,而不是使用分离的反相器来进行反相

2018-12-22 15:05:16 2225

2225 本文档的主要内容详细介绍的是spartan-6 FPGA的时钟资源的用户指南资料免费下载。

2019-02-15 16:39:07 27

27 状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

2019-12-04 07:03:00 2880

2880

。 不要随意将内部信号作为时钟,如门控时钟和分频时钟,而要使用CLKDLL或者DCM产生的时钟,或者可以通过建立时钟使能或者DCM产生不同的时钟信号。 FPGA尽量采取同步设计,也就是所有时钟都是同一个源头,如果使用两个没有相位关系的异步时钟,必须

2020-12-11 10:26:44 1482

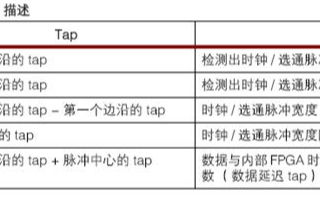

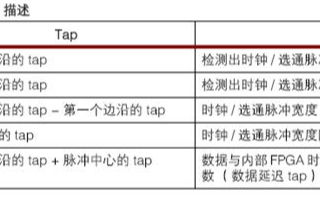

1482 ,并与内部 FPGA 时钟实现中心对齐。在这个方案中,内部 FPGA时钟采集传出的数据。存储器传出的时钟/ 选通脉冲用于决定与数据位相关的延迟值。因此,与选通脉冲相关的数据位的数量不受限制。由于无需将选通脉冲分配给相关数据位,所以不需要其他时钟资源。

2020-11-26 10:01:31 1219

1219

区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 本文档的主要内容详细介绍的是FPGA硬件基础之理解FPGA时钟资源的工程文件免费下载。

2020-12-10 14:20:11 6

6 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 传统的异步采集方法会影响采集到的功耗信息的信噪比,降低功耗分析的成功率。针对异步采集的问题提出一种新的时钟同步功耗信息采集方法。该采集方法基于现场可编程门阵列(FPGA)的时钟同步采集平台

2021-03-31 15:50:21 6

6 在设计FPGA项目的时候,对时钟进行约束,但是因为算法或者硬件的原因,都使得时钟约束出现超差现象,接下来主要就是解决时钟超差问题,主要方法有以下几点。 第一:换一个速度更快点的芯片,altera公司

2021-10-11 14:52:00 2878

2878

(08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA时钟设计原则1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟设计原则5)结语1.2 FPGA简介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1481

1481 设计变更极短交付周期减少库存管理费用缓解短缺风险5、SiT9120应用1Gb到10Gb以太网光学模块PCIeFPGASATA/SAS光纤通道系统计时无线和回程光纤、电缆、DSLCPE和家庭网关安全设备

2022-06-13 16:29:34 2950

2950 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 电子发烧友网站提供《Logos系列FPGA时钟资源(Clock)用户指南.pdf》资料免费下载

2022-09-26 10:15:21 1

1 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 686

686

随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码可能无法满足时序要求。

2023-05-06 09:33:27 774

774

2023-11-01 09:05:26 0

0 就是看看超差的那个线路,增加一些中间寄存器,或者使用流水线技术,就是将组合逻辑和时序逻辑分开,大的时序逻辑,尽量优化成由很多小的时序逻辑组成一个大的时序逻辑。

2024-02-29 12:47:03 114

114

电子发烧友App

电子发烧友App

评论