近期,eSilicon推出了由台积电7nm工艺制造的NeuASIC ASIC设计平台,包含用于网络应用的软硬件宏命令和用于构建AI加速器的新架构及IP库。

NeuASIC平台为设计者提供了多种功率优化的内存编译器、SerDes和2.5D IC封装。7nm库包括56Gbps SerDes、HBM2 PHY、三态内容寻址存储器(TCAM)编译器、网络优化I/O以及其他组件。

2017年,Marvell关闭了其大部分欧洲的业务,eSilicon由此“获得”了Marvell的意大利工程师团队,该团队为Marvell开发了28nm工艺制造的56Gbps SerDes。这个团队用基于ADC/DSP的相同架构开发出了7nm的56Gbps SerDes,且该核出现在了NeuASIC平台上,同时,该核可以被单独授权使用。对于芯片而言,功耗与性能似乎是两个无法同时兼顾的指标。

2

三星:2020年开发3纳米制程,芯片设计费将高达15亿

三星电子先前发布,到2020年开发3纳米Foundry制程。据分析称3纳米Foundry制程芯片设计费用将高达15亿美金。虽芯片设计费用的增长倍数极高,但据专家分析称其电流效率和性能提升幅度并没有与费用成正比,而且考虑到高额的费用,能设计3纳米工程的企业屈指可数。

半导体市调机构International Business Strategy(IBS)分析称3纳米芯片工程的芯片设计费用将高达4亿至15亿美金。IBS说明,在设计复杂度相对较高的GPU等芯片设计费用最高。该公司资料显示28纳米芯片的平均设计费用为5130万美金,而采用FinFET技术的7纳米芯片设计费用为2亿9780万美金,是将近6倍的涨幅。

3

3D感测2023年产值扩张至185亿美元

随着2017年9月iPhone X的推出,Apple为消费者使用3D感测技术带动新趋势。相关市调机构研究指出,全球3D影像与感测市场预计将从2017年的21亿美元扩大到2023年的185亿美元,年复合成长率达44%。包括全局快门影像传感器、VCSEL、射出成型和玻璃光学、绕射光学组件(DOE)和半导体封装供货商都可望受益。

目前有碍于供应链部分关键组件还掌握在特定厂商手上,一旦Android智能手机的替代供应链到位,搭载率将加速并从2018年的13.5%增加到2023年的55%。此外,3D感测也开始延伸到其他消费设备和汽车领域应用,高阶市场如医疗、工业和科学也将加速采用。

4

AI公司旷视科技拟融资6亿美元阿里巴巴参投

知情人士称,中国面部识别系统Face++开发商旷视科技拟至少融资6亿美元,投资者包含阿里巴巴集团、博裕资本。

据称,旷视科技将在数周内完成这轮融资,随后将寻求启动第二期(second tranche)融资。旷视科技投资者已包括马云旗下蚂蚁金服、中国最大的政府背景风投基金之一。

阿里正在加大对中国最大人工智能(AI)创业公司的投资,希望在其不断扩大的互联网和零售帝国部署AI技术。旷视科技向联想集团、蚂蚁金服等公司提供面部识别系统,它与阿里支持的另外一家创业公司商汤科技在零售、金融、智能机以及公共安全等领域争夺市场份额。

5

多镜头成趋势,华为新款Mate拉动CIS产业需求

尽管2018下半年智能手机市场充斥不确定性,不过大陆一线手机厂华为缴出上半年出货突破1亿支佳绩,全年将挑战2亿支大关。熟悉CMOS影像传感器业者表示,华为除了出货成长雄心旺盛外,三镜头手机P20获得市场好评,据了解,预计第3季推出的新款Mate机种仍将延续三镜头设计趋势。

多镜头设计将推动对于CIS元件需求,其中,代理Sony CIS元件、又重返华为供应链的代理通路业者尚立可望大为受惠,市场估计尚立第3季业绩可望较第2季成长双位数百分比,今年则将有逐季业绩成长表现。

-

芯片

+关注

关注

462文章

53581浏览量

459489 -

asic

+关注

关注

34文章

1271浏览量

124069 -

AI

+关注

关注

90文章

38224浏览量

297070

原文标题:一周产业新闻(7.20—7.26)

文章出处:【微信号:ic_park,微信公众号:中关村集成电路设计园】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

“汽车智能化” 和 “家电高端化”

国产AI芯片真能扛住“算力内卷”?海思昇腾的这波操作藏了多少细节?

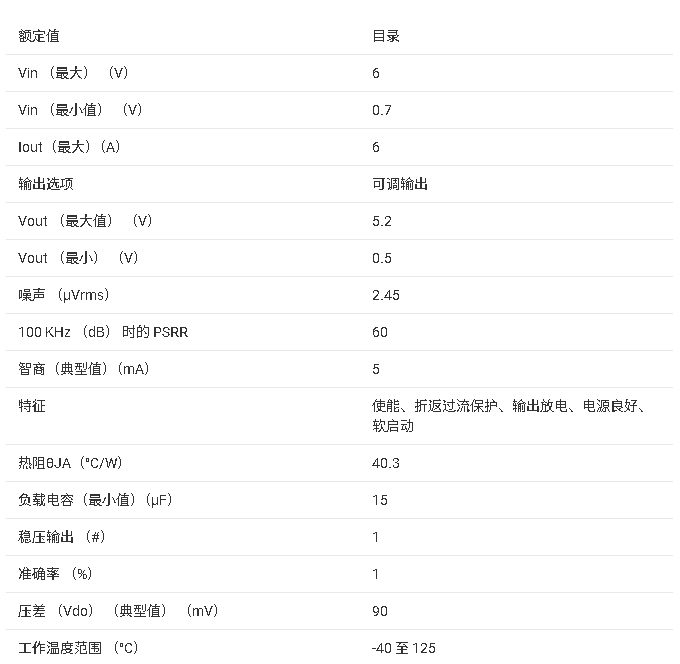

TPS7A56 6A低压差线性稳压器(LDO)技术文档总结

AMD 7nm Versal系列器件NoC的使用及注意事项

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片的需求和挑战

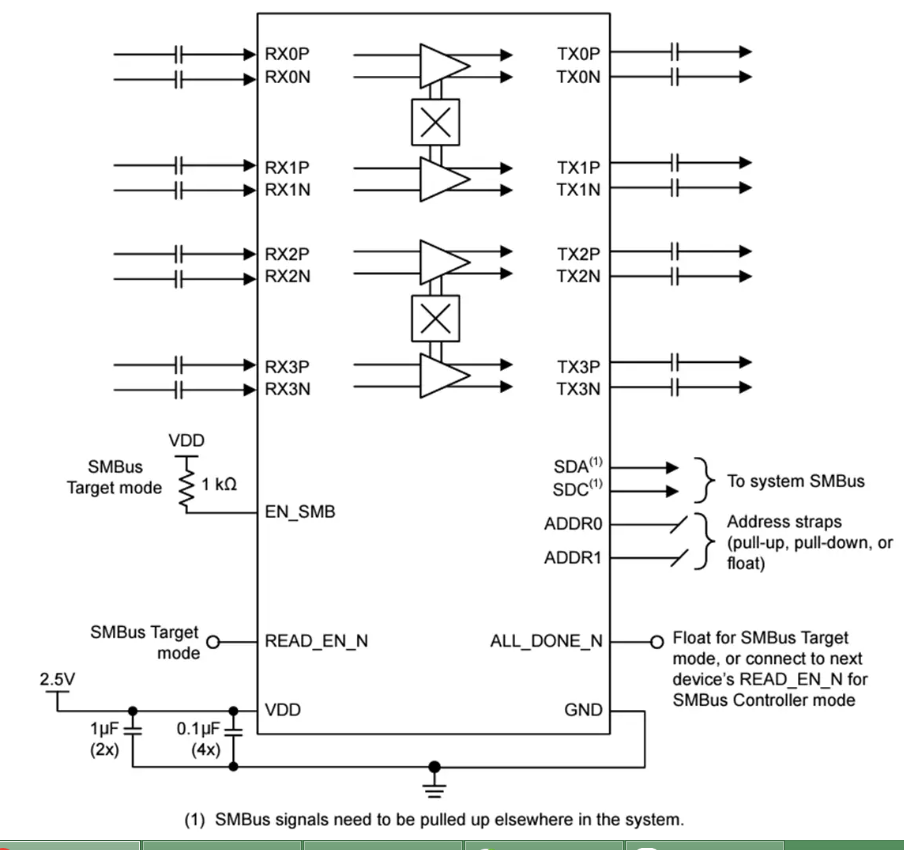

DS560DF810 56Gbps八通道重定时器技术深度解析

AI 芯片浪潮下,职场晋升新契机?

从Ascend 910D看芯粒创新,半导体行业将迎重大变局

AI芯片,需要ASIC

从14nm到3nm:AI ASIC算力、能效双突破

从SerDes到SoC,全场景适配的FCom差分晶振设计全解

什么是SerDes?SerDes有哪些应用?

7nm 56Gbps SerDes加持,这款ASIC或为AI芯片封装提供新思路

7nm 56Gbps SerDes加持,这款ASIC或为AI芯片封装提供新思路

评论