SR锁存器的功能有哪些?

SR锁存器是一种数字电路中常用的存储元件,它具有一些重要的功能和特点。以下是对SR锁存器功能的介绍: 存储功能 SR锁存器最基本的功能是存储信息。它有两个稳定状态,分别对应于“1”和“0”。当输入

2024-08-28 10:55:56

锁存器的组成、功能及应用

锁存器(Latch)是一种具有记忆功能的数字电路元件,用于存储和保持数字信号的状态。锁存器在数字电路设计中扮演着重要的角色,广泛应用于各种电子设备和系统中。本文将介绍锁存器的组成、功能及应用。 一

2024-07-23 11:32:56

d锁存器解决了sr锁存器的什么问题

存在一些差异,D锁存器在一定程度上解决了SR锁存器的一些问题。 引言 在数字电路设计中,锁存器是一种基本的存储元件,用于存储一位二进制信息。锁存器的种类有很多,其中D锁存器和SR锁存器是最常见的两种。这两种锁存器在功能和应用上有一定的差异,D锁存器在某些方

2024-08-28 09:16:42

常用的d锁存器型号有哪些

、输出使能和复位功能。 74HC74:这是一种高速CMOS D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入、输出使能和复位功能。 74F74:这是一种高速的正触发D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

2024-08-28 09:13:51

rs锁存器和sr锁存器有什么区别吗

RS锁存器和SR锁存器是数字电路中两种常见的存储单元,它们在功能和应用上有一些区别。 RS锁存器 RS锁存器,即Reset-Set锁存器,是一种具有两个稳定状态的存储单元。它有两个输入端,分别

2024-07-23 14:15:52

sr锁存器和触发器的逻辑功能区别

在数字电路中,锁存器和触发器是两种非常重要的存储元件,它们在逻辑功能上有着明显的区别。锁存器和触发器都是用于存储二进制信息的基本元件,但它们在结构、工作原理、应用场景等方面都存在差异。 一、锁存器

2024-07-23 10:19:20

FPGA的设计中为什么避免使用锁存器

前言 在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数

2020-11-16 11:42:00

锁存器电路中的中间是什么元件

锁存器电路概述 定义与功能 锁存器(Latch)是数字电路中的一种基本存储元件,用于存储一个位(1或0)的状态。它能够在特定输入脉冲电平作用下改变状态,并保持该状态直到下一个脉冲电平到来。锁存器

2024-07-23 11:29:39

锁存器电路通过什么触发的

锁存器(Latch)是一种在数字电路中广泛使用的存储元件,它能够存储一位二进制信息。锁存器电路的触发方式有很多种,包括同步触发、边沿触发、电平触发等。 一、锁存器的基本概念 锁存器是一种具有记忆功能

2024-07-23 11:31:06

锁存器的工作原理

锁存器的工作原理 锁存器(latch)是一种用于存储和记忆数字信号的电路。它被广泛用于计算机和数字电子电路中,用于实现内存存储、寄存器和其他计算单元。 锁存器的工作原理是通过反馈电路和放大

2023-12-08 11:18:03

运动控制器位置锁存功能的应用

今天,正运动小助手给大家分享一下运动控制器位置锁存功能的应用,以ZMC408CE运动控制器为例,介绍多种锁存模式的用法,用户可根据自身需求灵活选择。

2022-11-07 10:57:16

锁存器的作用是什么?

数码管的动态显示截取了部分程序,使用了74hc573锁存器,但是我觉得去掉锁存器程序照样可以执行,那么这里使用锁存器的意义是什么呢?还是说只是用一下没有什么特殊的含义? for( i=0

![]() cd340823

2023-10-26 07:18:07

cd340823

2023-10-26 07:18:07

【答疑】关于锁存器问题的讨论

逻辑才需要。问2:是不是只要组合逻辑的if else补充了,就不会生成锁存器了?答:不一定。这里的关键在于“保持不变”,千万不要从“代码层次”来理解,而应该从“功能的层次”来理解,要找准到底有没有“保持

![]() 明德扬吴老师

2020-03-02 00:25:31

明德扬吴老师

2020-03-02 00:25:31

如何制作一个软锁存电路

在这个项目中,我们将制作一个软锁存电路,通过按一个按钮来打开和关闭电子设备。该电路称为软锁存开关。软锁存电路与普通锁存电路不同,在软锁存器中,可以使用外部手段(按钮)改变开启和关闭状态,但在普通锁存

2022-08-25 16:32:47

什么是锁存器 与寄存器有何区别

锁存器(Latch)是一种基本的数字电路元件,用于存储二进制数字的状态信息,并能够在需要时通过加电或控制信号的作用保持状态。它通常由几个逻辑门组成,可以实现简单的存储、移位、计数等功能。锁存器在数

2023-04-09 18:45:34

锁存器工作时是什么触发方式

锁存器(Latch)是一种存储电路,用于存储一位二进制信息。锁存器在数字电路设计中非常常见,它可以用来保持数据状态、实现同步等功能。锁存器的工作原理和触发方式是数字电路设计的基础之一。 1. 锁存器

2024-07-23 10:17:50

锁存器的相关资料分享

前言在学习了基本锁存器原理后,剩下就是对各个外设以及对单片机寄存器的相关学习,如果没有看过之前对锁存器原理的讲解的同学,可以回看一下。蓝桥杯基础教程之锁存器操作(非常重要!)学习蓝桥杯必看

![]() 人走了

2021-12-03 08:05:27

人走了

2021-12-03 08:05:27

锁存器的相关资料下载

P0口作为分时复用接口,既要作为数据总线口,又要作为地址总线口 输出的低8位地址需要用8位锁存器锁存 ALE的下降沿将P0口输出的低8位地址锁存• 对于锁存器:○ /OE为输出使能端 § /OE有效

![]() lancy

2021-12-13 08:23:27

lancy

2021-12-13 08:23:27

锁存器原态和新态的定义

锁存器(Latch)是一种存储单元,用于存储一位二进制信息。在数字电路中,锁存器是一种基本的存储元件,广泛应用于寄存器、计数器、触发器等电路中。锁存器的原态和新态是描述锁存器状态变化的两个重要概念

2024-07-23 10:21:06

锁存器的基本输出时序

在深入探讨锁存器的输出时序时,我们需要详细分析锁存器在不同控制信号下的行为表现,特别是控制信号(如使能信号E)的电平变化如何影响数据输入(D)到输出(Q)的传输过程。以下是对锁存器输出时序的详细描述,旨在全面覆盖其工作原理和时序特性。

2024-08-30 10:43:44

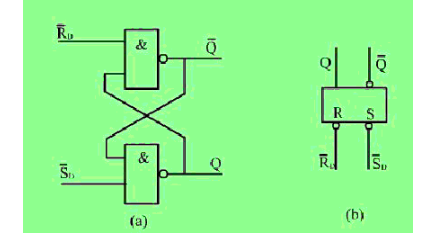

RS锁存器和D锁存器的电路结构及工作原理

一、SR锁存器 1、RS锁存器的电路结构及工作原理 RS锁存器是一两输入、两输出的电路,其电路如图1(a),其有两个互相交叉反馈相连的两个与非门构成,其两个输出为两个相反的输出(或称为互补输出),图

2020-10-07 15:24:00

Rs锁存器的R,S为什么端

RS锁存器的R和S端分别代表 Reset(复位) 和 Set(置位) 端。 R(Reset)端 功能 :当R端接收到有效信号(通常是低电平,但具体取决于锁存器的实现方式,有时高电平也可能为有效信号

2024-08-28 10:25:27

锁存器的结构组成及工作原理

锁存器(latch)是数字电路中的一种基本存储单元,用于存储和保持一个或多个位的状态。锁存器在数字逻辑设计中扮演着重要的角色,它们可以用于实现各种功能,如数据存储、信号同步、状态保持等。 锁存器

2024-08-28 09:09:00

D锁存器的基本实现

在Verilog HDL中实现锁存器(Latch)通常涉及对硬件描述语言的基本理解,特别是关于信号如何根据控制信号的变化而保持或更新其值。锁存器与触发器(Flip-Flop)的主要区别在于,锁存器

2024-08-30 10:45:03

简述锁存器的工作时序

锁存器(Latch)是数字电路中的一种重要组件,其工作时序对于理解其功能和在电路中的应用至关重要。锁存器的工作原理主要基于电平敏感的特性,它能够在特定输入脉冲电平作用下改变状态,将信号暂存以维持某种电平状态。

2024-08-30 10:42:58

锁存器的主要特性、种类及应用

锁存器是具有两个稳定状态的时序逻辑电路,即它是双稳态多谐振荡器。锁存器有一个反馈路径来保留信息。因此,锁存器可以是存储设备。只要设备处于开机状态,锁存器就可以存储一位信息。当使能启用时,锁存器会在输入更改时立即更改存储的信息,即它们是电平触发设备。当使能信号打开时,它会持续对输入进行采样。

2022-09-12 16:13:00

锁存器是时序逻辑电路吗

在数字电子学中,锁存器(Latch)和触发器(Flip-Flop)是两种基本的存储元件,它们在数字系统中扮演着至关重要的角色。它们的主要功能是存储和保持数据状态,以供后续处理。然而,它们在实现方式

2024-07-23 10:16:31