好的,这是 74LS112 双 JK 负边沿触发触发器(带置位和清零) 的引脚图描述和功能说明:

芯片概述

- 型号: 74LS112

- 类型: 双 JK 主从触发器 (Dual JK Master-Slave Flip-Flop)

- 封装: 常见为 16引脚 DIP(双列直插)封装。

- 触发方式: 负边沿触发 (在时钟脉冲 CP 的 下降沿 改变状态)。

- 特点: 每个触发器都有独立的 异步置位 (PRESET, PR) 和 异步清零 (CLEAR, CLR) 输入(低电平有效),以及 数据 (J 和 K) 输入。输出为标准的 Q 和 Q非 (互补输出)。

引脚图 (16-Pin DIP 封装)

假设芯片缺口在上方或左侧有标识点,引脚编号从左下角(标识点旁)开始逆时针排列:

+-----+--+-----+

1CLR |1 +--+ 16| Vcc (+5V)

1K |2 15| 2CLR

1J |3 14| 2K

1CP |4 13| 2J

1PR |5 74LS112 12| 2CP

1Q |6 11| 2PR

1Q非 |7 10| 2Q

GND |8 9| 2Q非

+--------------+引脚功能列表:

| 引脚号 | 引脚名称 | 类型 | 功能描述 |

|---|---|---|---|

| 1 | 1CLR | 输入 | 触发器1 异步清零 (CLEAR)。低电平有效。当为低电平时,强制 Q 输出为低 (0),Q非 为高 (1),独立于时钟 (CP) 状态。 |

| 2 | 1K | 输入 | 触发器1 数据输入 K。高或低电平有效。与 J 一起,在时钟下降沿时决定触发器的次态 (Qn+1)。 |

| 3 | 1J | 输入 | 触发器1 数据输入 J。高或低电平有效。与 K 一起,在时钟下降沿时决定触发器的次态 (Qn+1)。 |

| 4 | 1CP | 输入 | 触发器1 时钟输入 (CLOCK PULSE)。负边沿触发。状态变化发生在该引脚信号的 下降沿 (高电平 -> 低电平)。 |

| 5 | 1PR | 输入 | 触发器1 异步置位 (PRESET)。低电平有效。当为低电平时,强制 Q 输出为高 (1),Q非 为低 (0),独立于时钟 (CP) 状态。 |

| 6 | 1Q | 输出 | 触发器1 标准输出 Q。 |

| 7 | 1Q非 (1/Q) | 输出 | 触发器1 反相输出 Q非。Q 的互补输出。 |

| 8 | GND | 电源 | 接地 (0V)。 |

| 9 | 2Q非 (2/Q) | 输出 | 触发器2 反相输出 Q非。 |

| 10 | 2Q | 输出 | 触发器2 标准输出 Q。 |

| 11 | 2PR | 输入 | 触发器2 异步置位 (PRESET)。低电平有效。功能同 1PR (引脚5),作用于第二个触发器。 |

| 12 | 2CP | 输入 | 触发器2 时钟输入 (CLOCK PULSE)。负边沿触发。功能同 1CP (引脚4),作用于第二个触发器。 |

| 13 | 2J | 输入 | 触发器2 数据输入 J。功能同 1J (引脚3),作用于第二个触发器。 |

| 14 | 2K | 输入 | 触发器2 数据输入 K。功能同 1K (引脚2),作用于第二个触发器。 |

| 15 | 2CLR | 输入 | 触发器2 异步清零 (CLEAR)。低电平有效。功能同 1CLR (引脚1),作用于第二个触发器。 |

| 16 | Vcc | 电源 | 正电源电压 (+5V)。 |

功能表

以下是单个触发器的功能表 (PRESET 和 CLEAR 低电平有效, ^ 表示下降沿, X 表示任意状态 - 高或低电平均可, Qn 表示当前状态, Qn+1 表示时钟下降沿后的状态):

| PR (异步置位) | CLR (异步清零) | CP (时钟) | J | K | Qn+1 (次态) | Q非n+1 (次态) | 工作模式 |

|---|---|---|---|---|---|---|---|

| L (0) | H (1) | X | X | X | H (1) | L (0) | 异步置位 (Set):强置 Q=1 |

| H (1) | L (0) | X | X | X | L (0) | H (1) | 异步清零 (Clear/Reset):强置 Q=0 |

| L (0) | L (0) | X | X | X | H (1) | H (1)⁺ | 无效状态 (Invalid):Q和Q非同时为高,避免使用! |

| H (1) | H (1) | ↓ ^ | L | L | Qn | Q非n | 保持 (Hold):状态不变 |

| H (1) | H (1) | ↓ ^ | L | H | L (0) | H (1) | 清零 (Reset):置 Q=0 |

| H (1) | H (1) | ↓ ^ | H | L | H (1) | L (0) | 置位 (Set):置 Q=1 |

| H (1) | H (1) | ↓ ^ | H | H | Q非n | Qn | 翻转 (Toggle):状态取反 (计数) |

重要说明:

- 异步优先:

PRESET (PR)和CLEAR (CLR)是 异步 控制输入。当它们有效时(低电平),立即且独立于时钟 (CP) 和 数据输入 (J, K) 地改变触发器的输出状态。只有当PR = H (1)且CLR = H (1)时,触发器才会在时钟CP的 下降沿 根据当前的J和K输入状态更新其状态(即执行功能表下半部分的逻辑)。 - 同步操作: 表的后4行描述了在

PR = H且CLR = H时,时钟下降沿 (↓) 根据J/K输入进行的 同步 操作。 - 避免无效状态: 绝对不要同时将

PR和CLR都置为低电平 (L),这将导致Q和Q非同时为高电平 (H),这是一个 不稳定且违反逻辑 的状态,可能损坏芯片或导致不可预测的行为。 - 触发时刻: 状态变化仅发生在时钟信号的 下降沿(从高到低的瞬间)。

功能简述

- 强制设置 (Set):

PR= 低 (0),CLR= 高 (1) -> 强制Q = 1,Q非 = 0(立即生效,无视时钟)。 - 强制清零 (Reset):

PR= 高 (1),CLR= 低 (0) -> 强制Q = 0,Q非 = 1(立即生效,无视时钟)。 - 保持 (Hold):

PR= 高 (1),CLR= 高 (1), 时钟下降沿时J = K = 0-> 输出保持原状态不变 (Qn+1 = Qn)。 - 清零 (Reset):

PR= 高 (1),CLR= 高 (1), 时钟下降沿时J = 0,K = 1-> 输出Qn+1 = 0,Q非n+1 = 1。 - 置位 (Set):

PR= 高 (1),CLR= 高 (1), 时钟下降沿时J = 1,K = 0-> 输出Qn+1 = 1,Q非n+1 = 0。 - 翻转/计数 (Toggle):

PR= 高 (1),CLR= 高 (1), 时钟下降沿时J = 1,K = 1-> 输出状态翻转 (Qn+1 = Q非n)。这是构成计数器的基础。

希望这份详细的中文说明能帮助你理解和使用 74LS112 芯片!

74ls160引脚图及功能真值表介绍

74ls160引脚图管脚图及功能真值表,74ls160引脚图管脚图74LS160的功能真值表-综合电路图 74ls160引脚图管脚图 74LS160的功能真值表

2022-05-25 16:39:14

74ls161引脚图及功能介绍

74ls161引脚图及功能。 74ls161引脚图: 74ls161功能: 从功能表中能够知道,如果清零端CR=“0”时,计数器输出Q3、Q2、Q1、Q0都会马上为全“0”,这个时候是异步复位功能。当CR=“1

2021-07-08 15:40:22

74ls163引脚图及功能表

74LS163是4位二进制同步计数器,它具有同步清零、同步置数的功能,它可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能。 74LS163引脚图: 74LS163引脚图

2021-07-08 16:00:13

74ls32引脚图及功能表

,6--2Y;7--GND; 右起:右上8--3Y,9--3A,10--3B;11--4Y,12--4A,13--4B;14--VCC 其中A,B为输入端,Y为输出端,GND为电源负极,VCC为电源正极。 74LS32引脚图: 74LS32功能表: 文章综合来源:51hei 编辑:ymf

2021-07-08 11:22:59

74ls153引脚功能图

双4选1数据选择器74LS153 所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。引脚图排列如图1,功能如表1。 表1 74LS153功能表 图1 74LS153引脚功能图

2021-06-30 11:34:40

74ls147的引脚和功能图

74ls147引脚图管脚图和功能真值表优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最的输入信号进行编码。 常用的集成优先编码器IC有10 线-4线、8线-3线两种。10线

2021-06-30 14:46:01

74ls161商品批发价格 74ls161引脚图与管脚功能测试

clk,这是时钟。 74ls161引脚图介绍: 时钟CP和四个数据输入端P0-P3 清零/MR 使能CEP,CET 置数PE 数据输出端Q0-Q3 以及进位输出TC.(TC=Q0.Q2.Q3.CET

2021-06-08 10:45:41

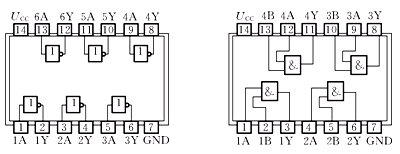

74ls00引脚图资料及功能电路图

74ls00为四组2输入端与非门(正逻辑),他的作用很简单顾名思义就是实现 一个与非门。下面来看看74ls00的引脚图资料及功能电路图。

2022-11-12 09:21:02

74ls20引脚图及引脚图解

、低电平输出电流: 0.4 mA、传播延迟时间:22 ns、电源电压-最大: 5.25 V、电源电压-最小: 4.75 V、封装: PDIP-14、引脚数14。74LS20系列拥有4组2输入端与非门

2021-06-21 11:55:15

74ls32引脚图及功能表

74LS32系列包含四个独立的2输入或门,SN5432, SN54LS32和SN54932的特点是在整个军事范围内工作-550℃到125℃。SN7432、SN74LS32和SN74S32的特点是适用于0°C~70℃的工作环境。

2021-07-06 16:55:53

集成芯片74ls00引脚功能

集成芯片74LS00是一款四组2输入与非门(NAND)集成电路,具有高速、低功耗、高可靠性的特点,在数字电路设计中得到了广泛的应用。下面,我们将详细解析74LS00集成芯片的引脚功能。

2024-03-20 15:37:32

74ls373引脚图及功能 74ls373是什么芯片

74LS373是带三态缓冲输出的8D锁存器,常被应用在单片机系统中。分为54S373和74LS373两个线路,74LS373输出端Q0-Q7可直接与总线相连接。

2021-07-08 10:07:10

74hc595引脚图及功能表

3个io就可以控制8个数码管的引脚,他还具有一定的驱动能力,可以免掉三极管等放大电路,所以这块芯片是驱动数码管的神器.应用非常广泛。 74HC595引脚图及功能表: 74HC595引脚

2021-07-01 10:10:29

74ls04引脚图及功能

74LS04是一个数字,控制开关芯片简单来说里面就是几个电子开关电路由外部信号控制内部开关状态,在节日彩灯中起控制彩灯按设的顺序亮和灭的作用。

2021-06-29 14:45:58

74ls08 74ls08引脚图及功能

74LS08是74XXYY系列集成电路芯片之一,有四个AND门,每个门带有两个输入,是2输入四正与门集成电路芯片,常被应用在各种功能的数字电路系统中。

2021-07-07 11:24:35

sp3232引脚及功能

的功能。 Vcc1和Vcc2引脚:这两个引脚用于供电,通常使用+3.3V或+5V电源。 RIN1和ROUT1引脚:这两个引脚用于接收和发送串行数据信号。RIN1引脚是接收器的输入引脚,接收来自外部设备的数据;ROUT1引脚是驱动器的输出引脚,用于发送数据给外部设备。 ROUT1和RIN1引脚:这两个

2023-12-19 09:39:30

74LS273引脚图和工作原理

74LS273是8位数据/地址锁存器,它是一种带清除功能的8D触发器,D0~D7为数据输入端,Q0~Q7为数据输出端,正脉冲触发,低电平清除,常用作数据锁存器,地址锁存器。

2020-08-10 17:39:26

74ls193引脚图及功能表

74LS193芯片是同步四位二进制可逆计数器,它具有双时钟输入,并具有异步清零和异步置数等功能。 74ls193计数器工作原理: 193为可预置的十进制同步加/减计数器,共有54193

2021-07-09 10:30:39

非门74ls04引脚图

74ls04是带有6个非门的芯片,就是有6个反相器,它的输出信号与输入信号是完全相反的。六个反相器。共用电源端和接地端,其它都是独立的。输出信号手动负载的能力也有一定程度的放大。 74LS04的作用

2021-07-08 09:03:12

关于sn74ls14d原理图的画法

不太懂这个sn74ls14d为啥要画成这个样子,跟网上搜到的不一样,我想生成pcb的时候是不是还要在原理图上把这个器件换成14引脚封装的图??

![]() 423uhih

2019-05-20 12:50:06

423uhih

2019-05-20 12:50:06

74LS248引脚图及功能表

74LS248是一款四线-7段BCD共阴极译码驱动器,经常被用于LED数码管显示驱动的集成电路芯片,有54/74248和54/74LS248两种线路结构型式。

2021-07-10 11:49:25